# THALES ALENIA SPACE IN ITALY EXPERIENCE WITH GR740

### GR740 USER DAY - ESA-ESTEC - 28<sup>TH</sup> NOV. 2019

G. Aranci, D. Andreetti

Date:

28/11/2019

/// 1

Ref:

GR740 User Day ESA-ESTEC

Template:

83230347-DOC-TAS-EN-008

#### PROPRIETARY INFORMATION

This document is not to be reproduced, modified, adapted, published, translated in any material form in whole or in part nor disclosed to any third party without the prior written permission of Thales Alenia Space. © 2019 Thales Alenia Space

# **TABLE OF CONTENTS**

## Date: 28/11/2019 /// 2 Ref: GR740 User Day ESA-ESTEC Template: 83230347-DOC-TAS-EN-008

### PROPRIETARY INFORMATION

This document is not to be reproduced, modified, adapted, published, translated in any material form in whole or in part nor disclosed to any third party without the prior written permission of Thales Alenia Space. © 2019 Thales Alenia Space

# INTRODUCTION AND HW ASPECTS

### COMPETENCE CENTER ELECTRONICS

Date:

28/11/2019

/// 3

Ref:

GR740 User Day ESA-ESTEC

Template:

83230347-DOC-TAS-EN-008

#### PROPRIETARY INFORMATION

This document is not to be reproduced, modified, adapted, published, translated in any material form in whole or in part nor disclosed to any third party without the prior written permission of Thales Alenia Space. © 2019 Thales Alenia Space

## **INTRODUCTION – WHY GR740 in the OBC Next Gen Roadmap?**

/// Thales Alenia Space in Italy decided to adopt the NGMP as core of the Platform OBC Product since 2013

/// This was considered as the "natural" evolution in the Platform OBC roadmap based on ESA supported processors

2010

LEONARDO-3G SPARC-V8 Leon3FT EPICA-NEXT SoC 80DMIPS 75 satellite in orbit ESA programs: Sentinel-1C&D **IPAC**

2018

SPARC-V8 Quad-Core Leon4FT GR740 SoC 1700 DMIPS Including GNSS RX

SPARC-V7 ERC32 TSC-695F 20DMIPS

62 satellite in orbit

### ESA programs: CryoSat-2, GOCE, SWARM, Sentinel-1A&B

Date: 28/11/2019

LEONARDÓ

2000

/// 4

Ref: GR740 User Day ESA-ESTEC Template: 83230347-DOC-TAS-EN-008 PROPRIETARY INFORMATION

This document is not to be reproduced, modified, adapted, published, translated in any material form in whole or in part nor disclosed to any third party without the prior written permission of Thales Alenia Space. © 2019 Thales Alenia Space

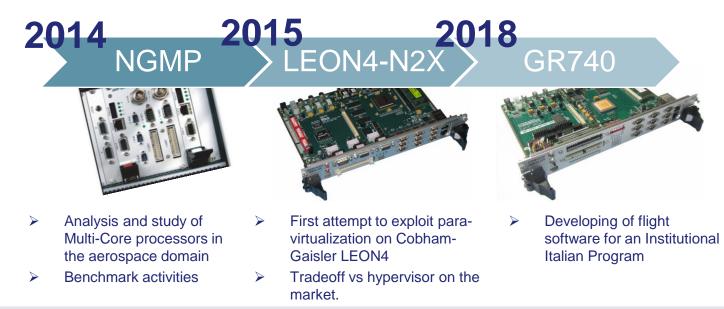

## CRONOLOGY 1/3

///In 2010 TAS-in-Italy started the definition of a new generation of avionics computer based on multi-core processor in the frame of Italian National programs and internal R&D, in order to integrate several processing tasks previously distributed among many computers around the satellite (e.g. Star Tracker processing, GNSS Navigation processing, AOCS Data Fusion) with benefit in term of avionics platform competitiveness

///In 2013 the ESA NGMP (Next Generation Microprocessor) has been selected by TASin-I as major building block for the new computer generation family

///May 2013: preliminary draft datasheet of LEON4-NGMP available

///A trade off was activated in order to compare a solution based on the GR740 SoC from Cobham-Gaisler or on a custom FPGA solution based on use of NGMP IP Core. The final **solution based on GR740 was in the end selected mid 2016**, and detailed board design started.

///Adopted board name is Multi-Core Processor Module (MCPM)

#### PROPRIETARY INFORMATION

This document is not to be reproduced, modified, adapted, published, translated in any material form in whole or in part nor disclosed to any third party without the prior written permission of Thales Alenia Space. © 2019 Thales Alenia Space

## , CRONOLOGY 2/3

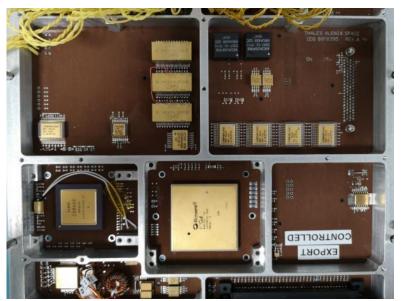

///First MCPM based on GR740 has been designed by TAS-in-Italy Competence Center Electronics in **2016** targeted to Platform On-Board Computer with HIREL EEE components

### ///TAS-in-Italy GR740 HI-REL board assembled and tested mid 2017

### PROPRIETARY INFORMATION

This document is not to be reproduced, modified, adapted, published, translated in any material form in whole or in part nor disclosed to any third party without the prior written permission of Thales Alenia Space. © 2019 Thales Alenia Space

THALES ALENIA SPACE INTERNAL

6 Ref: GR740 User Day ESA-ESTEC Template: 83230347-DOC-TAS-EN-008

## , CRONOLOGY 3/3

///A new version "COTS" of the board has been developed in 2017/18, targeted to low cost missions

///TAS-in-Italy GR740 COTS board assembled and tested early 2018

### PROPRIETARY INFORMATION

This document is not to be reproduced, modified, adapted, published, translated in any material form in whole or in part nor disclosed to any third party without the prior written permission of Thales Alenia Space. © 2019 Thales Alenia Space

THALES ALENIA SPACE INTERNAL

7 Ref: GR740 User Day ESA-ESTEC Template: 83230347-DOC-TAS-EN-008

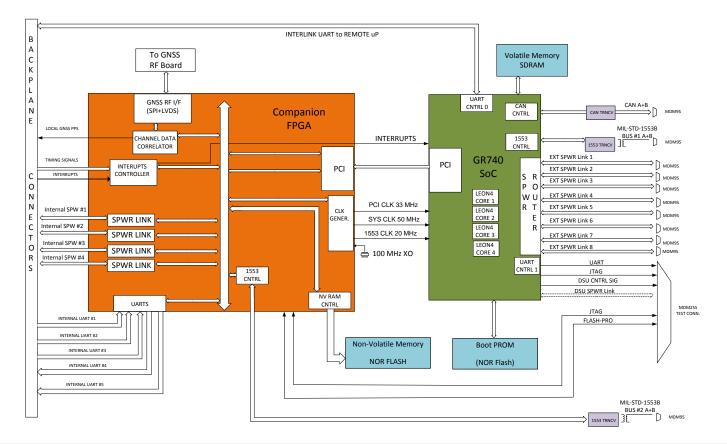

## **MCPM BOARD CHARACTERISTICS**

///MCPM is targeted to Platform Avionics Computer functions. According to some limitations imposed by GR740 (not all the SoC functions can be used due to Pin Multiplexing), it has been necessary to help the SoC with an additional companion reprogrammable FPGA (allowing flexibility and configurability).

### ///GR740 provided interfaces:

- 8 SPW links (from GR740 router to external users)

- I 1 PCI (bridge to companion FPGA)

- 1 MIL-STD-1553B Bus

- 2 CAN Bus

- 2 UART

/// 8

JTAG, DSU SPW

### ///Companion FPGA provided Interfaces:

Interface to non-volatile large memory (NOR FLASH)

Clocks generation & Timings management

GR740 reset and additional Interrupt Controller

4 SPW links (for high rate TM/TC/RM internal connection)

5 serial link (for low rate TM/TC/RM internal connection)

Interface to GNSS RF and GNSS Receiver correlators

Second MIL-STD-1553B Bus

### ///MCPM implements following memory budget:

- 64kbyte Non-Volatile Boot Memory (maximum allowed due to GR740 Pin Multiplexing limitation)

- 32Mbyte Non-Volatile Memory (supported by Companion FPGA)

- 512Mbyte Volatile SDRAM (128MByte in COTS version)

Date: 28/11/2019

Ref: GR740 User Day ESA-ESTEC Template: 83230347-DOC-TAS-EN-008

### PROPRIETARY INFORMATION

This document is not to be reproduced, modified, adapted, published, translated in any material form in whole or in part nor disclosed to any third party without the prior written permission of Thales Alenia Space. © 2019 Thales Alenia Space

## , MCPM BOARD BLOCK DIAGRAM

#### PROPRIETARY INFORMATION

This document is not to be reproduced, modified, adapted, published, translated in any material form in whole or in part nor disclosed to any third party without the prior written permission of Thales Alenia Space. © 2019 Thales Alenia Space

THALES ALENIA SPACE INTERNAL

ThalesAlenia

Date:

28/11/2019

/// 9

Ref:

GR740 User Day ESA-ESTEC

Template:

83230347-DOC-TAS-EN-008

# PLATFORM/SYSTEM ASPECTS

**COMPETENCE CENTER PLATFORM & INTEGRATION**

Date:

28/11/2019

///

10

Ref:

GR740 User Day ESA-ESTEC

Template:

83230347-DOC-TAS-EN-008

#### PROPRIETARY INFORMATION

This document is not to be reproduced, modified, adapted, published, translated in any material form in whole or in part nor disclosed to any third party without the prior written permission of Thales Alenia Space. © 2019 Thales Alenia Space

## **ROAD TO «MULTICORE SYSTEM»**

**EMC<sup>2</sup> -** Embedded Multi-Core systems for Mixed Criticality applications (ARTEMIS Joint Undertaking project)

The **objective** of EMC<sup>2</sup> is to establish Multi-Core technology in all relevant Embedded Systems domains

#### PROPRIETARY INFORMATION

28/11/2019

GR740 User Day Day ESTEC

Ref:

Template: 83230347-DOC-TAS-EN-008

This document is not to be reproduced, modified, adapted, published, translated in any material form in whole or in part nor disclosed to any third party without the prior written permission of Thales Alenia Space. © 2019 Thales Alenia Space

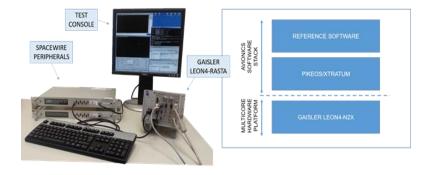

## SPACECRAFT PLATFORM COMPUTER

TAS-in-Italy has implemented a reference Spacecraft Platform based on a next-generation multicore processing architecture which supports Mixed Criticality applications.

### **OBJECTIVE**

- To evaluate multi-core platform (Cobham Gaisler LEON4) for the aerospace domain

- > To evaluate the virtualization-based software architectures (SYSGO **PikeOS** and FentISS **XtratuM**)

- > To analyse the performance of the platform with respect to real world applications

- > To evaluate the hypervisor capabilities in reusing legacy code (Star Tracker Software)

### **OVERVIEW**

- > The designed system aims to model:

- The satellite's telecommand and telemetry function.

- > The management of peripheral devices.

- > The management of mixed-criticality application.

Date:

28/11/2019

///

12

Ref:

GR740 User Day ESA-ESTEC

Template:

83230347-DOC-TAS-EN-008

#### PROPRIETARY INFORMATION

This document is not to be reproduced, modified, adapted, published, translated in any material form in whole or in part nor disclosed to any third party without the prior written permission of Thales Alenia Space. © 2019 Thales Alenia Space

## **KEY POINTS**

### **Achievements**

- Multicore processors (e.g. LEON4) provide better cost and power dissipation than single-core solutions of comparable computing power.

- The Hypervisor allows the development of Time and Space Partitioning Systems supporting mixed-criticality applications. (e.g. Symmetric Multi-Processing)

- > The **latency** introduced by the hypervisor is minimal and it doesn't forbid the execution of Avionic Applications.

- > The re-use of Legacy Code is fundamental feature of virtualization

- SYSGO PikeOS and FentISS XtratuM are interesting solution for the aerospace domain. Both hypervisors ensure time and space partitioning on multicore system with mixed criticality applications

### A little effort on...

Improvement of predictability and determinism (Both are minor w.r.t. single core processor due to contention of shared resources)

### PROPRIETARY INFORMATION

This document is not to be reproduced, modified, adapted, published, translated in any material form in whole or in part nor disclosed to any third party without the prior written permission of Thales Alenia Space. © 2019 Thales Alenia Space

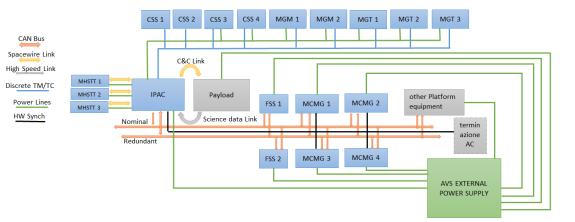

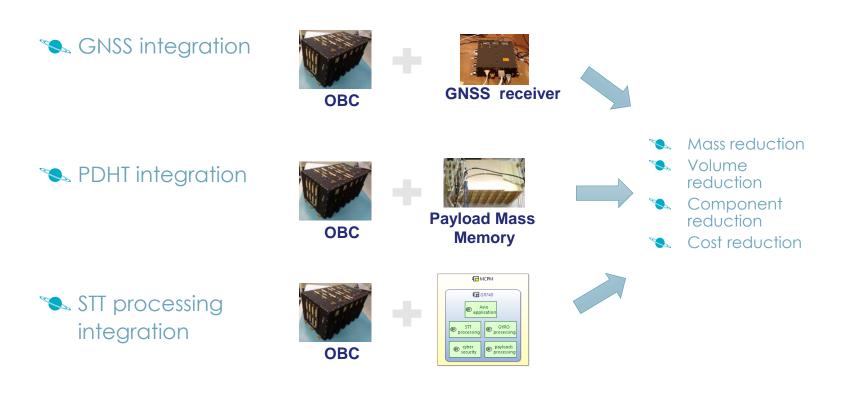

## **NEW AVIONIC ARCHITECTURE: IPAC OVERVIEW**

- /// New Avionic architecture is based on new OBC: the Integrated Processing & AOCS Controller (IPAC)

- Enhanced compactness with respect to the actual OBC

- Processor capability up to 1700 DMIPS

- Flash memory capacity (for platform and payload data storage) up to 5 Tbit

- Reduced mass thanks to the fusion of many different functions in the same board

OBC Mass: 18 Kg Power: 53 W Volume: 38 dm3

### **GNSS** Receiver Mass: 3 Kg Power: 15 W

Volume: 5.4 dm3

Mass: 16 Kg Power: 95 W Volume: 32 dm3

Date: 27/11/2019 Ref: Template: 83230347-DOC-TAS-EN-008

### PROPRIETARY INFORMATION

This document is not to be reproduced, modified, adapted, published, translated in any material form in whole or in part nor disclosed to any third party without the prior written permission of Thales Alenia Space. © 2019 Thales Alenia Space

**NEW AVIONIC ARCHITECTURE: IPAC EFFECT**

Date: 27/11/2019 Ref: Template: 83230347-DOC-TAS-EN-008

### PROPRIETARY INFORMATION

This document is not to be reproduced, modified, adapted, published, translated in any material form in whole or in part nor disclosed to any third party without the prior written permission of Thales Alenia Space. © 2019 Thales Alenia Space

# SW ASPECTS

### COMPETENCE CENTER SOFTWARE SOLUTIONS

Date:

28/11/2019

///

16

Ref:

GR740 User Day ESA-ESTEC

Template:

83230347-DOC-TAS-EN-008

### PROPRIETARY INFORMATION

This document is not to be reproduced, modified, adapted, published, translated in any material form in whole or in part nor disclosed to any third party without the prior written permission of Thales Alenia Space. © 2019 Thales Alenia Space

## **MIGRATION TOWARDS A MULTICORE ARCHITECTURE**

- Integration of multiple SW on the same multi-core processor

- Reduce HW bill of material and SW qualification effort, Increases SW complexity

- Need to manage different SW cat. level sharing the same resources

- Needs to isolate failure of less critical SW to prevent error propagation

- Time and space partitioning management

## **HYPERVISOR**

- An Hypervisor grants time and space partitioning

- At the start of our activity none hypervisor is qualified for GR740

- Open contact with vendor

- Currently we are using XtratuM by FentISS

- None formal qualification but grants compatibility for GR740

- Just qualified under ESA contract on LEON 3. Probably it will be in 2020 for multicore in GR740

- We have performed an internal validation campaign for XM4 on GR740.

Date:

28/11/2019

///

17

Ref:

GR740 User Day ESA-ESTEC

Template:

83230347-DOC-TAS-EN-008

#### PROPRIETARY INFORMATION

This document is not to be reproduced, modified, adapted, published, translated in any material form in whole or in part nor disclosed to any third party without the prior written permission of Thales Alenia Space. © 2019 Thales Alenia Space

## SW DEVELOPMENT FOR GR740 BASED ON BOARD COMPUTER

### SW Development for OnBoard Computer

- Dedicated HW aspect can't be managed until OBC availability

- The use of a GR740 development board can't be enough for some aspect

## FULL SW SIMULATOR

- A completely SW simulator permits to develop SW without HW availability

- GR740 emulator are currently in beta version

- Open contact with vendor

- At this time there isn't a GR740 emulator

Date:

28/11/2019

///

18

Ref:

GR740 User Day ESA-ESTEC

Template:

83230347-DOC-TAS-EN-008

### PROPRIETARY INFORMATION

This document is not to be reproduced, modified, adapted, published, translated in any material form in whole or in part nor disclosed to any third party without the prior written permission of Thales Alenia Space. © 2019 Thales Alenia Space

# **RETURN OF EXPERIENCE**

Date:

28/11/2019

///

19

Ref:

GR740 User Day ESA-ESTEC

Template:

83230347-DOC-TAS-EN-008

#### PROPRIETARY INFORMATION

This document is not to be reproduced, modified, adapted, published, translated in any material form in whole or in part nor disclosed to any third party without the prior written permission of Thales Alenia Space. © 2019 Thales Alenia Space

## **POSITIVE FEEDBACK**

## • Map of memory suitable for SW implementations

- all registers of each function are grouped to a block aligned to 4KB. This allow an easy segregation of memory using MMU (that works on a minimum amount of memory (page) that is exactly 4KB)

- Cache system with the L2

- Controllers of peripherals

- suitable in exchange data, using DMA bursts to access SDRAM. Improvement of functionality (for example the CAN controller, with its buffering potentiality, is better respect the one on UT699)

- Powerful HW utility

- one for all, scrubbing of SDRAM

- IOMMU also allows spatial segregation also in presence of DMA peripherals.

Date:

28/11/2019

/// 20

Ref:

GR740 User Day ESA-ESTEC

Template:

83230347-DOC-TAS-EN-008

#### PROPRIETARY INFORMATION

This document is not to be reproduced, modified, adapted, published, translated in any material form in whole or in part nor disclosed to any third party without the prior written permission of Thales Alenia Space. © 2019 Thales Alenia Space

## **IMPROVEMENTS AREAS AND SUGGESTIONS 1/2**

## • Multiplexing of signals

- The PROM lines are multiplexed with standard avionics resources such CAN, MIL-STD-1553, UART → this penalized specifically the Platform Computer application scenario where large Non-Volatile memory and standard avionics interfaces are requested at the same time. This imposes additional companion FPGA.

- multiplexing of interrupt inputs

## Only one MIL-STD1553B bus

Many applications (also several ESA missions) require the presence of two MIL-BUS-1553 busses

## SDRAM Controller

• SDRAM are obsolete → difficult to guarantee manufacturability of equipment based on GR740 for more than 5/6 years and imposes the maintenance of compatible SDRAM part stock

### PROPRIETARY INFORMATION

This document is not to be reproduced, modified, adapted, published, translated in any material form in whole or in part nor disclosed to any third party without the prior written permission of Thales Alenia Space. © 2019 Thales Alenia Space

## **IMPROVEMENTS AREAS AND SUGGESTIONS 2/2**

## Interrupt controller

- •most of the interrupt of first level are dedicated to timers.

- •Only one interrupt is the collector of other 16 interrupts coming from peripheral.

- •No «first level» interrupt for external signal GPIO (the only GPIO are «second level» interrupt but anyway multiplexed).

- •4 «first level» interrupt unassigned.

- This create a «bottle neck» for redistribute interrupt toward different applications.

## PCI DMA engine

•only 1 PCI DMA engine present (GRPCI2) → One per core could be a better solution to extend the potentiality of this bus to all applications running on different cores

### PROPRIETARY INFORMATION

This document is not to be reproduced, modified, adapted, published, translated in any material form in whole or in part nor disclosed to any third party without the prior written permission of Thales Alenia Space. © 2019 Thales Alenia Space