# 32 bit Embedded Real-time computing Core Single Chip Development (ERC32SC/TSC695)

Contract 12598/FM (SC)

T. Corbiere, J. Tellier, C. LeGargasson, B. Mouchel, S. Vandepeute, ATMEL WM, France A. Pouponnot, J. Gailser, ESTEC, Netherlands

# **Agenda**

- Objectives of the contract

- Tentative specification

- Added / Removed functionality

- Electrical characterization

- Radiation test results

- Evaluation Board

- On Chip Debugger

- Part numbering

- Conclusions

- References

# **Program objectives**

- 18 months overall program

- Monolithic version of the existing ERC32 chip set

- Identical set of net-lists with minimum changes

- Upward software functionality

- Improved functionality, speed, radiation hardness, "user friendly"

- 5V and 3V tolerant functionality

- Basic "foundry" functional validation

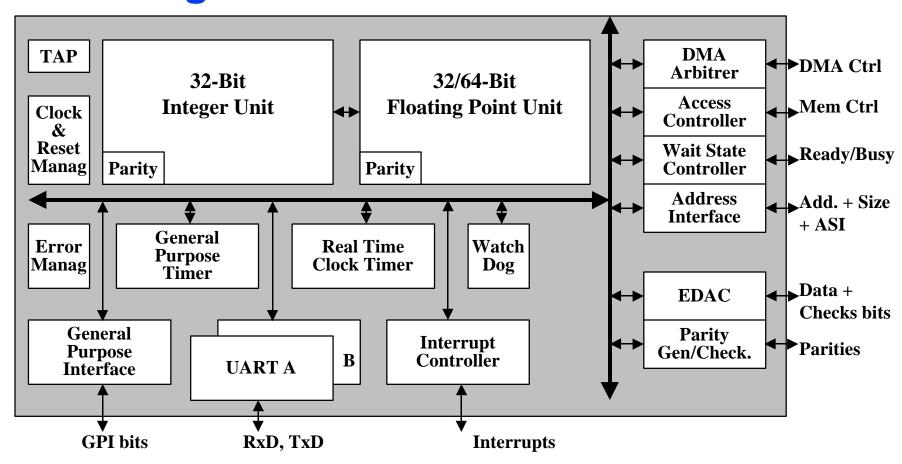

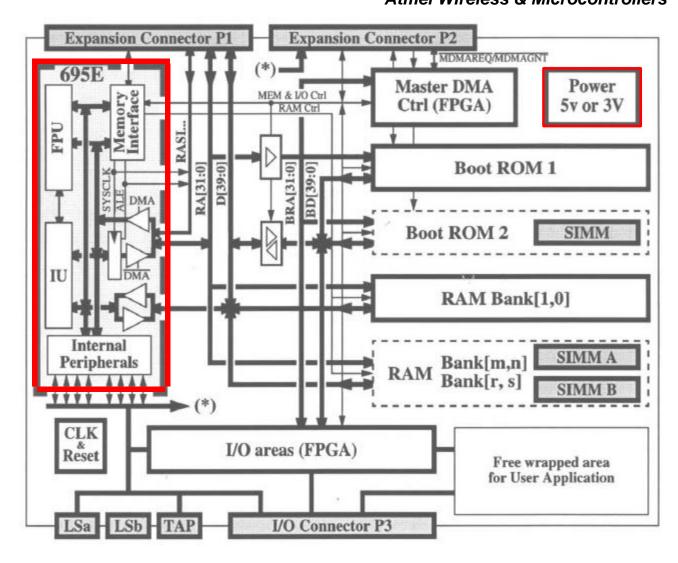

#### **Block Diagram**

#### **New Features**

- General Purpose Interface (µcontr. Functions)

- ✓ 8-bit parallel I/O port bit per bit configurable

- ✓ Edge detection on GPI inputs => External interrupt

- FLASH compatibility

- Selectable NMI or Watchdog

- High Drive Capability

- ✓ Up to 400 pF for Address buffers

- Address latches included

- ✓ Up to 150 pF for Data, Controls & Clock buffers

- On-Chip Debugger for JTAG Emulator with Read/Write access for all Registers and I/Os

# No longer supported

- Master/checker mode (Never used by customers)

- Program flow control (Not supported by compilers)

- 601/602 modes (Internal parities always checking)

- Coprocessor capability (Never used, embedded processor)

# **Contractual specification**

|                  | Power supply (V) | Speed<br>(MHz) | MIPS | Power (W) |

|------------------|------------------|----------------|------|-----------|

| Committed        | $5.00 \pm 10\%$  | 20             | 14   | < 1.5     |

| ATMEL objectives |                  | 35             | 25   | <1.5      |

| Committed        | $3.00 \pm 10\%$  | 12             | 8    | < 0.4     |

| ATMEL            |                  | 20             | 14   | < 1.0     |

| objectives       |                  |                |      |           |

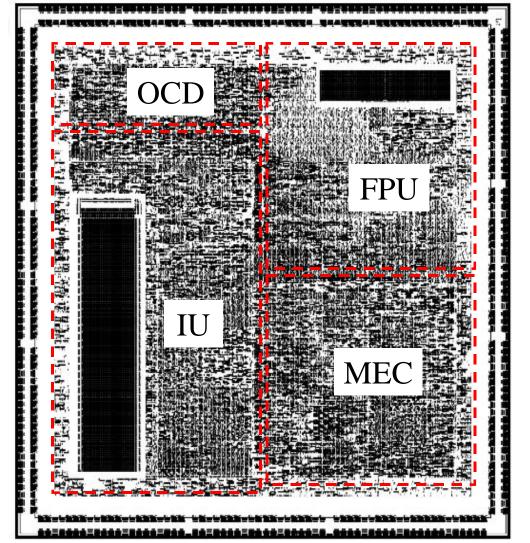

#### **ERC32 Single Chip development**

#### Atmel Wireless & Microcontrollers

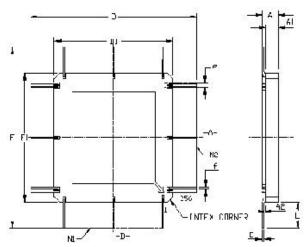

256 LEAD MQFP\_F

|     | l mm   |        | mil;   | 5      |

|-----|--------|--------|--------|--------|

|     | И г    | Max    | Min    | Max    |

| A   | 2, 41  | 0,18   | . 095  | .125   |

| С   | 0.10   | 0, 20  | . 004  | , 00€  |

| D   | 50 23  | 55, 74 | 2, 005 | 2,105  |

| D1  | 36 83  | 37, 34 | 1, 450 | J. 470 |

| E   | 59 23  | 55, 74 | 2, 095 | 2, 190 |

| E1  | 36 83  | 37, 34 | 1. 450 | 1, 470 |

| 6   | 0, 508 | 8 B3C  | . 020  | BSC    |

| f   | 0.15   | 0, 25  | .(06   | 7010   |

| A1  | 2, 3€  | 2, 56  | .(8_   | 51     |

| AC  | 0.00   | 0, 36  | 500.   | . 014  |

| L   | 8 20   | 5, 20  | , 323  | , 366  |

| N.I | 6-     | 4      | €4     | 1      |

| NZ  | 6-     | 4      | t-     | 1      |

#### **Functional Validation**

- Validation plan rev 1.0 Feb 1999

- Current status:

| Bloc                        | Status | Comment |

|-----------------------------|--------|---------|

| System startup control      | Done   | OK      |

| Integer Unit                | Done   | OK      |

| Floating Point Unit         | Done   | OK      |

| Access controller           | Done   | OK      |

| Timers                      | Done   | OK      |

| UARTs                       | Done   | OK      |

| Wait-states and Time-out    | Done   | OK      |

| Interrupt Ctrl              | Done   | OK      |

| General Purpose Interface   | Done   | OK      |

| EDAC / Parity               | Done   | OK      |

| <b>Direct Memory Access</b> | Done   | OK      |

| Test Access Port            | Done   | OK      |

#### **Electrical Characterization**

- Covers from 2.7V up to 6.0V, from -55 $^{\circ}$ C to +125 $^{\circ}$ C

- Functional verification (all patterns at V and Temp)

- Dynamic/static measurements (example given for initial rev.)

| Timing | Worst case           | Comment for 30MHz speed            |

|--------|----------------------|------------------------------------|

|        | ( <b>5.0V</b> range) |                                    |

| t5     | 10.8 nS              | Critical / to improve              |

| t8     | 35.6 nS              | Critical / to improve              |

| t9_D   | 16.5 nS              | Critical / to improve              |

| t13    | 18.3 nS              | Critical / few nS to get           |

| t15    | 35.6 nS              | Critical / to improve              |

| t7     | 33.0 nS              | OK. No change requested            |

| t9_CB  | 7.6 nS               | OK. No change requested            |

| t12    | 20.2 nS              | OK. No change requested            |

| t14    | 12.0 nS              | Spec. to be changed                |

| t57    | 13.7 nS              | Change to t15 will make t57 better |

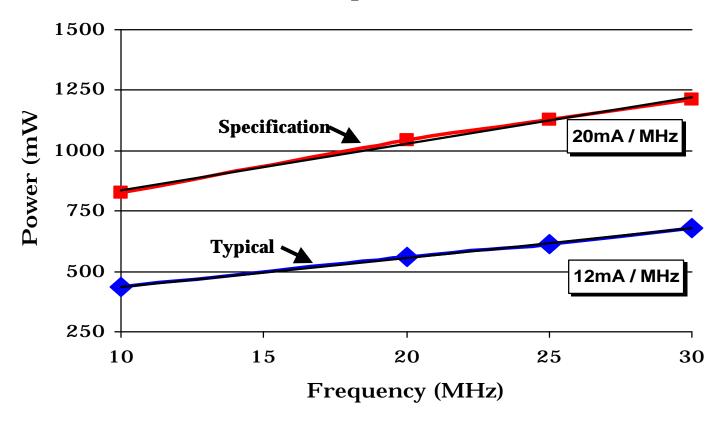

#### **Power**

#### Dissipation

#### ERC32 Single Chip development

Atmel Wireless & Microcontrollers

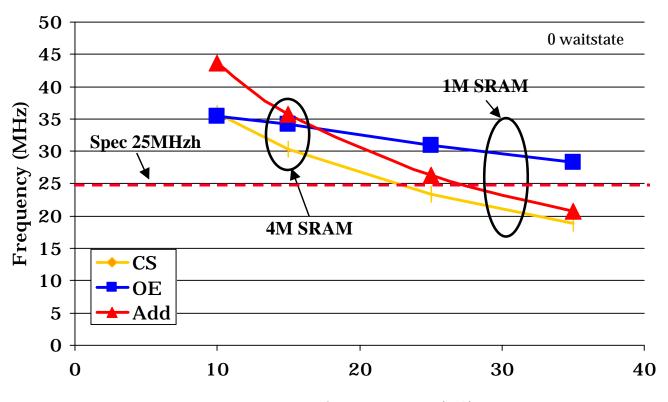

# **Speed**

#### Frequency

Memory Access time (nS)

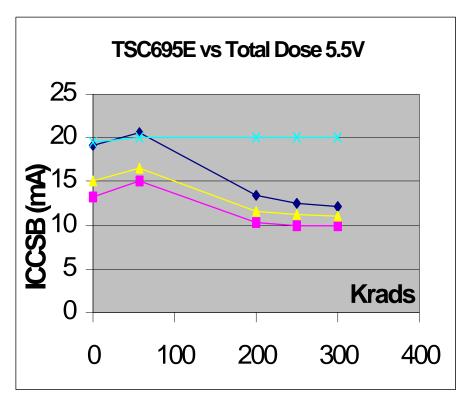

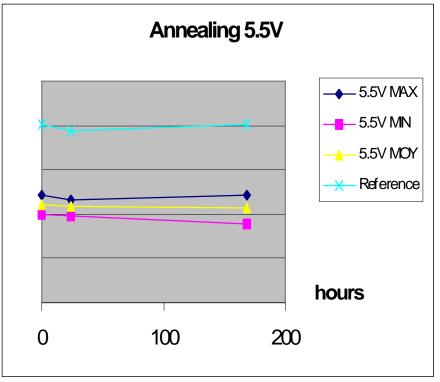

#### **Tolerance to Total Dose**

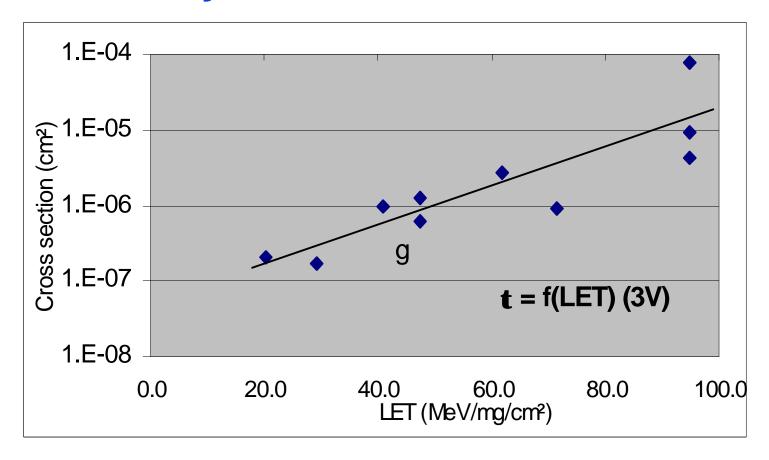

### **Heavy ions test results**

- 2 parts @ 4.5V & 2 parts @ 2.7V

- Test at Berkeley, CA

- eVAB-695, evaluation board used

- LATCH-UP detection

- ✓ by external current threshold

- ✓ In case of functional failure, no POWER-DOWN to not remove possible permanent LATCH-UP

- UPSET detection

- **✓** By means of similar to what was used during the ERC chip set test

- **✓** Internal registers then PARANOIA tests

- **✓** Test status reporting via UART to monitor

- **✓** In case of functional crash, RESET is sent to the eVAB-695.

#### Response to Heavy ions

| Voltage    | LET Threshold             | <b>Cross Section</b> | Comments                    |

|------------|---------------------------|----------------------|-----------------------------|

| <b>(V)</b> | (MeV/mg/cm <sup>2</sup> ) | (cm <sup>2</sup> )   |                             |

| 4.5        | > 109.7                   | < 2.0E-07            | No Upset. No event in space |

| 2.7        | 20                        | 2.2E-07              | Functional (*)              |

|            |                           |                      | 3.3E-7 Error/device/day     |

(\*) The board used for test is not equipped with 3V tolerant products. Results assume errors are generated by the TSC695

# SEU sensitivity @ 2.70V

#### **New revisions**

- Improved memory interface / signals

- Corrected internal parity generation & checks

- Minor timing improvements

- Same die from 2.7V to 5.5V, Mil temp.

- Speed: 25MHz @ 5V ±10%

- 0.9W typ. @ 25MHz & 5.0V

- One single package: 256-pins MQFP (>70% space saved)

- Internal qualification pronounced as early as September 1999

- Changed to Rev.F to correct internal parity check deviations

- Space evaluation started (CNES contract)

#### JTAG On-Chip Debugger Features

- Reset / Run / Stop

- Breakpoints

- **✓** 3 hardware breakpoints for program execution

- **✓** 1 hardware breakpoint data memory access

- √ 'n 'software breakpoints using trap patch mechanism

- Step-in, Step-out, Step-over

- **✓** Assembly level

- **✓** High language Level

- Examination and Modification of Registers, Memory or I/O's

- Code Download, Inline Assembly for Local Patches

#### **Development tools**

- Ada Cross compiler system

- Hard real-time tools, target simulator

- JTAG based TSC695 target emulator (\*)

- VxWorks real-time operating system

- Rational/Verdix ADA cross-compiler Corp.

- RTEMS real-time kernel

- ADA95/C/C++ cross compiler system, simulator

- TLA 700 Logic analyser disassembler

- ADA95 compiler, based on GNAT

• ...

**Aonix**

Spacebel

**Spacebel**

Wind River Syst. Inc.

**Rational Software**

OAR

**ESA/ESTEC**

**Tektronix**

**ADA Core Technologies**

(\*) Non intrusive breakpoint detection in executed instruction

#### References

- All major European space actors

- Selected for various Space applications:

- Smart-1, Beagle 2, PHARAO, Ariane V, Radarsat, SAC-C ...

- Generic Processor Units,

- High reliability spacecraft buses,

- Star trackers

- Charge Particle Telescope (ESA experiment)

- **>** ...

- First QML-Q and QML-V parts delivered

- SMD number: 5962-00540

#### Literature

- TSC695 user's manual

- TSC695 data sheet

- eVAB695 user's manual

- TSC695E errata sheet

- at www.atmel-wm.com

#### **Part Numbers**

| <u>Part Number</u> | <u>Lead-times</u> |

|--------------------|-------------------|

|--------------------|-------------------|

TSC695F-25MA-EOn stock

TSC695F-25MA6 Weeks

TSC695F-25MA/883

22 Weeks

• 5962-0054001QXC 20 Weeks

• TSC695F-25SASB 35 Weeks

• 5962-0054001VXC 30 Weeks

TSC695-SKIT

On stock

#### ERC32 Single Chip development

Herakles

Atmel Wireless & Microcontrollers

**eVAB-695**

#### **Conclusions**

- Fast & Successful transfer of the 3 ERC32 Chip set net-lists

- Dramatically improved performances :

- Speed

- Radiation Hardness

- Power Consumption

- Space / Weight

- Additional features while overall compatibility

- Enhanced development tools :

- Support from ESTEC and European industry

- Starter kit / Development board / Compiled model for hardware simulation

- ATMEL-wm Semiconductors hot line