## RUAG Space Microprocessors in present and future equipment

Torbjörn Hult

#### **Products**

**Spacecraft Management Units**

**Guidance and Control Computers**

Payload processing and control

Radio occultation instruments

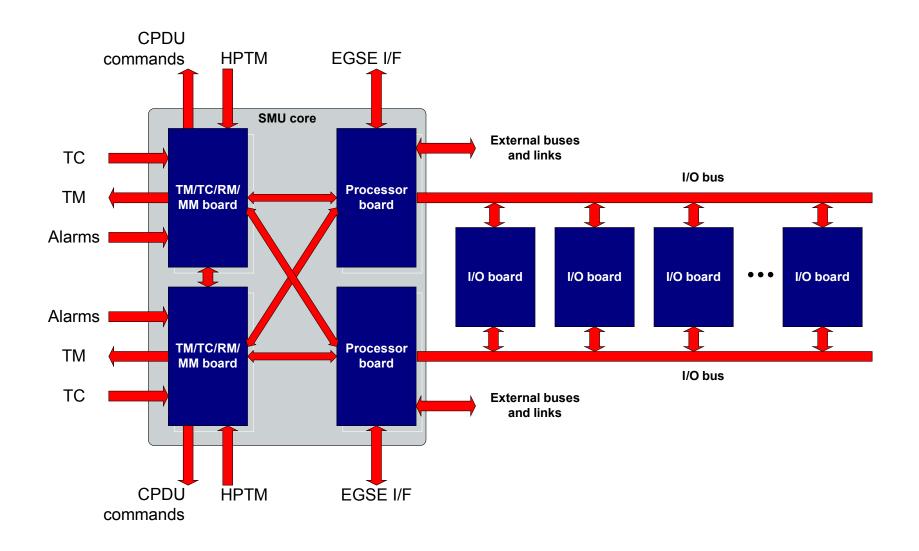

### **SMU Technical Concept**

#### **Current generation processor boards**

- Based on TSC695 including:

- COCOS ASIC

- Ext. interfaces: 2x1553, 2xSpaceWire/UART, 2xPacketWire, Sync, EGSE

- Int. interfaces: 1553, OBDH, 4xSpaceWire, 2xPacketWire Sync, Alarms

- Based on COLE ASIC including:

- 1,8V DC/DC converter

- Ext. interfaces: 2x1553, 2xSpaceWire, 2xUART, 2xCAN, Sync, EGSE

- Int. interfaces: 1553, OBDH, 5xSpaceWire, 2xPacketWire Sync, Alarms

## **COCOS, CPU Companion and I/O ASIC**

- CPU Interface

- Memory Interface

- Interrupt Controller

- Watchdog

- Alarms

- Memory Copy Controller

- On Board Time (OBT)

- 3 MIL-STD-1553B

- 1 to 3 UARTs

(pins shared with SpaceWire)

- PCI bus

- 3 Packet Wire Receiver (PWR)

- 3 Packet Wire Transmitter (PWT)

- 3 to 6 SpaceWire (pins shared with UARTs)

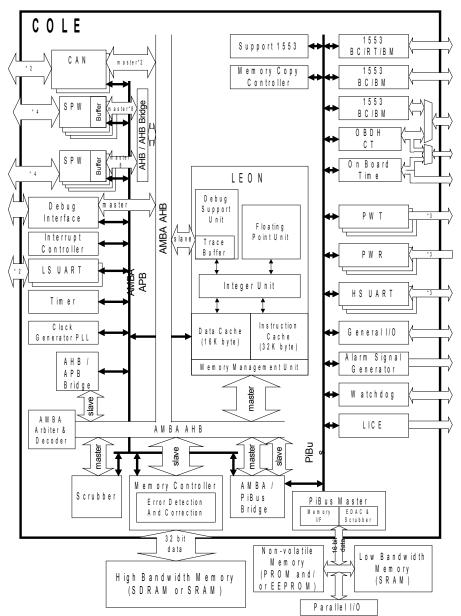

#### **COLE** chip

## RUAG

#### Integration of:

- "LEON" SPARC v. 8 processor

- COCOS I/O controller

#### Major improvements:

- Processing Performance

- I/O Speed and Functionality (MMU, enhanced DSU, SpaceWire RMAP)

- CAN bus I/O

- Cost

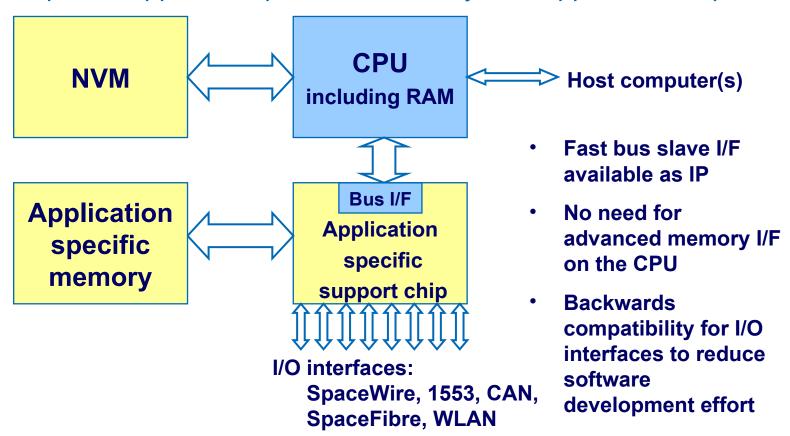

#### **Next generation computers**

- >10 years design lifetime

- Higher performance, i.e. multi-core CPU needed

- Flexible architecture to handle future requirement changes

- New standards impose upgrade of IP blocks and software

- New interfaces such as sensor buses and wireless

- Built-in GPS receiver

- Star Tracker processing in the main computer

- Time and Space Partitioning support

#### Next generation computer architecture

- Processor technology evolves faster than system architecture

- Separate application processor from system application chip

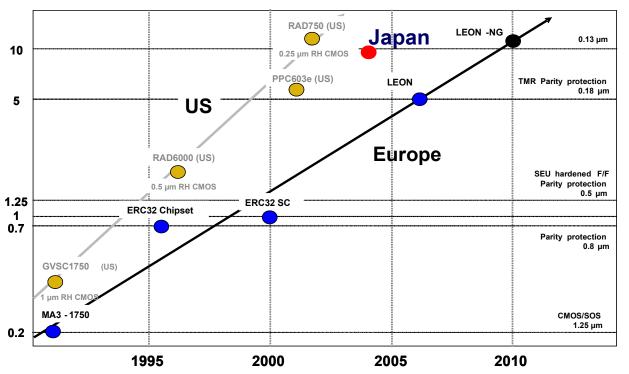

# CPU architecture considerations (from 2006 microprocessor RT)

- Performance by extrapolation:

- Are European foundries competitive?

- Does the SPARC architecture give sufficient performance?

Eurospace Oct 05

- Anything else we can do better in Europe?

- Do we have the resources to participate in the performance race?

- What will be the consequences if we do not participate?