#### **Dominique de Saint Roman**

Everywhere You Are Aerospace Product Line Marketing and Business Development Manager Everywhere You Are

Everywhere You /

Everyw

Everywhere You Are

AMEL

**Everywhere You Are**

**Everywhere You Are**

**Everywhere You Are**

**Everywhere You Are**

Everywhere You Are

Everywhere You Are®

Everywhere You Are

# AI.N. LGA625 PACKAGE DEVELOPMENT AND ESCC EVALUATION/QUALIFICATION

# **CNES contract: 04/1643/01**

ESTEC, Noordwijk, March 30th to April 1st

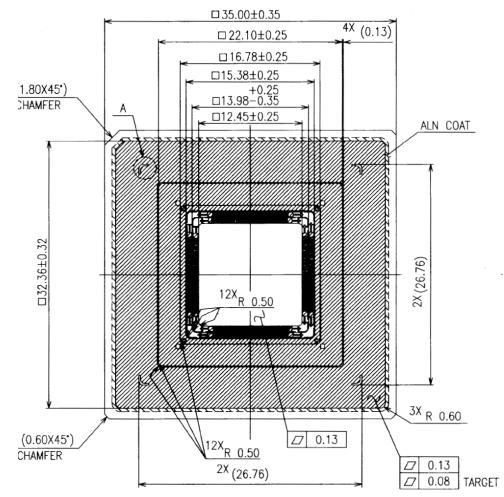

### **ALN LGA 625**

AMEL

# PACKAGE TECHNOLOGY RATIONALES

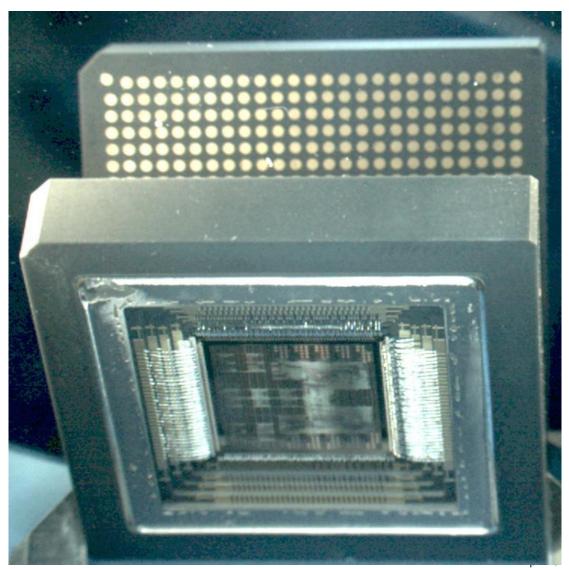

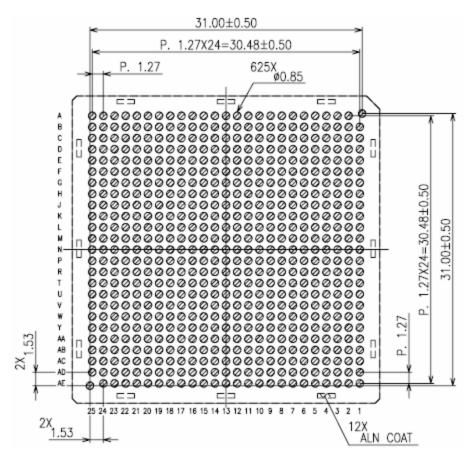

- First package of a series, w.o. rigid bond with board: <u>LGA625</u>

- 625 lands with 1.27 mm pitch and 35\*35 mm body size

- Drawback of the non-rigid bond: the power heat dissipation can no longer transfer through the columns and spread out on the board => reliability impact

#### Initially considered mitigation means

- An heat-sink on top of the package for improved dissipation

- A more thermally conductive ceramic: Al2O3 (I = 17 W/m.K) is replaced by AIN (I = 150 W/m.K) to help conduction from die to heatsink

- A larger lid seal ring area for better ceramic-lid thermal conductivity

# **DEVELOPMENT PLAN**

- Validation of the seal ring and lid option with package A

- Development and manufacturing of the B package options for the manufacturing of:

- B1: 40# with the Tyndall PMOS4 test chip and the available lands interconnected through a daisy chain scheme for board level validation by the customer

- B2: 2 batches of FM using an existing customer ASIC chip for qualification purpose without having to wait for the final ASIC design completion and manufacturing

- Development of the final package C for the end application and manufacturing of the first batch of FM to be used as a third lot for the package qualification

- 3 trial lots using all the same package:

- Trial #1: 5mm Kovar Combo lid (3#)

- Trial #2: 2mm Kovar Combo lid (3#) e2v standard

- Trial #3: 5mm AIN Combo lid same lid/preform size (2#)

TRIAL 1 RESULTS (Kovar 5mm) (1/2)

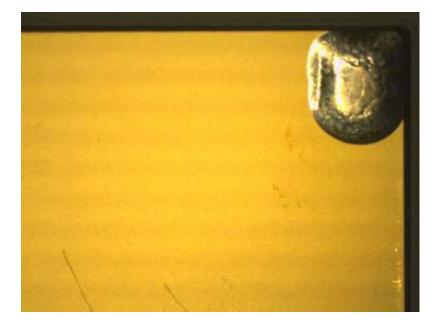

Visual inspection: Solder alloy overflow on the top of the lid

3 rejects / 3 parts

- TRIAL 1 RESULTS (Kovar 5mm) (2/2)

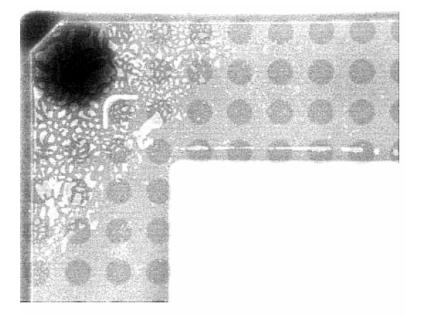

- X-rays: sealing fillet reduction by 70%

Acceptance criteria: Sealing filet width reduction < 50% 1 reject / 3 parts

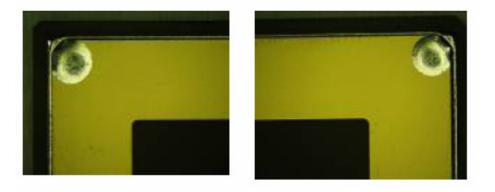

- TRIAL 2 RESULTS (Kovar 2mm) (1/2)

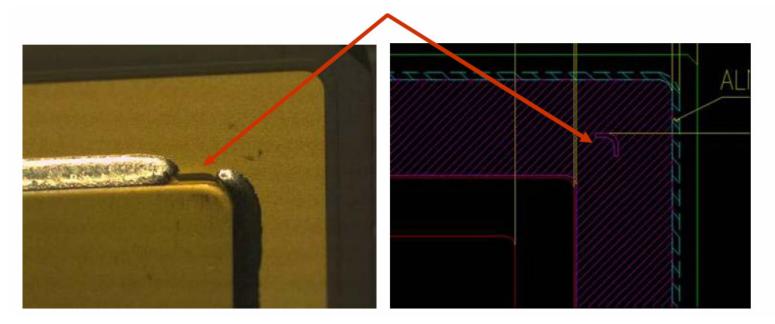

- Visual inspection: Incomplete solder fillet due to alignment mark

3 rejects / 3 parts

- TRIAL 2 RESULTS (kovar 2mm) (2/2)

- X-rays:sealing fillet reduction by 10%

Acceptance criteria: Sealing fillet width reduction < 50% 0 reject / 3 parts

- TRIAL 3 RESULTS (AIN same size lid/preform) (1/2)

- Visual inspection: solder alloy overflow on the top of the lid

2 rejects / 2 parts

TRIAL 3 RESULTS (AIN 5mm) (2/2)

• X-rays:sealing fillet reduction by 40%

Acceptance criteria: Sealing filet width reduction < 50%

0 reject / 2 parts

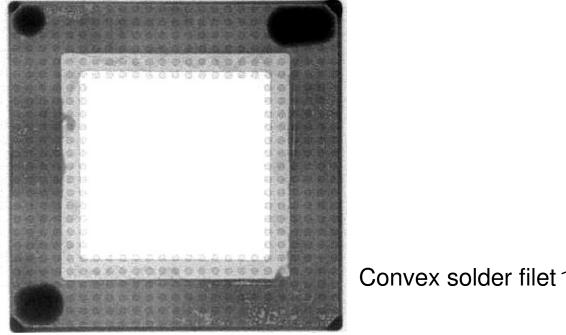

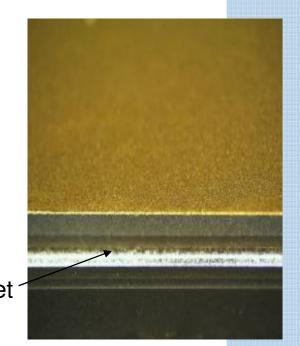

Because of the convex solder filet, a 4<sup>th</sup> trial was done for mitigating it

- TRIAL 4 RESULTS (AIN 5mm combo lid with lid smaller than preform size)

- X-rays:sealing fillet reduction by 50%

Acceptance criteria: Sealing filet width reduction < 50% 0 reject / 2 parts

#### Results:

- No pin hole whatever lid configuration is

- No configuration fully compliant with space standards (solder alloy overflow)

- Only 2mm Kovar combo lid OK after some process improvements

|   | IVE       | X-rays   | Conclusion |

|---|-----------|----------|------------|

| 1 | 3 rejects | 1 reject | Fail       |

| 2 | 0         | 0        | ОК         |

| 3 | 2         | 0        | Fail       |

| 4 | 2         | 0        | Fail       |

- 5mm seal ring: additional tests were performed to mitigate the solder alloy overflow

- Standard process: use of 4 clips 1.5 pound

- Trial 1: reduce the number of clips down to 2

→No improvement (16 rejects / 20 parts)

- Trial 2: reduce the clips pressure down to 1 pound

- $\rightarrow$  No improvement (18 rejects / 20 parts)

#### Conclusions

#### Recommendation was to go ahead with 2mm kovar option

#### Validation and reliability tests

- ✓ Cavity co-planarity characterization

- ✓ Die attach tests

- ✓ Seal ring characterization hermeticity

- ✓ Thermal cycling (300 cycles)

- ✓ Fine and gross Leak

- ✓ Vapor content (3#)

- ✓ Micro-sectionning (2#)

- ✓ PIND tests

- ✓ Visual inspection & X-rays

- ✓ Stud pull test (10#)

#### Conclusions

#### Process is compliant with space quality level

# Daisy chain packages (B1): manufacturing and delivery

- The aim of this was to validate the assembly of the packages on the boards

- This package is worst case compared to the final package from a thermal point of view:

- Smaller die (10\*10 mm instead of 14\*14)

- Smaller ceramic thickness (3mm instead of 6mm)

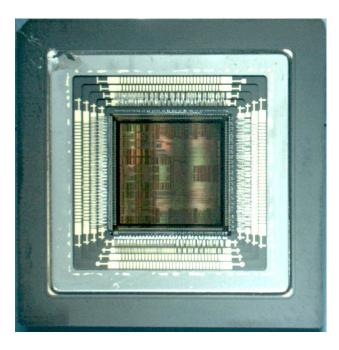

- This package includes a thermal die, PMOS4 from Tyndall with:

- Heater resistor (up to 12W)

- Temperature reference diodes (3 per die)

- Strain gauges (6 per die)

April 10

# Daisy chain packages (B1): manufacturing and delivery

- We proceeded with the procurement of the PMOS4 thermal die, the test socket & board

- We set the package specification, designed and procured it

- We packaged the PMOS4 die to produce 40#, tested them and shipped them to the customer for evaluation of their assembly on flight boards

- B1 thickness is 3mm and is a worst case for thermal & mechanical evaluation with respect to the 6mm for the C package which will allow for a better heat conduction

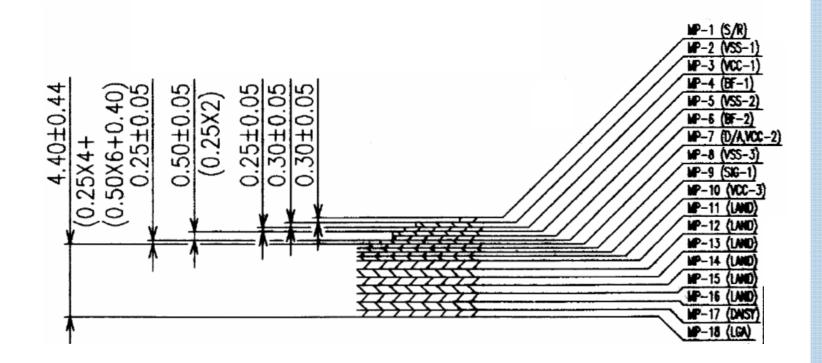

#### PACKAGE B1 THERMAL DIE + DAISY CHAINS

#### Package design (1/2)

AMEL

#### PACKAGE B1 THERMAL DIE + DAISY CHAINS

Package design (2/2)

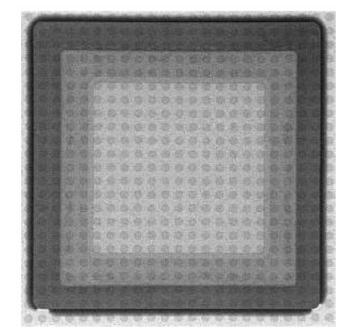

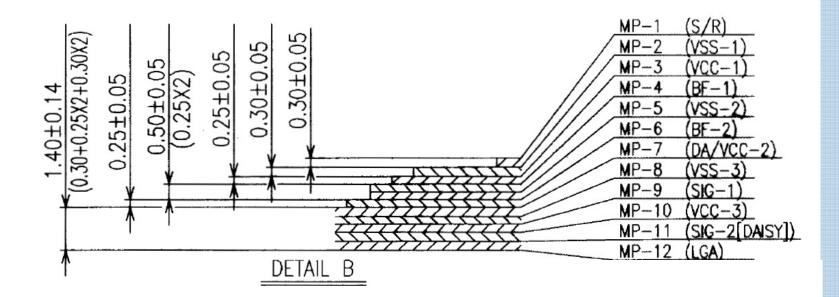

#### PACKAGE B1 THERMAL DIE + DAISY CHAINS

540 unused pins are daisy chained as follow

$\otimes \otimes \otimes$  $\otimes \otimes \otimes$ \$\$\$\$\$\$\$\$\$\$\$\$\$\$\$\$  $\bigotimes \otimes \bigotimes$  $\otimes \otimes$  $\langle \chi \rangle$  $\otimes \otimes \otimes \otimes$  $\otimes \otimes \otimes$  $\otimes \otimes \otimes \otimes$  $\otimes$   $\otimes$   $\otimes$  $\otimes \otimes \otimes \otimes \otimes \otimes$  $\otimes \otimes \otimes \otimes \otimes \otimes \otimes$  $\otimes \otimes \otimes \otimes$ \*\*\* \*\*\*\*  $\otimes \otimes \otimes \otimes \otimes \otimes \otimes \otimes$  $\otimes \otimes \otimes \otimes \otimes \otimes \otimes$  $\otimes \otimes \otimes \otimes \otimes \otimes \otimes$  $\otimes \otimes \otimes \otimes \otimes \otimes \otimes \otimes \otimes$  $\otimes \otimes \otimes$

- The aim of this package is to start the qualification of the final package (1<sup>st</sup> and 2<sup>nd</sup> lot) with an available ASIC die

- Same thickness than final package (6mm), same seal ring...

- Only cavity size is different

No parts have been delivered to the customer, only the qualification tests report

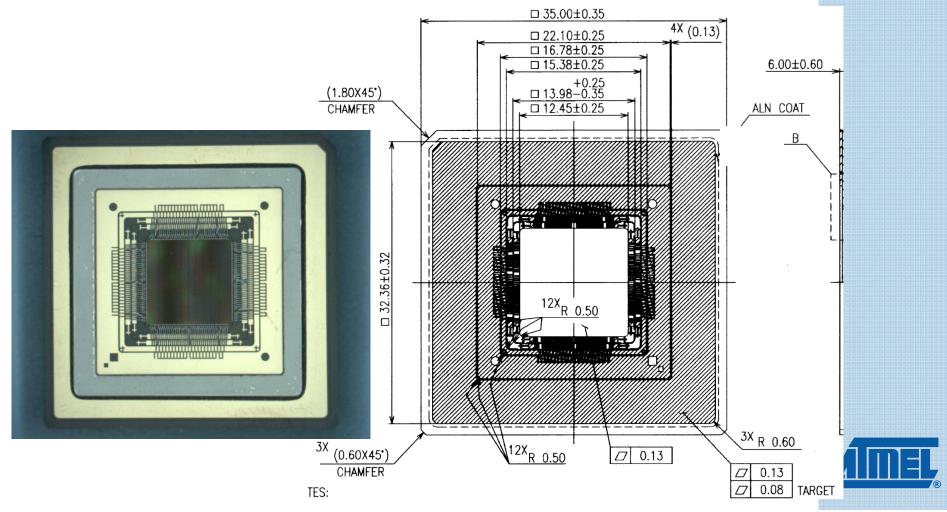

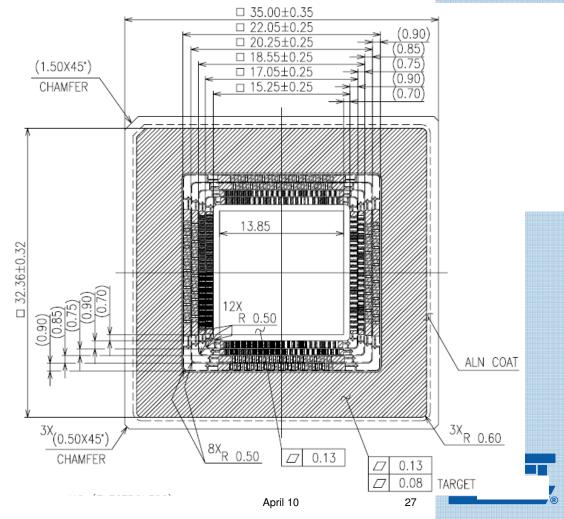

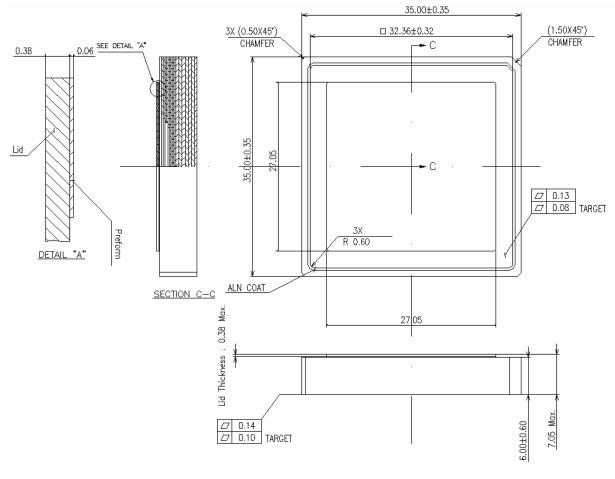

#### Package design (1/2)

#### Package design (2/2)

- Die manufacturing and probe

- B2 Package specification, design and procurement

- Lot 1 was assembled, tested to QML V and CNES CSI'd

- Lot 2 was assembled, tested to QML V and CNES CSI'd

- First and second lots qualification on going

| End customer ASIC manufacturing     | Completed     |

|-------------------------------------|---------------|

| Package C design and procurement    | Completed     |

| End customer ASIC industrialization | Completed     |

| Lot 3 assembled and CNES precaped   | On going (1)  |

| ESCC qualification test plan        | Completed (2) |

| Lot 3 CNES CSI                      | 10W18         |

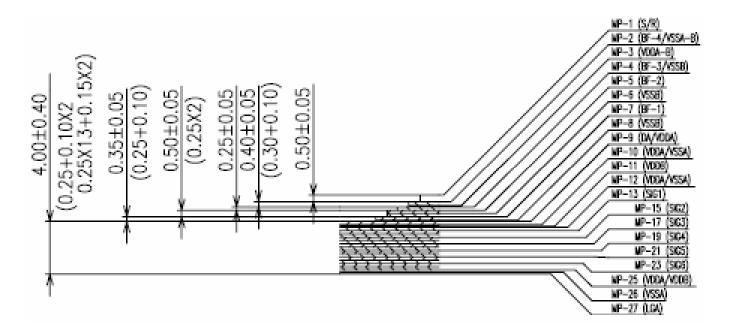

#### Package design (1/4)

#### Package design (2/4)

#### Package design (3/4)

29

April 10

#### Package design (4/4)

The 27 layers were necessary for a good matching of the LVDS

April 10

### **ESCC QUALIFICATION STATUS**

| Lot 3 parts ready for qualification | 10W19 |

|-------------------------------------|-------|

| Atmel qualification completed       | 10W25 |

| Atmel qualification report          | 10W26 |

| ESCC evaluation completed           | 10W33 |

|                                     | 10W35 |

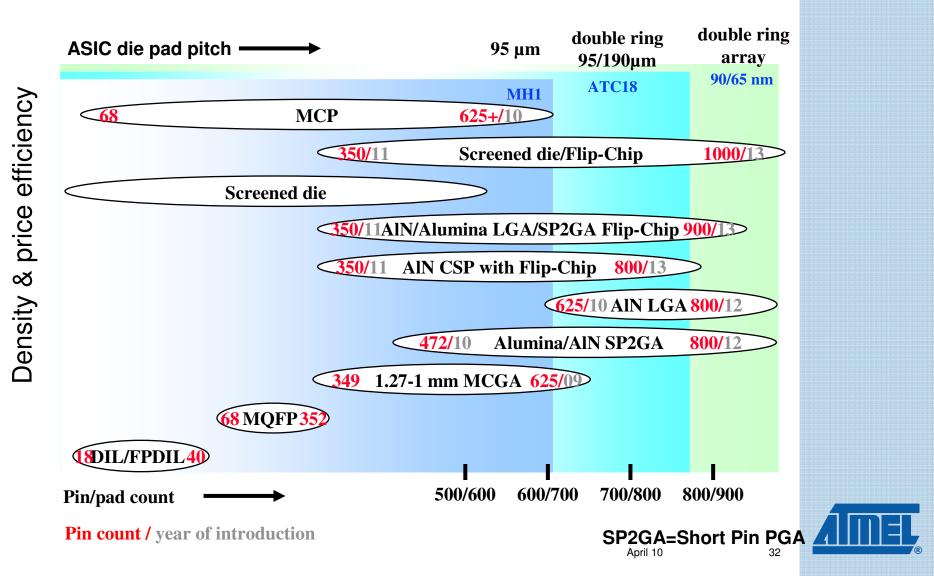

### **SPACE PACKAGES OFFERING & ROADMAP**

### THANKS TO ...

Jean-Louis Venturin and David Dangla, CNES, who managed to make and manage this contract

Valérie Briot, ATMEL, who managed it!