### SpaceWire Router ASIC

Steve Parkes, Chris McClements

Space Technology Centre, University of Dundee

Gerald Kempf, Christian Toegel

Austrian Aerospace

Stephan Fisher Astrium GmbH,

Pierre Fabry, Agustin Leon ESA, ESTEC

## SpW-10X Architecture

#### SpaceWire Ports

- SpaceWire compliant

- Data Signalling Rate

- 200 Mbits/s maximum

- Selectable 2 200 Mbits/s

- Each SpaceWire port can run at a different speed

- LVDS drivers and receivers on chip

- Avoids size, mass, cost of external LVDS chips

- Receiver auto-start mode

- Power control

- Each SpaceWire port can be completely disabled

- including clock tree

- LVDS can be tri-stated with auto-enable

- Links can be held disconnected until there is data to send

#### **Parallel Ports**

- Parallel ports to support connection to

- Processors

- Simple logic

- 8-bit data + control/data flag

- FIFO type interface

- Operate at speed of SpaceWire links

- i.e. 200 Mbits/s

### Routing Switch

- Switches packet being received to

- Appropriate output port

- SpaceWire and Parallel ports treated the same

- Non-blocking

- If the required output port is not being used already

- Guaranteed to be able to forward packet

- Rapid packet switching times

- Low latency

- Worm-hole routing

### SpaceWire Packets

- Packet Format

- <DESTINATION> <CARGO> <END OF PACKET MARKER>

- Destination

- represents either path to, or identity of destination node

- Cargo

- data or message to be transferred from source to destination

- End of Packet Marker

- indicates end of packet

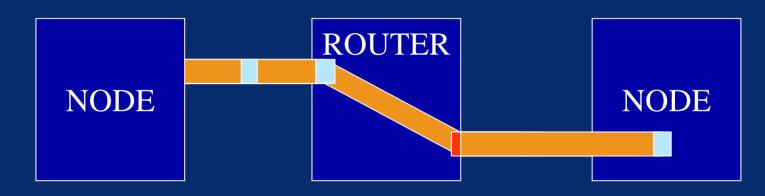

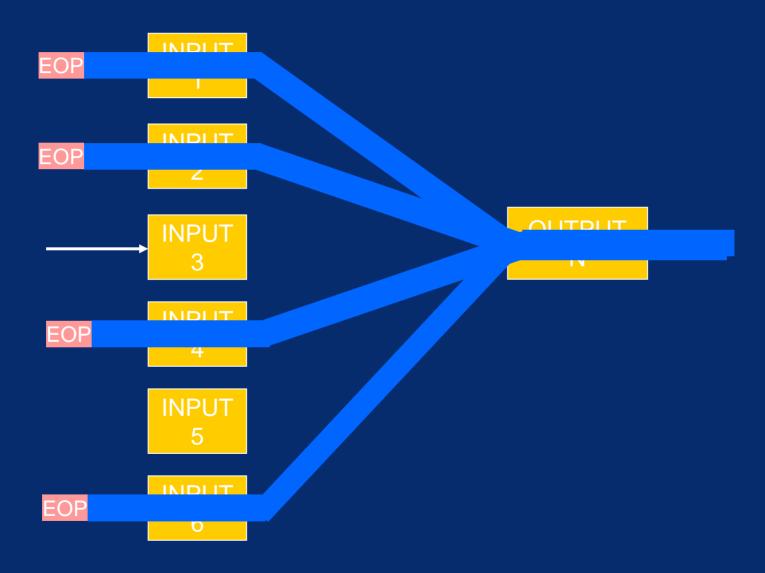

### Wormhole Routing

Node sends out packet

Router receives header and checks requested output port

Router connects input to output and packet flows through router

When EOP marker seen, router terminates connection

and frees output port

#### Wormhole Routing

#### Advantages

- No packet buffering

- Little buffer memory

- Can support packets of arbitrary size

- Rapid switching

#### Disadvantages

- If output port not ready

- Then have to wait

- Blocks all links being used for the waiting packet

# Routing Table

|                    | Address | Port O | Port 1 | Port 2                       | Port 3 | Port 4 |

|--------------------|---------|--------|--------|------------------------------|--------|--------|

| Configuration      | 0       | 1      | 0      | 0                            | 0      | 0      |

|                    | 1       | 0      | 1      | 0                            | 0      | 0      |

| Path<br>Addressing | 2       | 0      | 0      | 1                            | 0      | 0      |

| ,                  |         |        |        | 0 1 0<br>1 0<br>0 0<br>0 1 0 |        |        |

|                    | 32      | 0      | 1      | 0                            | 0      | 0      |

| Logical            | 33      | 0      | 0      | 1                            | 0      | 0      |

| Addressing         | 34      | 0      | 0      | 0                            | 0      | 1      |

|                    |         |        |        |                              |        |        |

| Reserved           | 255     | 0      | 0      | 0                            | 0      | 0      |

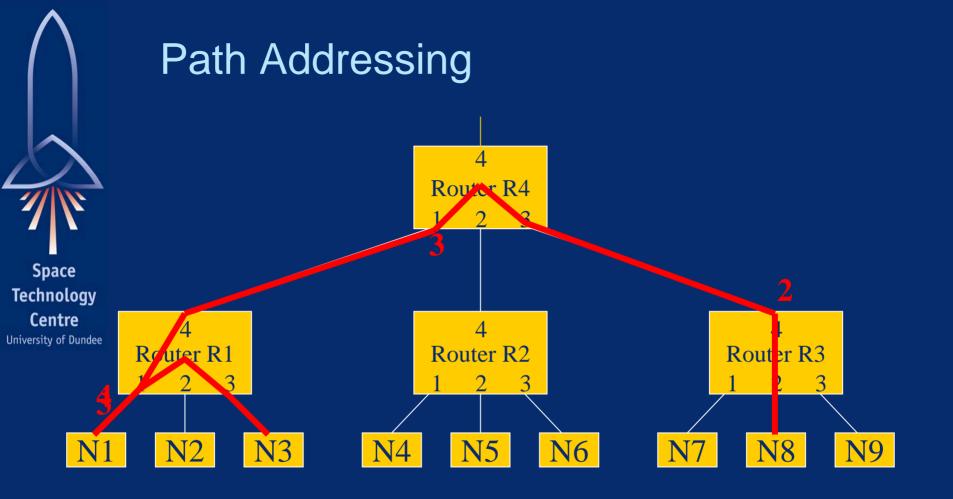

- destination is specified as router output port number

- node 1 to node 3 <3><cargo><EOP>

- node 1 to node 8 <4><3><2><cargo><EOP>

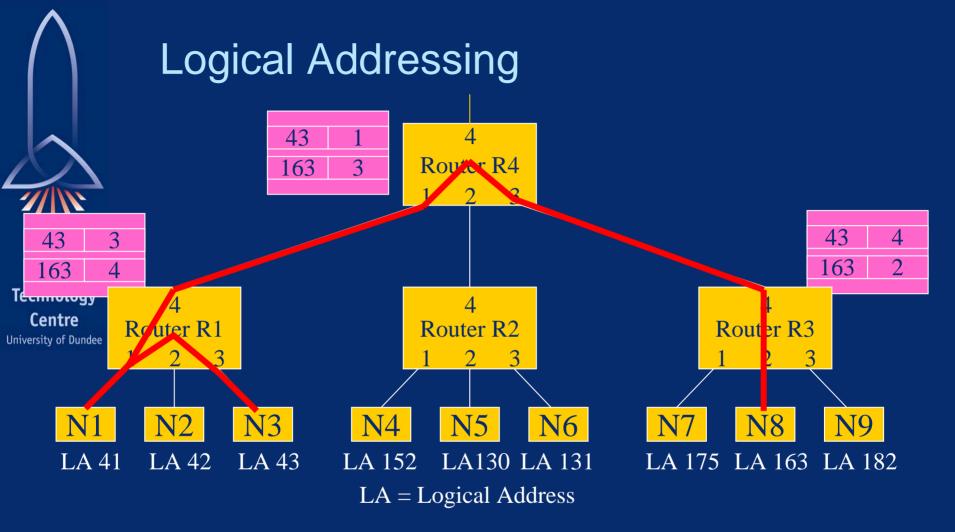

- each destination has a unique logical address

- each router has a list of which port(s) to send data out for each possible destination

- node 1 to node with logical address 43 <43><cargo><EOP>

- node 1 to node with logical address 163 <163><cargo><EOP>

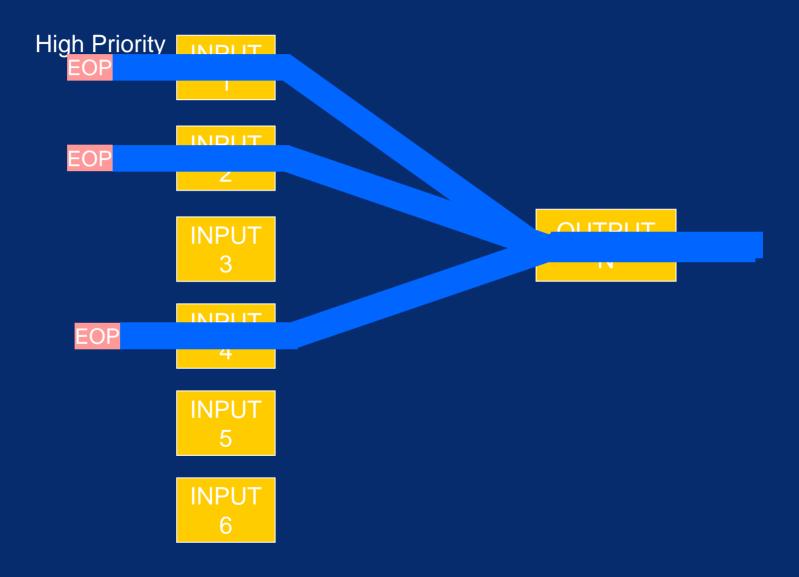

## **Priority**

- Arbitration in Router

- Fair arbitration

- Priority based

- SpaceWire header contains address only

- Assign priority to logical addresses

#### Arbitration

# Priority

|    |                    | Address | Priority | Port 0 | Port 1 | Port 2 | Port 3 | Port 4 |

|----|--------------------|---------|----------|--------|--------|--------|--------|--------|

|    | Configuration      | 0       | 0        | 1      | 0      | 0      | 0      | 0      |

|    |                    | 1       | 0        | 0      | 1      | 0      | 0      | 0      |

| Ž. | Path<br>Addressing | 2       | 0        | 0      | 0      | 1      | 0      | 0      |

| e  |                    |         |          |        |        |        | 0      |        |

|    | Logical            | 32      | 0        | 0      | 1      | 0      | 0      | 0      |

|    |                    | 33      | 1        | 0      | 1      | 0      | 0      | 0      |

|    | Addressing         | 34      | 0        | 0      | 0      | 0      | 0      | 1      |

|    |                    |         |          |        |        |        |        |        |

|    | Reserved           | 255     | 0        | 0      | 0      | 0      | 0      | 0      |

# Arbitration with Priority

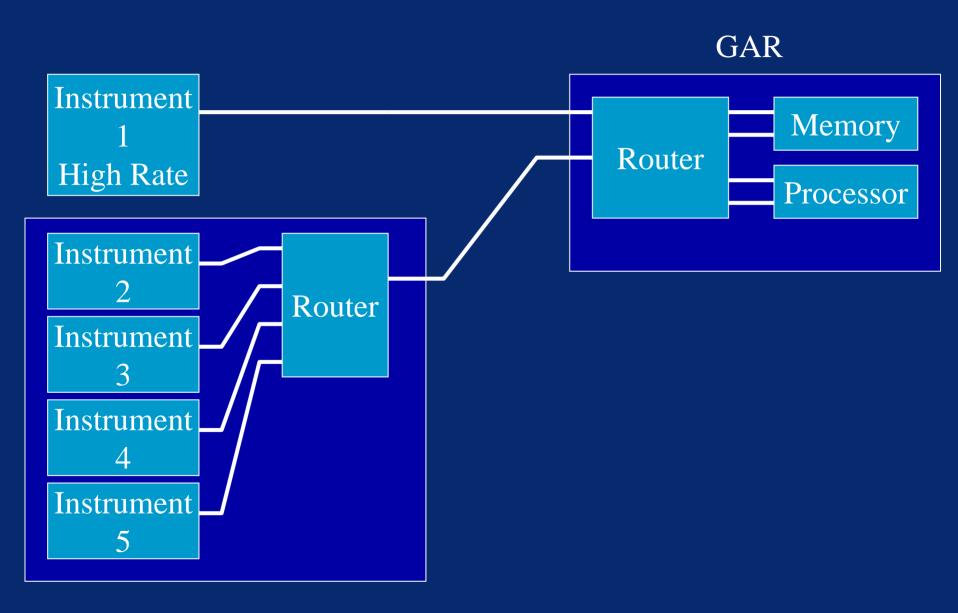

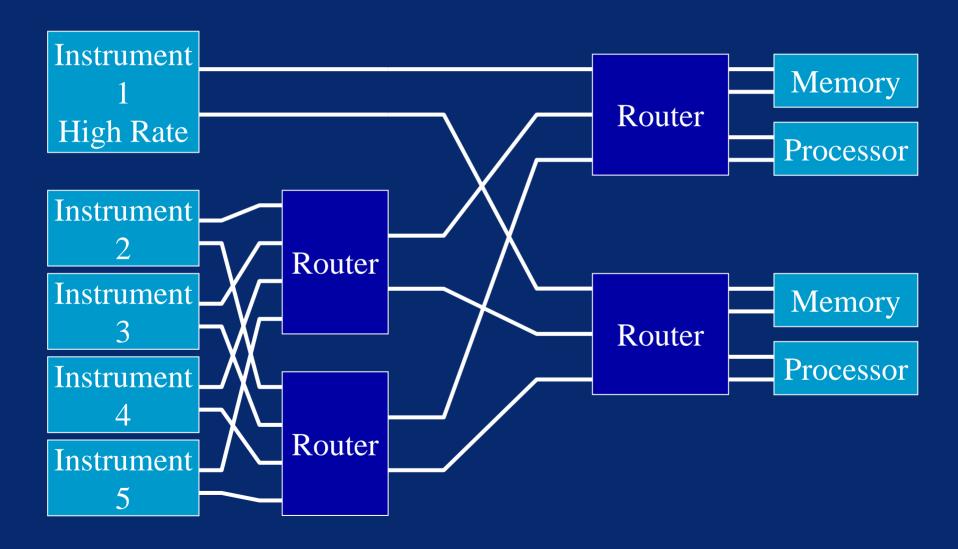

# Group Adaptive Routing

# **Group Adaptive Routing**

|   |                       | Address | Priority | Port O | Port 1 | Port 2 | Port 3 | Port 4 |

|---|-----------------------|---------|----------|--------|--------|--------|--------|--------|

|   | Configuration         | 0       | 0        | 1      | 0      | 0      | 0 0    | 0      |

|   |                       | 1       | 0        | 0      | 1      | 0      | 0      | 0      |

|   | Path<br>Addressing    | 2       | 0        | 0      | 0      | 1      | 0      | 0      |

| e |                       |         |          |        |        |        |        |        |

|   | Logical<br>Addressing | 32      | 0        | 0      | 1      | 1      | 0      | 0      |

|   |                       | 33      | 1        | 0      | 1      | 1      | 0      | 0      |

|   |                       | 34      | 0        | 0      | 0      | 0      | 1      | 1      |

|   |                       |         |          |        |        |        |        |        |

|   | Reserved              | 255     | 0        | 0      | 0      | 0      | 0      | 0      |

### Configuration Port

- Used to configure router device

- Routing tables

- Link speeds

- Power states

- Etc

- Used to read router status

- RMAP Remote Memory Access Protocol

- Used for reading and writing configuration port registers

- Router can be configured over

- Any SpaceWire port

- Any Parallel port

#### Time-Code Port

Sends and receives time-codes

#### Tick-in

- Internal time-counter incremented and time-code sent

- Or

- Value on the time-code input port is sent as a time-code

#### Tick-out

- Indicates valid time-code received

- Value of time-code on time-code output port

# Status/Configuration Interface

- On power up holds some configuration information

- Thereafter provides status according to four address lines

- 0-10: Port status

- 0: Configuration port

- 1-8: SpaceWire port

- 9-10: Parallel port

- 11: Network discovery

- Return port

- This is a router

- 12: Router control

- Enables and timeouts

- 13: Error active

- 14: Time-code

- 15: General purpose

- Contents of general purpose register

- Settable by configuration command

#### Router ASIC Performance

#### ASIC

- Implementation in Atmel MH1RT gate array

- Max gate count 519 kgates (typical)

- 0.35 µm CMOS process

#### Radiation tolerance

- 100 krad

- SEU free cells to 100 MeV

- Used for all critical memory cells

- Latch-up immunity to 80 MeV

#### Performance

- SpaceWire interface baud-rate 200 Mbits/s

- LVDS drivers/receivers integrated on-chip

#### Power

- 4 W power with all links at maximum data rate

- Single 3.3 V supply voltage

#### Package

196 pin ceramic Quad Flat Pack 25 mil pin spacing

## ESA SpaceWire Router Performance

SpaceWire Router Latency and Jitter Measurements (Bit rate = 200Mbits/s)

[1] Note all figures are worst case

| Description                                     | Symbol              | Value | Units   |

|-------------------------------------------------|---------------------|-------|---------|

| Switching Latency                               | T <sub>SWITCH</sub> | 133.3 | ns, max |

| Router Latency – SpaceWire to SpaceWire port    | T <sub>SSDATA</sub> | 546.6 | ns, max |

| Router Latency – SpaceWire to External port     | T <sub>SEDATA</sub> | 316.6 | ns, max |

| Router Latency – External to SpaceWire port     | T <sub>ESDATA</sub> | 363.3 | ns, max |

| Router Latency – External to External port      | T <sub>EEDATA</sub> | 166.6 | ns, max |

| Time-code Latency – SpaceWire to SpaceWire port | T <sub>SSTC</sub>   | 409.3 | ns, max |

| Time-code Latency – SpaceWire to External port  | T <sub>SETC</sub>   | 316.6 | ns, max |

| Time-code Latency – External to SpaceWire port  | T <sub>ESTC</sub>   | 359.9 | ns, max |

| Time-code Jitter                                | T <sub>TCJIT</sub>  | 116.6 | ns, max |

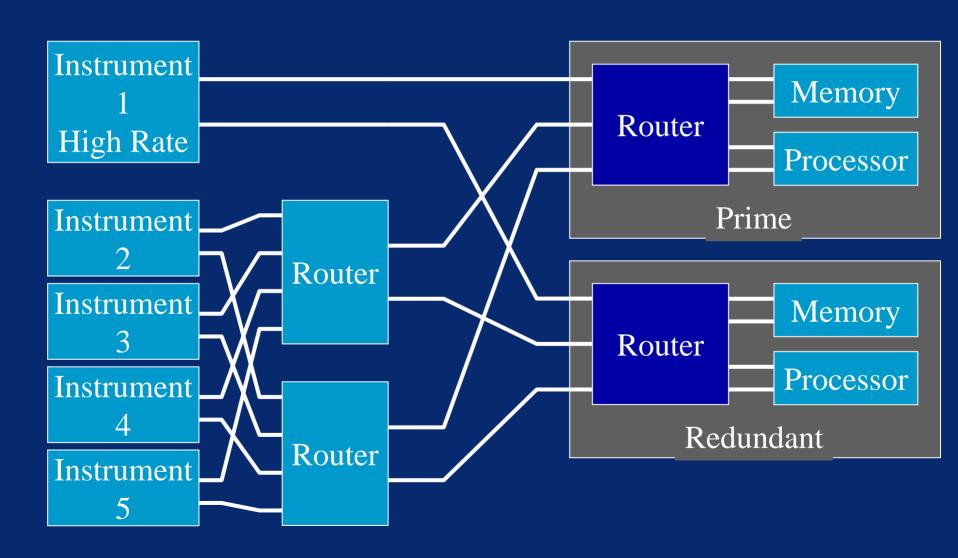

### Applications – Standalone Router

### Applications – Embedded Router

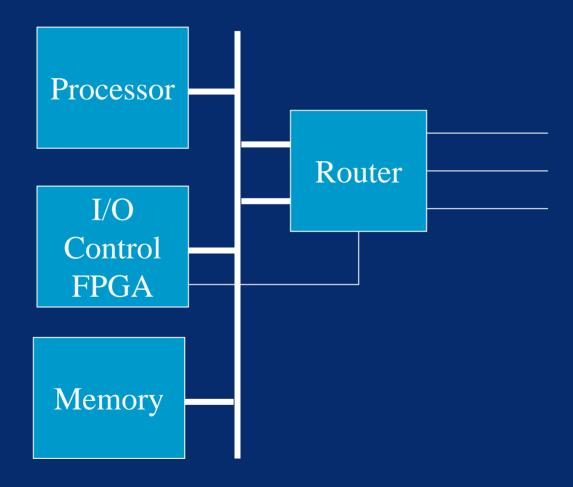

# Applications – Node Interface

# Applications – Node Interface

# Applications – Node Interface

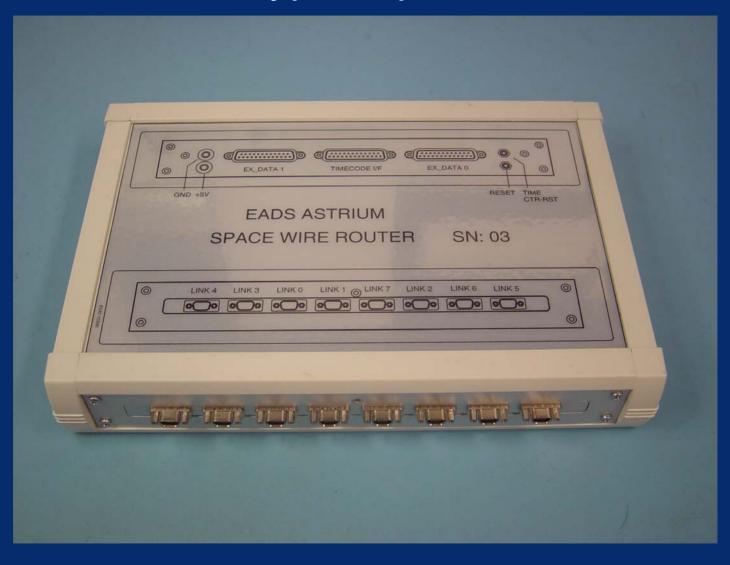

# Router Prototype Implementations

# Router Prototype Implementations

# Router Prototype Implementations

#### Team

- University of Dundee

- Design and Testing

- Austrian Aerospace

- Independent VHDL Test Bench

- Transfer to ASIC technology

- Astrium GmbH

- Functional Testing

- Atmel

- ASIC Manufacture

- STAR-Dundee

- Support and Test Equipment

#### Conclusions

- ESA router has extensive capabilities

- Suitable for a wide range of applications

- Independently tested

- Extensively validated

- Full range of support services available