# The ADPMS experience

## An <u>Advanced Data & Power Management System</u> for small satellites & missions

Author: Koen Puimege – Verhaert Space – koen.puimege@verhaert.com Hogenakkerhoekstraat 9, 9150 Kruibeke, Belgium www.verhaert.com

7-8 March 2007

**ESTEC's Microelectronics Presentation Days**

Slide 1

## Contents

- Introduction

- Satellite requirements

- System design

- Architectural

- Chip design

- Validation approach

- Critical area's

- The result

- Key features

- The team

## Introduction

In a contract for the European Space Agency, Verhaert Space developed a state-off-the-art control unit for small but high demanding satellites.

Built on the experience gained with the PROBA-I satellite that has been in daily use since its launch in 2001. This next generation avionics has been developed and will have its first in-orbit demonstration in 2007 as the satellite control unit for PROBA-II.

The need for a performant, easily adapted and configured satellite control unit has been identified as crucial to succeed in the system design of small satellites with high autonomy demands.

The European Space Agency initiated different programs to demonstrate the concept and feasibility of small satellites with high performances in terms of:

- Autonomy

- On board processing capabilities

- Payload management

## **Introduction (2)**

The PROBA-I satellite, currently in orbit, has shown some limitations in its Data Handling System, Payload Processing Unit and Power Conditioning System in terms of:

- **Power consumption**

- Mass and Volume

- Design complexity due to a lack of uniformity

- Proprietary 'closed' architecture (black box design)

- Limited computing and data-handling performance

- **Modularity**

- **Scalability**

- **Testability**

A detailed look at the above top-level requirements identifies however some contradictions:

- Low power consumption versus high computing performance

- Low mass and volume versus modularity

- Highly integrated system versus testability

This presentation describes how the ADPMS design has provided an answer to all above criteria without penalising one of them.

## **Satellite requirements**

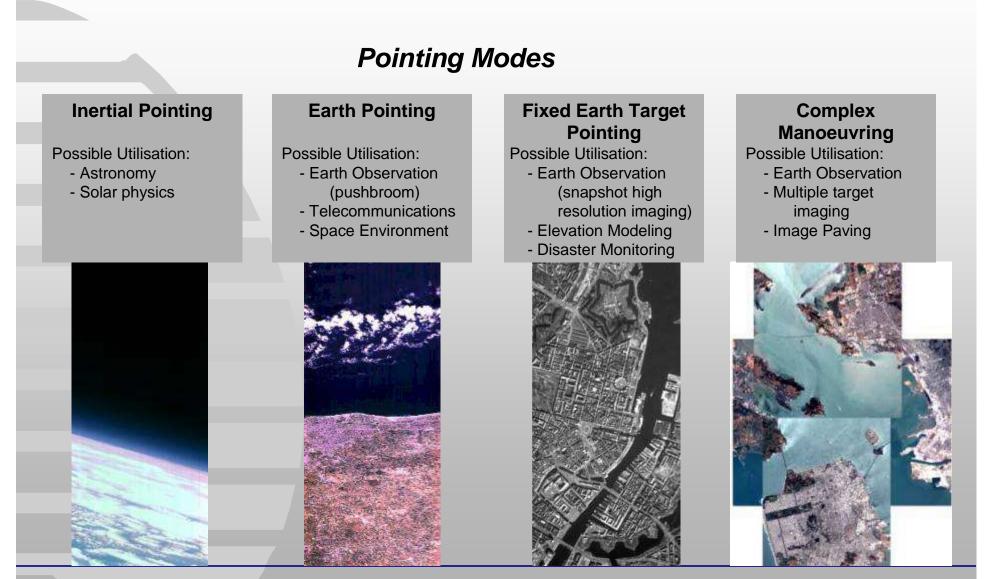

### Onboard Autonomy Features

- Autonomy in planning / scheduling

- Autonomy in attitude control system

- Autonomous target prediction and trajectory generation

- High level payload management

- Powerful automated on-board functions

# For Earth Observation instruments

1 image = 1 command

( target latitude and longitude)

## Ground Segment Automation

- Internet access for payload activity requests

- Internet access for payload data distribution

- "Light-out" ground segment

# Satellite requirements (2)

7-8 March 2007

**ESTEC's Microelectronics Presentation Days**

Slide 6

# **Satellite requirements (3)**

## Satellite requirements (4)

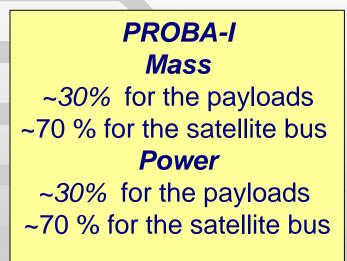

Satellite Objective: more resources available for the Payloads

20% reduction for the bus elements

PROBA-II Mass ~50% for the payloads ~50% for the satellite bus Power ~50% for the payloads ~50% for the satellite bus

7-8 March 2007

**ESTEC's Microelectronics Presentation Days**

Slide 8

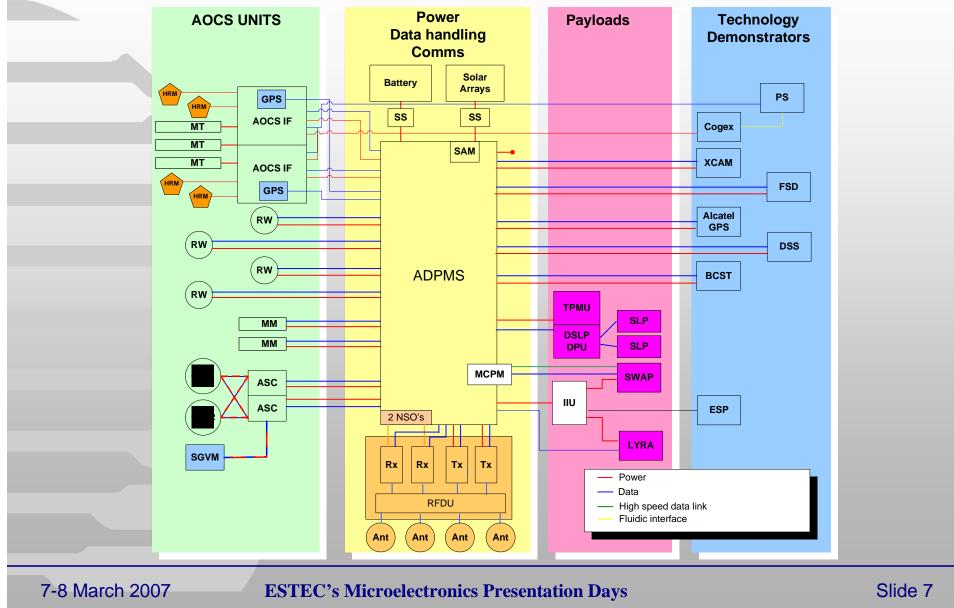

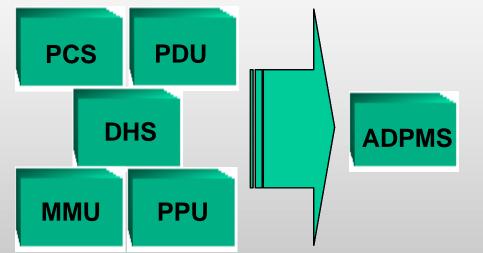

## **ADPMS System design**

In order to fulfil the top-level requirements listed before some drastic changes were needed. Therefore the following five essential satellite bus elements have been incorporated into one system:

- S/C Power Conditioning System (PCS)

- S/C Power Distribution Unit (PDU)

- S/C Data Handling System (DHS)

- S/C Mass Memory Unit (MMU)

7-8 March 2007

• S/C Payload Processing Unit (PPU)

A very effective power, mass and volume reduction could be achieved by the integration of these elements. Resulting at Satellite level in a:

- centralisation of all data handling, storage and processing

- centralisation of all analog- and temperature sensor acquisition

- elimination of the harness that interconnected the formerly separate units

- reduction of the mechanics because of the integration into one physical enclosure.

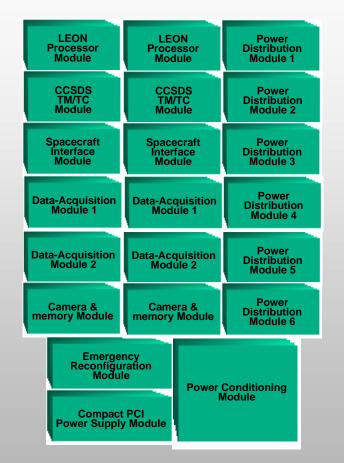

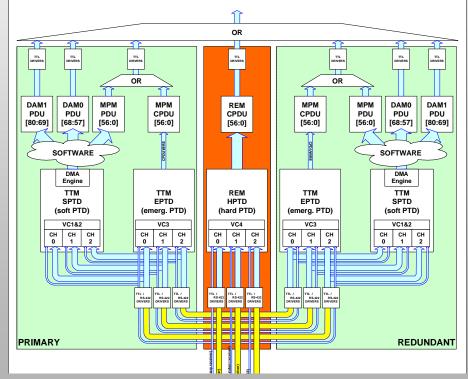

## **ADPMS** Architectural

## Architectural overview

The computer is partitioned into sub-modules in the form of 3U Compact-PCI boards.

The main modules consist of:

- a processor board with memory

- a TM/TC board

- a spacecraft interface board

- one or more data-acquisition boards

- a camera board with mass memory

- a reconfiguration board.

The integrated power system consists of:

- a power conditioning module

- several power distribution modules

- a Compact-PCI power supply module.

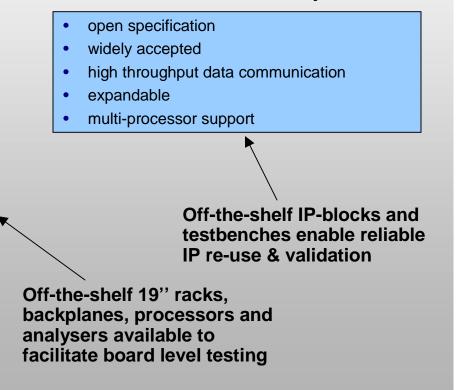

## **ADPMS Architectural (2)**

#### Re-use of industrial standards

The design complexity of the ADPMS has been significantly reduced by the implementation of some wellproven industrial specifications resulting in a higher uniformity of the FPGA and board designs. The selection of these widely-used standards

#### Compact PCI standard $\rightarrow$ key-features:

- open specification (coordinated by PCISIG and PICMG)

- widely accepted  $\rightarrow$  reviewed by a large user community

- protocol-, electrical-, mechanical- and configurationaspects guarantee compatibility between plug-in boards

- electrical- and pcb-layout guidelines allow reliable

product-design

- suited for rugged environments

- low power consumption (reflected wave-switching <-> fixed bus terminations)

- high throughput data communication

- light weight, high-density, low EMC connector technology

- expandable

- multi-processor support.

#### AMBA<sup>™</sup> AHB standard $\rightarrow$ key-features:

## **ADPMS Architectural (3)**

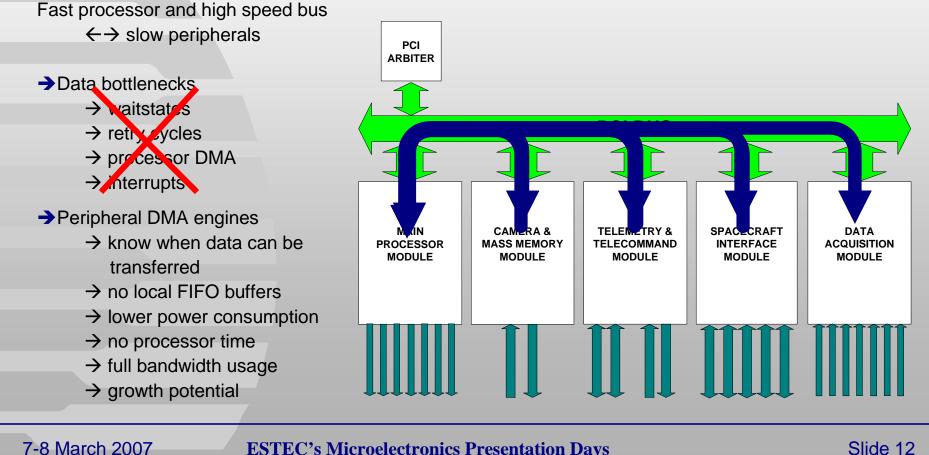

## Peripheral DMA engines

In many existing systems, communication between modules with unequal data rates or large data latencies create blocking of the shared buses, such as the PCI bus or on-chip AMBA buses.

### Software packet telecommand decoder

Having a H/W recovery TC decoder, the need for a full blown hardware TC decoder in the nominal and redundant lanes might not be so strong. Since the recovery TC decoder is 'hot' and since the nominal and redundant lanes have a limited emergency TC-decoder in hardware, this requirement is no longer needed for the nominal TC decoder. Therefore this nominal TC decoder can be implemented in software.

#### The benefits:

- → the protocol can be changed to future versions without hardware redesign

- $\rightarrow$  Authentication can be added in software

- $\rightarrow$  Additional VC-ID's can be easily added

- $\rightarrow$  Additional MAP-ID's can be easily added

- → the (hardware) failure rate decreases since less logic is needed

- $\rightarrow$  no large FPGA needed anymore

- $\rightarrow$  no PROM needed anymore

- $\rightarrow$  no radiation-hard static RAM needed anymore

- $\rightarrow$  the power consumption is reduced

- → virtually no extra power required since the processor performance needed is less than 10 KIPS

## **ADPMS Architectural (6)**

## A new processor

A trade-off was made between LEON2 and LEON3 in both FPGA and ASIC implementation.

Where the LEON3 (implemented in an ACTEL RTAX2000 FPGA) gives slightly better performance than the former ERC-32. For this project there was a need to demonstrate high computing performance. Therefore the LEON2-FT (AT697 from ATMEL) has been selected. It has a superior performance with respect to its successor the ERC-32 not only because it can run at a higher clock frequency but especially because of the following key-features:

- > The on-chip PCI host bridge makes the connection to a high throughput PCI backplane straightforward

- → The availability of a **powerful debug support unit** made it very suitable for this application

- The LEON supports via its PCI-target interface direct memory access which allows the onboard software to concentrate on its processing tasks while all data movement is done with a minimal software interaction

- → the high clock frequency

- → the 7-stage pipeline

- → the data- and instruction cache

- → less sensitive to slow memories

- → the little power consumption.

- →the SDRAM memory controller

- → large memory footprint for minimal board space and little power consumption

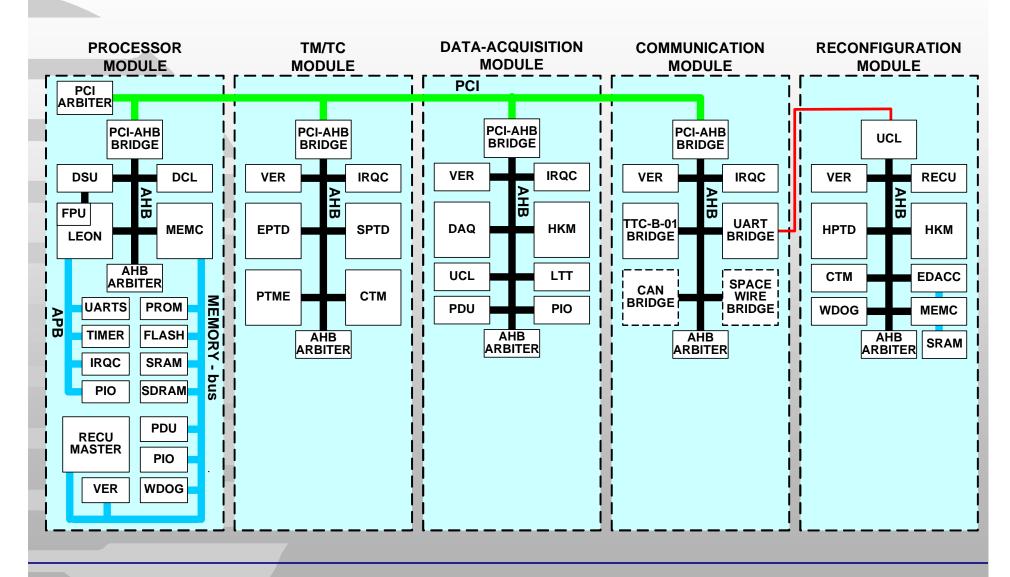

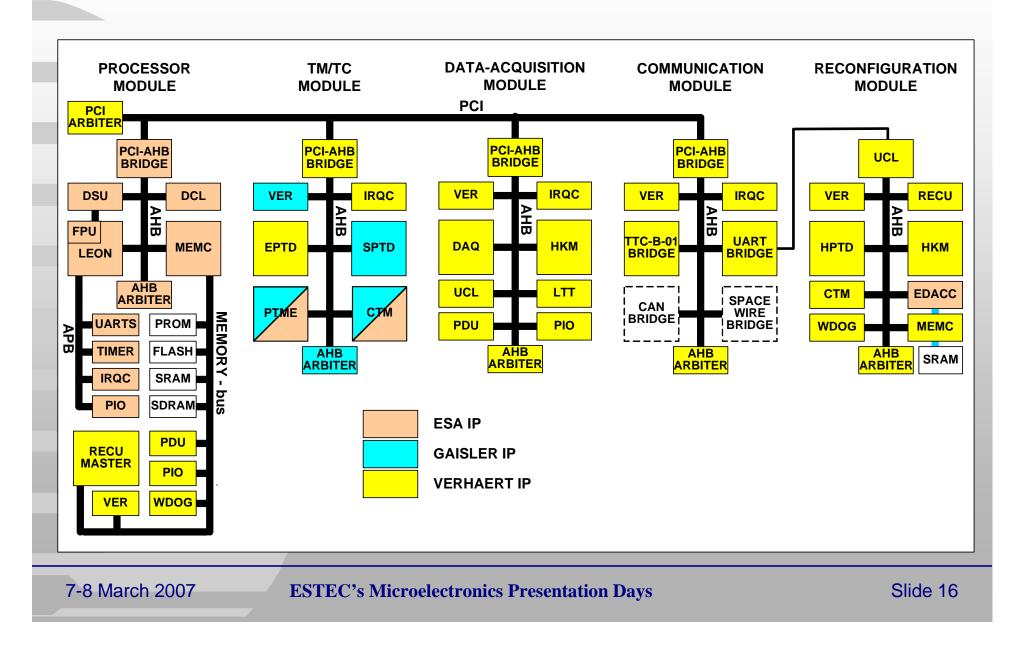

## **ADPMS Chip Design**

7-8 March 2007

## **ADPMS Chip Design (2)**

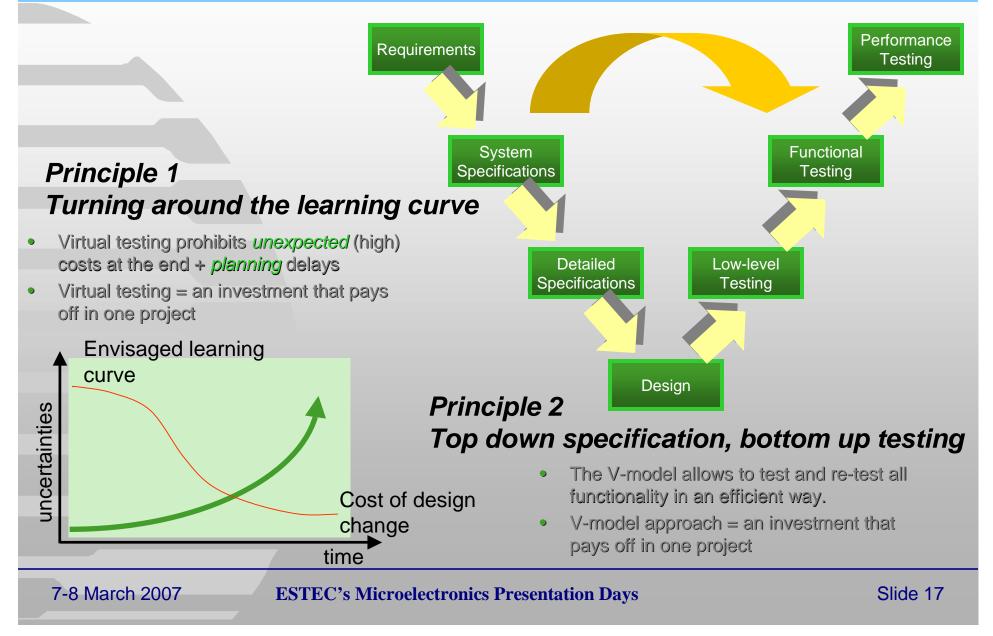

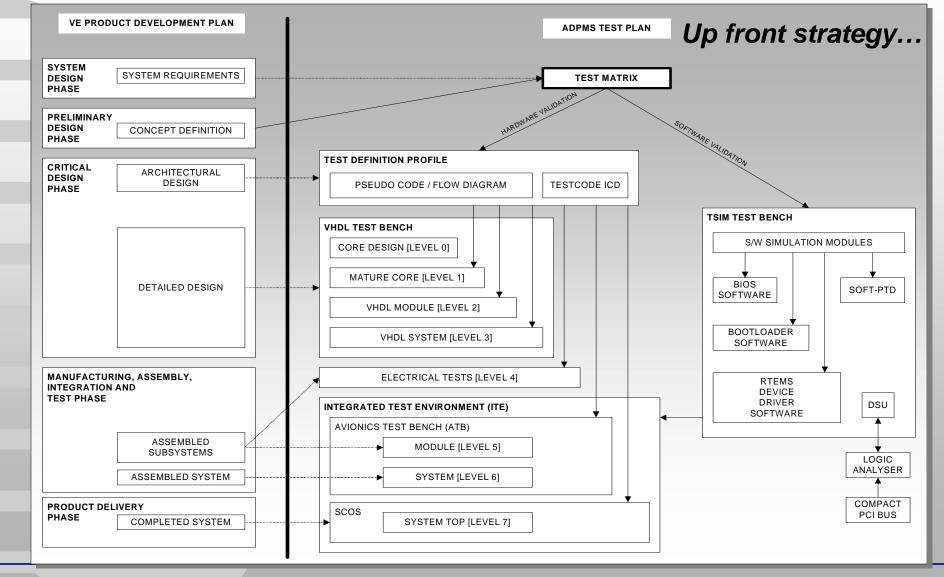

# **Validation Approach**

# Validation Approach (2)

7-8 March 2007

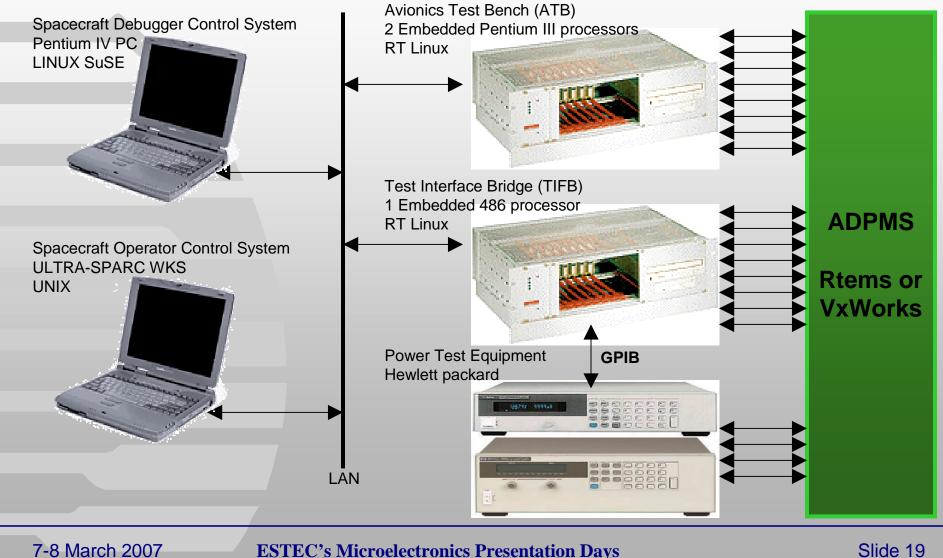

# Validation Approach (3)

## An integrated test environment...

## **ADPMS Critical area's**

Herewith an shortlist of the most important problems encountered during the ADPMS development

- Achieving the PCI I/O timing in an ACTEL RTAX2000 FPGA

- Finding a low voltage DC/DC converter with good efficiency

- Estimating the power-consumption of ACTEL RTAX2000 SoC designs

- Qualifying the reflow-process for a 624-pin CCGA for use in space

- Qualifying the pcb-process for a 324-pin MCGA for use in space

- Soldering RoHS compliant parts

## **ADPMS The Result**

The ADPMS configured for the Proba-II satellite offers the following functionality for the following budgets: **Power distribution** 1 failure - 24 outputs of 28V / 50W tolerant **Processor board** - current protected with auto restart **Backplane** system - switchable or non-switchable - designed for 100MHz operation data throughput - 64 Mbyte SDRAM up to 1 GBps - battery undervoltage protected - 4 Mbyte SRAM with auto switch off - 4 Mbyte Flash Telecomma Budgets - 256 kByte Prom **Power conditioning** - 2 Mbps upl \_\_\_\_\_ - Up to 300W satellite peak power - 4 virtual ch - Up to 6 solar sections 13 kg Mass - configurab **Mass memory** Volume 455x160x267mm - 56 CPDU d - 512 Mbyte ime interfaces Power 7 W (computer) - with EDAC programmable clock outputs **Context memory 10 W (power-system)** clock datation inputs - 128 kbyte - 2 packetwire inputs H/W - with EDAC - full encoding **Communication Interfaces** recovery H/W - Up to 25 UART channels **TC decoder** generated - Up to 6 TTC-B-01 channels Multi emergency - a camera interface **Analogue Interfaces** processor telemetry with frame grabber - Up to 80 analogue inputs support - 2 packetwires - Up to 32 temperature inputs 7-8 March 2007

# **ADPMS Key features**

#### High performance

- → 100MIPS LEON processor

- $\rightarrow$  1GBit/s high throughput backplane

- $\rightarrow$  4Gbit mass memory (easily expandible)

- $\rightarrow$  100MBit/s downlink capability

#### Low power consumption

- $\rightarrow$  low power, low voltage components (3,3V & 1,5V)

- → utilisation of large radiation tolerant FPGA's

#### Miniaturised avionics (mass & volume)

- → Optimal highly integrated housing design

- $\rightarrow$  Qualification of new high pin-count packages (CGA)

- $\rightarrow$  99% surface mount technology (SMD)

#### Easy satellite integration

- → Easy test access guarantied after S/C integration

- $\rightarrow$  Open architecture ( $\leftrightarrow$  black box design)

- $\rightarrow$  Improved testability

- → Thermal control fully passive

#### **Growth potential – High re-use factor**

- $\rightarrow$  High throughput backplane

- → Multiprocessor support

- $\rightarrow$  Modular & scalable design

## **ADPMS The team**

#### The team

#### The ADPMS development has been carried out by

Verhaert Space a leading Belgian small space systems company.

With a track record of more than 30 years Verhaert Space develops advanced small space systems for agencies, large systems integrators and governments. Ranging from advanced small satellites, advanced space mechanisms & structures, and instruments & facilities for micro gravity research in manned and unmanned missions.

#### But could also be realised thanks to a good support from ESA and ATMEL

Mr. André Pouponnot, Mr. Roland Weigand, the PROBA-project team and Mr. Nicolas Renaud

#### And by a teaming with some renomated experts in their specific field

- GPV Printca A/S (DK)

- Spacebel (B)

- Gaisler Research (SE)

- Spur Electron Limited (UK)

# Thank you for your attention

#### Author:

Koen Puimege – Verhaert Space – koen.puimege@verhaert.com Hogenakkerhoekstraat 9, 9150 Kruibeke, Belgium www.verhaert.com

7-8 March 2007