# The new SpaceWire compliant SMCS332SpW / SMCS116SpW ASIC

Dr Stephan Fischer Astrium GmbH

### **Outline**

- Introduction

- Motivation for the new SMCS

- SMCS332SpW New Features / Functions

- SMCS116SpW New Features / Functions

- Serial Transfer Universal Protocol (STUP)

- ASIC Facts

- Status

## Introduction

SMCS (Scalable Multi-channel Communication Sub-system)

- communication controller ASIC

- for space applications (radiation tolerant)

#### Tasks:

- hardware supported execution of major parts of the interprocessor protocol

- provide a fast interface to serial protocol

## Introduction – The current SMCS

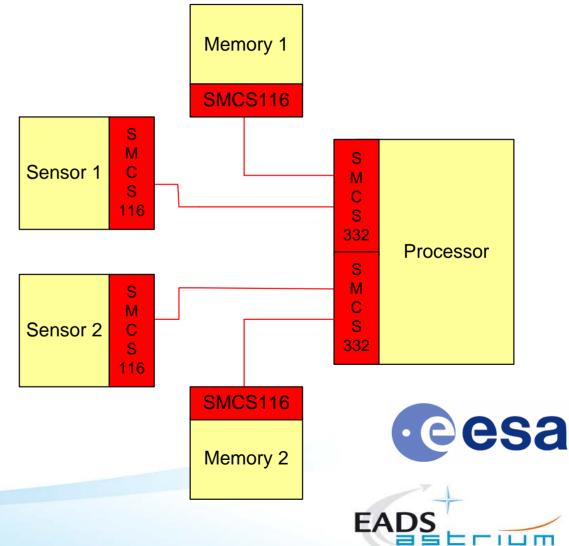

Application of SMCS ASICS

or SpaceWire network

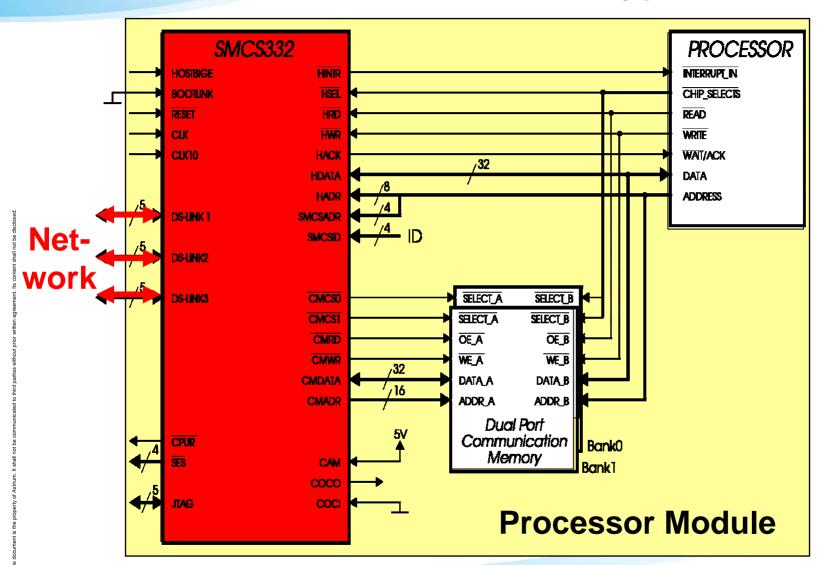

# SMCS332 in typical environment

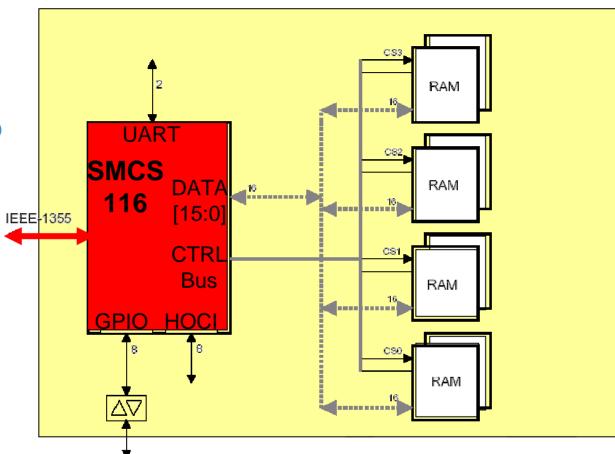

# **SMCSlite Applications**

SMCSlite connected to four banks of memory.

# **SMCSlite Applications**

SMCSlite as communication and system controller on an interface node consisting of an ADC and DAC.

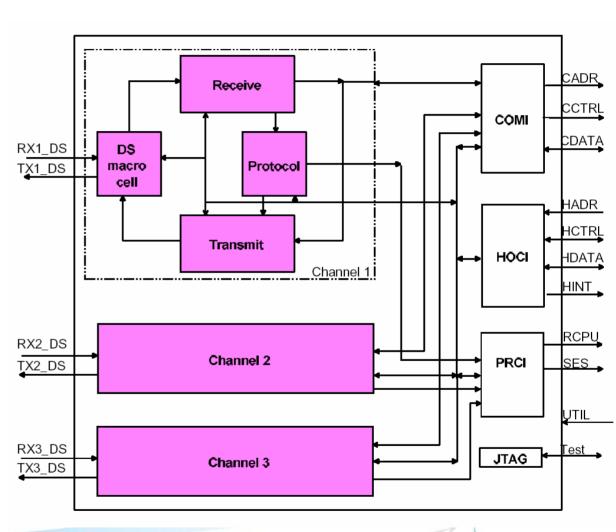

## Introduction - SMCS332

- 3 bi-directional link channels each with DS macro cell, receive, transmit section, protocol processing unit

- **COMI:** Com Memory Interface performs autonomous accesses to the communication memory

- HOCI: Host Control Interface gives r/w access to config reg and to DS channels for the CPU

- PRCI: Protocol Command

Interface

collects commands from

protocol units

- JTAG: Test Interface

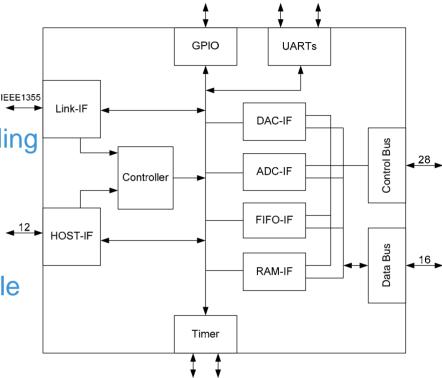

## Introduction SMCS116

#### **Link Interface:**

- •Interface to serial IEEE-1355 link

- control by Link

#### **Host Interface:**

parallel Interface for programming and controlling

#### ADC/DAC I/F:

•allows the read from ADC or write to DAC

#### **RAM IF:**

•4 banks (each 64K) of memory are addressable

#### FIFO I/F:

- •small internal FIFO (passive mode)

- •interface to external FIFO (active mode)

#### **GIPO:**

•General Purpose Interface, up to 24 I/Os

#### **UART:**

•2 independent UARTs

## **Motivation**

### Motivation for new SMCS SpW ASICs

- SMCS ASICs are often used communication controllers

- SpaceWire standard is becoming increasingly important

- ESA support

#### Requirements for the new SMCS SpW

- SpaceWire compliant (ECSS-E-50-12A, 24-Jan-2003)

- Pin compatible to existing SMCS332 / SMCS116

- not achieved completely

- correct known anomalies of the existing SMCS ASICs

- Goal: Backward compatibility concerning software

# Advantages of SpaceWire

#### New Features due to the SpaceWire Interface:

- The new SpaceWire interface is resistant against simultaneous switching on the data and strobe inputs

- It is 'hot' plug able (no master-slave situation has to be arranged)

- The SpaceWire Interface transmits / receives the new time code characters

# SMCS332SpW - New Functions

- Time code

- The SMCS332SpW can send Time Code characters

- The SMCS332SpW can be used as Time Code master

- New header field control bit

- more flexibility for packet generation

- Arbitrary packet length

- No restriction for the packet size for data reception/transmission over COMI

# SMCS116SpW - New Functions

- supports Serial Transfer Universal Protocol (STUP)

- enhanced 32-bit processor support

- the protocol engine was modified that it tolerates and executes commands of any length

- rest of a packet (read beyond 1 byte; write beyond 2 bytes) will be ignored

- Time code

- The SMCS116SpW can send Time Code characters

- The SMCS116SpW can be used as Time Code master

- FIFO, ADC and UART I/F improved

# Protocol handling

- for SpaceWire a new protocol is defined

- SMCS332SpW

- The SMCS332SpW directs all received data directly to the SW. Therefore, the SW has to handle the protocol and the SMCS332SpW is fully compliant to the new protocol.

- SMCS116SpW

- The new SMCS116SpW is able to handle data transfers without protocol and is compliant to the new SpaceWire protocol by using the STUP protocol.

## Serial Transfer Universal Protocol

#### Protocol format

| ◀                              | Destination Path<br>Address | Destination Path<br>Address                   | Destination Path<br>Address |

|--------------------------------|-----------------------------|-----------------------------------------------|-----------------------------|

| Destination Logical<br>Address | Protocol Identifier         | Source Logical<br>Address (Return<br>Address) | Data (one or more bytes)    |

| End of packet<br>marker (EOP)  |                             |                                               |                             |

- Destination Path Address bytes are optional

- This protocol structure can be used for all kinds of commands

# STUP in SMCS116SpW

## Command format for SMCS116SpW

| Destination Logical<br>Address | Protocol Identifier | Source Logical<br>Address (Return<br>Address) | Command/Address               |

|--------------------------------|---------------------|-----------------------------------------------|-------------------------------|

| Data (one or more bytes)       | Checksum            | Checksum                                      | End of packet<br>marker (EOP) |

- Byte 4 defines the command and address (write or read).

- Two Checksum bytes are appended, if checksum generation is enabled

- Source Logical address will be used as return address for read replies

## **ASIC Facts**

#### SMCS332SpW

- Radiation tolerant gate array technology from Atmel: MG2RT (0,5 µm)

- 196 pins

- power consumption: 1,7 W

- 3.3V version: 100MBit/s

- 5 V version: 200MBit/s

#### SMCS116SpW

- Radiation tolerant gate array technology from Atmel: MG2RT (0,5 µm)

- 100 pins

- power consumption: TBC

- 3.3V version: 100MBit/s

- 5 V version: 200MBit/s

## **ASIC Schedule**

#### SMCS332SpW

- Prototypes tested

- Prototype approval given

- ASIC available -> Atmel

#### SMCS116SpW

- Prototypes testing ongoing

- Prototype approval planned for end of March 07

- ASIC available in ~ Q3/07