| Doc. No.: |            | RTEMSSMP-FR-00 |         |  |

|-----------|------------|----------------|---------|--|

| Issue:    | 2          | Rev.:          | 1       |  |

| Date:     | 2015-03-20 | Page:          | 1 of 17 |  |

# **RTEMS SMP Final Report**

**Development Environment for Future Leon Multi-core**

Contract: 4000108560/13/NL/JK

# TABLE OF CONTENTS

| 1 INTRODUCTION                                                              | <u>. 3</u>  |

|-----------------------------------------------------------------------------|-------------|

| 1.1 Scope of the Document                                                   | <u>3</u>    |

| 1.2 Overview.                                                               |             |

| 1.3 Reference Documents                                                     | <u>.3</u>   |

| 2 ACTIVITY DESCRIPTION                                                      | 4           |

| 2.1 Introduction to the activity                                            |             |

| 2.2 Relation with other activities                                          | 4           |

| 2.3 About the consortium and work separation                                | 4           |

| 2.4 Main project goals and challenges                                       | <u>5</u>    |

| 2.5 Main activity steps and schedule                                        | . <u>.6</u> |

| 2.6 Main outputs                                                            | 7           |

| 2.7 Publications                                                            | 7           |

| 2.8 Main results                                                            | .7          |

| 3 WORK PERFORMED                                                            | 8           |

| 3.1 RTEMS SMP                                                               | 8           |

| 3.1.1 Initial RTEMS analysis and getting existing RTEMS SMP working on LEON | 8           |

| 3.1.2 Processor Set API                                                     |             |

| 3.1.3 SMP Scheduler extended with CPU affinity                              | <u>8</u>    |

| 3.1.4 RTEMS Atomic Layer and toolchain                                      | <u>10</u>   |

| 3.1.5 Capture Engine                                                        | <u>10</u>   |

| 3.1.6 Cache Manager SMP support                                             | <u>11</u>   |

| 3.1.7 LEON3 and NGMP BSPs                                                   |             |

| 3.1.8 LEON SMP development environment                                      |             |

| 3.2 Parallelisation library                                                 | <u>13</u>   |

| 3.2.1 Parallelisation survey                                                |             |

| 3.2.1.1 MCA MTAPI                                                           |             |

| 3.2.2 MCA Parallelisation Library implementation                            |             |

| 3.3 Demonstrator                                                            | <u>14</u>   |

| 4 CONCLUSIONS.                                                              | <u>17</u>   |

| Doc. No.: |            | RTEMSSMP-FR-00 |         |  |

|-----------|------------|----------------|---------|--|

| Issue:    | 2          | Rev.:          | 1       |  |

| Date:     | 2015-03-20 | Page:          | 3 of 17 |  |

# **1 INTRODUCTION**

#### 1.1 Scope of the Document

This document establish the final report for the RTEMS SMP activity.

This development centered around RTEMS SMP is part of an activity initiated by the European Space Agency under ESTEC contract 4000108560/13/NL/JK.

The work has been performed by Aeroflex Gaisler AB, Sweden and ASTRIUM SAS, France and On-line Application Research (OAR) Corporation, USA. Since the start of the activity Aeroflex Gaisler has changed name to Cobham Gaisler and ASTRIUM has changed name to Airbus Defence & Space.

#### 1.2 Overview

This document is partitioned in the following main sections,

- Activity description

- Work performed

- Conclusions

#### **1.3 Reference Documents**

- [GR712] "GR712RC Dual-Core LEON3-FT Development board", 2015-03-18, http://www.gaisler.com/index.php/products/boards/gr712rc-board

- [N2X] "GR-CPCI-LEON4-N2X NGMP functional prototype development board", 2015-03-18, http://www.gaisler.com/index.php/products/boards/gr-cpci-leon4-n2x

- [GR740] "GR740: The ESA Next Generation Microprocessor (NGMP)", 2015-03-18, http://microelectronics.esa.int/ngmp/

- [GRSIM] "GRSIM LEON MP simulator", 2015-03-18, http://www.gaisler.com/index.php/products/simulators/grsim

- [GAIA] "Gaia overview", 2015-03-18, http://www.esa.int/Our\_Activities/Space\_Science/Gaia\_overview

- [RTEMS] "RTEMS", 2015-03-18, http://www.rtems.org/

- [SIDMS] "SYSTEM IMPACT OF DISTRIBUTED MULTI CORE SYSTEMS (SIDMS) Final Report", 2011-11-22, http://microelectronics.esa.int/ngmp/SIDMS\_Final\_Report.pdf

- [MCA] "The Multicore Association", 2015-03-18, http://www.multicore-association.org/

- [MCAPI] "Multicore Association MCAPI", 2015-03-18, http://www.multicore-association.org/workgroup/mcapi.php

- [MTAPI] "Multicore Association MTAPI", 2015-03-18, http://www.multicore-association.org/workgroup/mtapi.php

- [CTF] "Common Trace Format (CTF)", 2015-03-18, http://www.efficios.com/ctf

- [BT] "Babeltrace", 2015-03-18, http://www.efficios.com/babeltrace

- [LTTNG] "Linux Tools Project LTTng Integration", 2015-03-18, http://eclipse.org/linuxtools/projectPages/lttng/

| Doc. No.: |            | RTEMSSMP-FR-002 |         |  |

|-----------|------------|-----------------|---------|--|

| Issue:    | 2          | Rev.:           | 1       |  |

| Date:     | 2015-03-20 | Page:           | 4 of 17 |  |

# 2 ACTIVITY DESCRIPTION

#### 2.1 Introduction to the activity

As multi-core processor devices have become more and more popular in the Real-Time Embedded Systems the space sector is bound to follow this trend too. ESA has launched several studies within the multi-core subject to analyse and explore possibilities and problems adapting new multi-core processor architectures. ESA is also active in developing future multi-core processors for space. The Next Generation Microprocessor (NGMP) activity will result in the GR740 ASIC, a quad-core LEON4 with a new bus architecture featuring for example a L2 cache.

The open source RTEMS Operating System is used in many European space missions. Several users in the space industry operates RTEMS in single-core configuration both on a ERC32 or LEON platform. The RTEMS community has started developing multi-core SMP support for RTEMS, it was started some years ago.

Studies have pointed out several problems in the existing multi-core software support. The objective of this activity is to improve the situation. Below is a brief summary of the objectives. The work tasks that resulted from these objectives are described in section 2.4.

- Extend the RTEMS OS to support SMP configurations of the NGMP and GR712RC multi-core achitectures. All changes to RTEMS are to be submitted to the RTEMS Community of acceptance into the main development stream

- Identify and port parallelisation libraries to exploit the parallelism of space applications

- Demonstrate the SMP support and programming model by parallelising a space application on multi-core LEON and compare the performance.

#### 2.2 Relation with other activities

The SIDMS study analysed hardware and software impacts with the introduction of multi-core processor architectures. Software techniques for multi-core programming were also analysed which is in direct interest of this activity. The study was completed in late 2011, the final report is available at [SIDMS].

The Next Generation Microprocessor (NGMP) ESA activity was started in 2009 and aims to develop a new quad core LEON4 processor chip, the GR740. The functional prototype of the NGMP design is used within this activity to test and demonstrate RTEMS SMP upon.

Another ESA activity with the same name and the same goals as this activity was kicked off some months before this activity. That activity was lead by Spacebel (Beligum). During the initial months of both activities discussions and meetings were held to synchronize the work to be performed.

#### 2.3 About the consortium and work separation

Cobham Gaisler AB (Sweden) has been the prime contractor in this activity, Airbus Defence & Space (France) was subcontractor and On-line Application Research (OAR) corporation (USA) has been an external service.

Cobham Gaisler is the developer of LEON3 and LEON4 fault tolerant processors and developer of the devices GR712RC [GR712] and LEON4-N2X NGMP prototype [N2X] targeted in this activity. Cobham Gaisler maintains the RTEMS Cross Compiler [RCC] SPARC environment used by many space projects. The RCC focuses on supporting RTEMS and its GNU GCC based toolchain for the LEON architecture.

|        | Doc. No.: |            | RTEMSSMP-FR-002 |         |  |

|--------|-----------|------------|-----------------|---------|--|

|        | Issue:    | 2          | Rev.:           | 1       |  |

| COBHAM | Date:     | 2015-03-20 | Page:           | 5 of 17 |  |

OAR Corporation is the founder and maintainer of the RTEMS operating system [RTEMS]. Besides being the main contributor to RTEMS and developers of the initial SMP support and scheduler design, OAR has previously developed the initial RTEMS SPARC port and BSP within an ESA activity.

Airbus Defence & Space has been involved as the prime contractor for several European spacecrafts and part of the SIDMS study that serves as input to this activity. Airbus DS built the Gaia Spacecraft [GAIA] and developed the computational heavy Video Processing Unit (VPU) software on Gaia. The VPU software is used to as a demonstrator for the activity.

Given the prior experiences of the contributors the work tasks are naturally separated within the consortium as follows:

- RTEMS platform independent SMP extensions, OAR corporation

- RTEMS SPARC and LEON specific SMP extensions and toolchain, Cobham Gaisler

- Space application parallelisation library requirements analysis, Airbus Defence & Space

- Parallelisation Library development, Cobham Gaisler

- Space application demonstrator development involving porting, parallelisation and performance measurements, Airbus Defence & Space

#### 2.4 Main project goals and challenges

The major goals of the activity are listed below. One can separate the goals into three sub categories:

- TASK1 RTEMS SMP

- Extend RTEMS OS SMP capabilities in the following areas

- Processor Set API

- Scheduler CPU affinity and user APIs

- Atomic library

- Trace support

- Extend the LEON support to run in SMP configuration on the GR712RC and LEON4-N2X (NGMP) platforms.

- All RTEMS changes are to be propagated upstreams to the RTEMS main repository.

- TASK2 Parallel Programming Models

- Parallel library survey study, to select appropriate parallelisation method

- Parallel library implementation

- TASK3 Demonstrator

- Port existing flight software demonstrator to RTEMS SMP

- Parallelisation of Demonstrator using above selected library

- Performance measurement against single-core of the demonstrator

The major resulting developments are summarized below:

- RTEMS

- Processor Set API

Doc. No.:

RTEMSSMP-FR-002

Issue:

2

Rev.:

1

Date:

2015-03-20

Page:

6 of 17

- Scheduler extended with CPU affinity capabilities

- SMP Priority Scheduler and Scheduler Pluggable API extended with CPU affinity

- POSIX Thread API extended

- RTEMS classic Thread API extended

- RTEMS Scheduler simulator and scheduler test-suite extended with SMP support

- Capture Engine extensions

- Support for tracing any function (without modifications to function) at link time

- SMP support with locking and real-time aspects in focus

- Generalized with variable sized records to support manually or automatically generated wrappers in the future

- RTEMS GNU Toolchain (GCC, BINUTILS, NEWLIB) tested, reviewed and updated upstreams. Focus on atomic support using LEON specific CAS instruction but also the toolchain as a whole

- Cache Manager extended with SMP support

- LEON3 and NGMP BSPs extended with SMP support. Tested on GR712RC and LEON4-N2X (NGMP) platforms.

- LEON environment: GDB-7.7.x support in GRMON2, automated RTEMS test-suite and GCC test-suite execution and reporting

- RTEMS kernel source build warnings have been reduced

- Parallelization library:

- Survey justifying that MTAPI is the preferred choice for the demonstrator

- MTAPI implemented for RTEMS SMP in an LEON environment

- MTAPI user's manual and test-suite

- Demonstrator

- Ported from single-core VxWorks PowerPC platform to RTEMS SMP LEON3/4 multi-core

- Parallelisation of the demonstrator using MTAPI

- Demonstrator task scheduling analysed and changed to take better advantage of CPU resources and performance figures collected and analysed.

#### 2.5 Main activity steps and schedule

The activity was planned as a 18 month activity with the four milestones listed below. The development defined by TASK1, TASK2 and TASK3 were scheduled to be mostly performed in parallel except for the integration of TASK1 into TASK2 and then into TASK3 the demonstrator.

- Kick off 2013-08-15

- PDR 2013-12-19

- CDR 2014-09-25

- FR 2015-03-27

### 2.6 Main outputs

The following items have been delivered within the activity:

- D11 RTEMS Features/change specification

- D12 RTEMS Test plan

- D13 RTEMS Test report

- D15 RTEMS user's manual

- D21 Parallelisation survey and trade-off justifications

- D22 MTAPI Parallelisation library user's manual

- D23 MTAPI Parallelisation library test report

- D31 SMP Demonstrator Architectural Document

- D32 SMP Demonstrator Test report

- FR Final Report (this document)

- SW11 RTEMS source code and patches against identified version

- SW12 RTEMS Test scripts/program

- SW21 Parallelisation library

- SW31 SMP Demonstrator source code

The output of SW11 and SW12 has also been submitted and included in the main official RTEMS repository.

#### 2.7 Publications

The work performed within this activity has been published in the following papers and presented at the DASIA conferences 2014 and 2015:

# RTEMS SMP and MTAPI for Efficient Multi-Core Space Applications on LEON3/LEON4 Processors

Daniel Cederman, Daniel Hellström, Joel Sherrill, Gedare Bloom, Mathieu Patte, Marco Zulianello

#### **RTEMS SMP for LEON3/LEON4 Multi-Processor Devices**

Daniel Cederman, Daniel Hellström, Joel Sherrill, Gedare Bloom, Mathieu Patte, Marco Zulianello

#### 2.8 Main results

All code developed for RTEMS Operating System, BSPs, documentation, tests and toolchain has been submitted upsteams to respective project repository and is freely and publicly available. This ensures that the work developed within this activity is available and will be reused in future ESA space missions.

The parallelisation survey justified the development of MTAPI task management API. The MTAPI implementation, user's manual and test-suite are part of the SW21 deliverable.

The porting of the demonstrator shows that the RTEMS SMP on LEON3/4 multi-core devices is usable in practise for space applications. It also shows one approach to exploit the performance in current and

| Doc. No.: |            | RTEMSSMP-FR-002 |         |  |

|-----------|------------|-----------------|---------|--|

| Issue:    | 2          | Rev.:           | 1       |  |

| Date:     | 2015-03-20 | Page:           | 8 of 17 |  |

future multi-core LEON devices. The performance results and lessons learnt are part of the D32 document and summarised in this report.

The activity has been performed within the time schedule of 18 months.

# 3 WORK PERFORMED

The development work of the project has been in line with the proposed of work. There was an initial minor delay after Kick-off within the RTEMS sub task where a broader discussion about how to extend RTEMS SMP had to be settled first in collaboration with another parallel ESA RTEMS SMP activity. As described below the atomic layer development planned switched focus towards reviewing and testing the toolchain now that RTEMS rely on the compiler (C11) for atomic support. The three teams were able to work in parallel most of the time hence the time plans could be met. The specification of new features was developed by one team in parallel with another team porting/analysing existing SMP features and the third team porting the demonstrator to single-core and so on.

The following sub sections describe the major work performed within the activity. The first part was focused on developing the software support for RTEMS SMP and toolchain, whereas the last two parts can also be seen as a system test and performance study.

# 3.1 RTEMS SMP

The following sub sections described the major development work performed related to RTEMS SMP and the RTEMS toolchain.

# 3.1.1 Initial RTEMS analysis and getting existing RTEMS SMP working on LEON

During the first months of the activity the existing SMP support in RTEMS LEON BSPs were analysed. Before the activity started problems had been identified related to the LEON BSP initialisation and SMP. Several LEON BSP initialization and SMP issues were fixed and most SMP tests in the RTEMS testsuite was successfully executed. During the boot analysis it was discovered that the platform independent start-up code had some problems, cache inconsistencies could be seen and the test results of the RTEMS test-suite was in some cases not reliable. The discoveries were feedback to community and the specification.

# 3.1.2 Processor Set API

In order to have one common way to describe a set of processors within the RTEMS kernel it was proposed to define and develop a Processor Set API. The API was defined and implemented at the start of the activity to make it available to other code as early as possible. Changes were made to NEWLIB and RTEMS. The interface is located in NEWLIB sources at *libc/sys/rtems/sys/cpuset.h* and installed in *rtems/score/cpuset.h* among the RTEMS header file. The *spcpuset01* tests was added to the RTEMS test-suite.

The Processor Set API was used in all the developed RTEMS code where appropriate.

#### 3.1.3 SMP Scheduler extended with CPU affinity

The ability to control which CPU or set of CPUs a task is allowed to execute on is an important feature in a SMP Operating System. For application developers is may be vital in cache optimization, controlling the task scheduling, avoiding locking between tasks, load balancing, porting existing single-core code to SMP etc. It is also a fundamental requirement for many parallelisation libraries.

|        | Doc. No.: |            | RTEMSSM | P-FR-002 |

|--------|-----------|------------|---------|----------|

|        | Issue:    | 2          | Rev.:   | 1        |

| COBHAM | Date:     | 2015-03-20 | Page:   | 9 of 17  |

Existing user APIs used to control a task's CPU affinity was analysed. The two Task user APIs in RTEMS, the RTEMS classic API and POSIX thread API, where extended with the ability to read and write the current CPU affinity settings of a task. The following CPU affinity directives were added to the POSIX Affinity API in *pthread.h*:

```

int pthread attr setaffinity np(

pthread_attr_t *__attr,

size_t __cpusetsize,

const cpu_set_t *__cpuset

);

int pthread_attr_getaffinity_np(

const pthread_attr_t *__attr,

size_t __cpusetsize,

cpu_set_t *__cpuset

);

int pthread setaffinity np(

pthread_t __id,

size_t __cpusetsize,

const cpu set t * cpuset

);

int pthread getaffinity np(

const pthread t id,

size t cpusetsize,

cpu set t * cpuset

);

int pthread getattr np(

pthread t id,

pthread_attr t * attr

);

```

The following functions were added to the classic RTEMS API, declared in *rtems/rtems/tasks.h*:

The RTEMS pluggable scheduler API was extended with CPU affinity support. It is an option for a scheduler implementation to make use or ignore the CPU affinity properties. The existing RTEMS *Deterministic Priority SMP Scheduler* was extended to support CPU affinity. The new scheduler is named the *Deterministic Priority Affinity SMP Scheduler*.

The RTEMS test-suite was extended with new tests for the new scheduler. The following tests were added: *smpaffinity01*, *smpschedaffinity01*, *smpschedaffinity02*, *smpschedaffinity03*, *smpschedaffinity04*, *smpschedaffinity05*, *smppsxaffinity01* and *smppsxaffinity02*. A test-suite verifying the scheduler algorithm was developed using the RTEMS Scheduler Simulator framework. The simulator was extended to support SMP and several scheduler scenarios was described to trigger specific task scheduling cases. The scheduler simulator could successfully be used to describe scenarios hard to trigger in real hardware.

| Doc. No.: |            | RTEMSSMP-FR-002 |          |  |  |

|-----------|------------|-----------------|----------|--|--|

| Issue:    | 2          | Rev.:           | 1        |  |  |

| Date:     | 2015-03-20 | Page:           | 10 of 17 |  |  |

# 3.1.4 RTEMS Atomic Layer and toolchain

The atomic layer in an operating system provides platform independent support for various atomic operations. It is often used to implement SMP primitives such as semaphores and protecting structures. It was identified as an important piece in the SMP support. Adding LEON support to the atomic layer using the LEON3/4 CAS instruction was proposed. However before the activity kicked off the RTEMS project selected to rely on the C11 standard for platform independent atomic operations. With GCC-4.8.2 and GCC-4.9 released in May 2014 CAS support was introduced in the LEON backend. The goal within the activity then became instead to review, test and update the atomic CAS support of the LEON backend used to implement atomic operations and locking primitives of RTEMS SMP.

The GCC test-suite was interfaced to the LEON environment using GRMON2 Tcl scripts to support automated execution on GR712RC and LEON4-N2X targets and collecting execution results. Running the GCC test-suite is as usual a very time consuming effort but paid off. In the same context of LEON backend atomic support the machine instructions generated and the execution of parts of RTEMS SMP were analysed. Issues were found the GCC LEON backend and in the RTEMS spin-lock implementation. The issues found were propagated to the RTEMS community and patches were submitted to the GCC mainline repository.

To gain an overall bigger trust in the GCC-4.9.2 compiler the compiler was tested in an Linux-3.10 environment. Linux was selected due to its huge software support and our previous experiences. Various common benchmarks and test-suites were compiled and executed on the LEON4-N2X in SMP configuration. The performance figures showed an overall minor improvement since GCC-4.4.6, and in two specific cases a performance drop. Performance drops were analysed. At first it was believed to be a GCC SPARC backend issue which could signal a significant problem. Later it was found to be platform independent introduced around GCC-4.6 and of minor importance. The GCC maintainers decided to fix the problem in the mainline GCC rather than back porting the fix to the GCC-4.9 branch. The core-utils test-suite found a LEON4-N2X hardware MMU problem which was fed back to the NGMP CPU developer team and fixed for the GR740. Overall the GCC-4.9.2 compiler for LEON was found very stable.

# 3.1.5 Capture Engine

In order to overview and analyse events and in a complex SMP environment a Trace Library was to be developed. The existing RTEMS Capture Engine was analysed and discussed within the community. The Capture Engine was to a great extent redesigned to support a number of new features, SMP support and to ensure that the trace recording had a minimal effect on the running application.

The starting point of the project were that the existing Capture engine was merely undocumented, no tests were present and SMP support fundamentally not working by design. It was concluded by the community that having two trace solutions within the RTEMS project was not optimal. Therefore the Capture Engine was redesigned inheriting features that was required to work. The community determined the path for the future RTEMS tracing capabilities which were explored during the activity. The work performed can be seen as an important step implementing the future plans. The future plans involve inserting functionality at link time into any function's entry and exit. It could be achieved automatically by extracting function prototype argument and return type information from a second source, for example the debug information or custom information. That information could serve as input for an automatically generated wrapper called at function entry/exit. The wrapper is responsible for doing logging and calling the original function to perform the expected functionality. Functions can be wrapped using the GNU LD linker's –*wrap=symbol* command line switch.

The focus were put on the capture engine design itself and not so much the environment and wrapper generation. The following major pieces of the Capture Engine were developed:

SMP support

|        | Doc. No.: |            | RTEMSSMP-FR-00 |          |  |

|--------|-----------|------------|----------------|----------|--|

| CODUOM | Issue:    | 2          | Rev.:          | 1        |  |

| COBHAM | Date:     | 2015-03-20 | Page:          | 11 of 17 |  |

|        |           | -          |                |          |  |

- Support for variable sized record. This is a fundamental requirement to support tracing functions with different input argument types and count

- Support for command line interface were maintained and improved

- Real-time performance improvements were implemented by,

- Redesign to removing dynamic memory in trace recording execution path

- One capture engine per processor to minimise SMP locking

- Capture record buffer read out partly redesigned

- RTEMS test-suite extended with new tests: capture01, smpcapture01 and smpcapture02

The new Capture Engine interface is declared in the *rtems/capture.h* header file.

A proof-of-concept SMP application was developed to test and demonstrate the usefulness of the Capture Engine on a SMP system. The MTAPI task activity was traced by the capture engine and transferred over Ethernet NFS by a low-priority task. The resulting logs were described by meta data files according to the Common Trace Format (CTF) [CTF]. The trace could then be viewed and searched using the command line *babeltrace* [BT] tool or graphically using the LTTng [LTTNG] Eclipse plug-ins. A couple of LTTng plug-in Java classes were extended accordingly to describe the MTAPI objects and extract and display MTAPI specific data recorded. See the PC screen shot below captured from a LEON4-N2X board running MTAPI on RTEMS SMP.

| 3 🔻 🔛 险 💁 🗣 😂 🖭 🧃                           | • ∲ • \$ \$ <b>•</b> • • |       |                    |                        |                     |                     |                                                                                                             |                      | Quick Ac          | ccess 📑 😰 🔁 Reso       |

|---------------------------------------------|--------------------------|-------|--------------------|------------------------|---------------------|---------------------|-------------------------------------------------------------------------------------------------------------|----------------------|-------------------|------------------------|

| Project Explorer 🛿 🔍 🗖                      | 🗆 Statistics ជ           |       |                    |                        |                     | 🗉 data2 📔 data3 🛱   |                                                                                                             |                      |                   |                        |

| = 🛸 🔻 🙆                                     | Slobal - data3           |       |                    |                        |                     | Timestamp           | Source                                                                                                      | Туре                 | File              | Content                |

| 😂 Tracing                                   | Level                    | Even  | ts total Events in | selection              |                     | ⇒ <filter></filter> | <filte< td=""><td>r&gt; <filter></filter></td><td><filter></filter></td><td><filter></filter></td></filte<> | r> <filter></filter> | <filter></filter> | <filter></filter>      |

|                                             | 🖬 data 3                 |       | 13,170             | 11,057                 |                     | 01:00:04.829 299 00 | 0 0                                                                                                         |                      |                   |                        |

|                                             | Event Types              |       | 13,170             | 11,007                 |                     | 01:00:04.829 307 00 | 0 0                                                                                                         |                      | trace             |                        |

| • 📴 data3                                   | dispatch enter           | 36 %  | 4,749 36.3 %       | 4,019                  |                     | 01:00:04.829 317 00 | 0 0                                                                                                         | dispatch_exit        | trace             |                        |

| <ul> <li>MTAPI Analysis</li> </ul>          | dispatch exit            |       | 4,749 36.3 %       | 4.018                  |                     | 01:00:04.829 325 00 | 0 0                                                                                                         | dispatch_enter       | trace             |                        |

| Test a builtin XML module fil               | 🔣 mtapi enter            |       | 1.188 9.1 %        | 1,007                  |                     | 01:00:04.829 382 00 |                                                                                                             |                      | trace             |                        |

| <ul> <li>Tmf Statistics Analysis</li> </ul> | 🔣 mtapi_exit             |       | 1,184 9.1 %        | 1,007                  |                     | 01:00:04.829 385 00 |                                                                                                             |                      |                   |                        |

| Statistics                                  | mtapi_wait_all_enter     | 2.2 % | 297 2.2 %          | 251                    |                     | 01:00:04.829 390 00 |                                                                                                             |                      | trace             |                        |

|                                             | mtapi wait all exit      | 2.2 % | 297 2.2 %          | 251                    |                     | 01:00:04.829 398 00 | 0 0                                                                                                         | dispatch_exit        | trace             |                        |

|                                             | Tick enter               | 2.6 % | 353 2.2 %          | 252                    |                     | 01:00:04.829 497 00 | 0 0                                                                                                         | dispatch_exit        | trace             |                        |

|                                             | tick exit                | 2.6 % | 353 2.2 %          | 252                    |                     | 01:00:04.829 732 00 |                                                                                                             | dispatch_exit        | trace             | nodeid=2, pad=0, jobio |

|                                             |                          | 0     |                    |                        |                     | 01:00:04.829 741 00 |                                                                                                             | mtapi_wait_all_exit  | trace             |                        |

|                                             |                          |       |                    |                        |                     | 01:00:04.829 747 00 |                                                                                                             | mtapi_exit           | trace             |                        |

|                                             |                          |       |                    |                        |                     | 01:00:04.829 750 00 | 0 0                                                                                                         | dispatch_enter       | trace             |                        |

|                                             |                          |       |                    |                        |                     | 01:00:04.829 753 00 |                                                                                                             | dispatch_enter       | trace             |                        |

|                                             |                          |       |                    |                        |                     | 01:00:04.829 755 00 |                                                                                                             | dispatch_enter       | trace             | nodeid=1, pad=0, jobic |

|                                             |                          |       |                    |                        |                     | 01:00:04.829 758 00 |                                                                                                             | mtapi_exit           | trace             |                        |

|                                             |                          |       |                    |                        |                     | 01:00:04 229 761 00 |                                                                                                             | mtapi_exit           | trace             |                        |

|                                             |                          |       |                    |                        |                     | 01:00:04.829 764 00 | 0 0                                                                                                         | mtapi_exit           | trace             | nodeid=1               |

|                                             |                          |       |                    |                        |                     | 01:00:04.830 008 00 | 0 0                                                                                                         | tick_enter           | trace             |                        |

| Outline 😫 🗐 Task Lis 📮 🗖                    |                          |       |                    |                        |                     | 01:00:04.830 013 00 |                                                                                                             | tick_exit            | trace             |                        |

|                                             |                          |       |                    |                        |                     | 01:00:04.830 036 00 |                                                                                                             | mtapi_enter          | trace             |                        |

| \$ v                                        |                          |       |                    |                        |                     | 01:00:04.830 041 00 | 0 0                                                                                                         | dispatch_exit        | trace             |                        |

| outline is not available.                   |                          |       |                    |                        |                     | 01:00:04.830 048 00 | 0 0                                                                                                         | mtapi_enter          | trace             | nodeid=2               |

|                                             |                          |       |                    |                        |                     | 01:00:04.830 052 00 | 0 0                                                                                                         | dispatch_exit        | trace             |                        |

|                                             |                          |       |                    |                        |                     | 01:00:04.830 055 00 | 0 0                                                                                                         | mtapi_enter          | trace             | nodeid=0               |

|                                             |                          |       |                    |                        |                     | 01:00:04.830 060 00 |                                                                                                             | mtapi_enter          | trace             | nodeid=3               |

|                                             |                          |       |                    |                        |                     | 01:00:04.830 065 00 |                                                                                                             | dispatch_exit        | trace             | nodeid=3, pad=0, jobio |

|                                             |                          |       |                    |                        |                     | 01-00-04 830 069 00 | ni o                                                                                                        | dispatch enter       | trace             | nodeid=1 nad=0 iobic   |

|                                             | MTAPI View 83            |       |                    |                        |                     |                     |                                                                                                             |                      | (二) (合)           | 5 5 6 4 4 a a          |

|                                             | 1970 Jan 01              |       | 01:00:             | 04.578000              | 01:00:04.578500     | . C                 | 1:00:04.57                                                                                                  | 9000                 |                   | 01:00:04.579500        |

| E                                           | a data3                  |       |                    |                        |                     |                     |                                                                                                             |                      |                   |                        |

|                                             | Node 0                   | (     |                    | Job 3 Job 8            | Job 9 Job 1 Waiting |                     |                                                                                                             | Job 3 Job 8 Job 9    |                   | Job 12                 |

|                                             |                          | 1     |                    | job 1 jok<br>Job 0 Job | 5 Job 12            |                     | _                                                                                                           | ob 2 Job 4           | Job 10            |                        |

|                                             |                          |       |                    | lob 2 lob 4            | 10b 7               |                     |                                                                                                             | Job 0 Job 3          |                   |                        |

|                                             |                          |       |                    |                        |                     |                     |                                                                                                             |                      |                   |                        |

|                                             |                          |       |                    |                        |                     |                     |                                                                                                             |                      |                   |                        |

|                                             |                          |       |                    |                        |                     |                     |                                                                                                             |                      |                   |                        |

|                                             |                          |       |                    |                        |                     |                     |                                                                                                             |                      |                   |                        |

|                                             |                          |       |                    |                        |                     |                     |                                                                                                             |                      |                   |                        |

|                                             |                          |       |                    |                        |                     |                     |                                                                                                             |                      |                   |                        |

|                                             |                          |       |                    |                        |                     |                     |                                                                                                             |                      |                   |                        |

Illustration 1: LTTng showing RTEMS Capture Buffer of a LEON4-N2X MTAPI system

Single-core and multi-core SMP tests were added to the RTEMS test-suite. By making minor modifications to the LEON BSP interrupt handling code layout it was successfully demonstrated that also interrupt services routines can be traced.

# 3.1.6 Cache Manager SMP support

After the initial analysis of RTEMS and start-up boot code it was clear that cache inconsistencies could be experienced when one processor modifies instructions. Self modifying code typically is used during

|        | Doc. No.: |            | RTEMSS | MP-FR-002 |

|--------|-----------|------------|--------|-----------|

|        | Issue:    | 2          | Rev.:  | 1         |

| COBHAM | Date:     | 2015-03-20 | Page:  | 12 of 17  |

installing trap handlers. This occurs typically during boot when installing basic services, interrupt initialisation/registration and when the user installs custom error trap handlers.

The RTEMS Cache Manager was extended with SMP support and a test was added to the RTEMS SMP test-suite. The Cache Manager was extended to use Inter Processor Interrupts (IPI) to signal cache flush requests on another processor. A IPI interrupt handler was implemented to execute the request. Processors are described using the Processor Set API primitives.

# 3.1.7 LEON3 and NGMP BSPs

During the initial analysis and debugging effort of RTEMS start-up code and the LEON3 and NGMP BSPs the problems found were fixed and patches submitted. After that the boot was successful and most RTEMS tests from the SMP test-suite was working.

Driver wise the Interrupt controller, Timer and UART console drivers were of primary interest. They were examined, tested primarily using the RTEMS test-suite, SMP problems were fixed and drivers were extended to SMP where required support was missing. New per CPU interrupt controller macros were introduced in the BSP and support interrupt CPU affinity was added to the BSP. Interrupts can now be assigned to any processor at compile-time by the user. The user overrides a weak interrupt to CPU number table with a custom table.

Since all code developed were updated against the RTEMS mainline sources that changed often it was essential to build tests, execute tests, check results and create a test report in an automatic fashion, and regularly. The RTEMS test-suite was automated for the LEON environment using GRMON2 Tcl scripts. The test-suite was executed on both the targeted GR712RC and LEON4-N2X development boards. As found in the early analysis some of the tests in the test-suite could fail undetected when performing a standard check for start and end markers in the console output. To improve the situation it was decided to look at a test's exit code.

To allow the exit code to be propagated to the hardware debugger or bootloader the SMP shutdown mechanism was reviewed. Some issues apart from the exit code propagation was found. The SMP shutdown mechanism was partly redesigned both on a platform independent but mostly SPARC specific level. The test-suite execution result summary showed that about 10% of the tests return other exit codes than (5,0) which is the standard exit code. It made it hard to rely on the exit code to determine if a test failed or not. However it still served as a valuable input when manually verifying the execution results and failures were detected based on the exit code during the activity.

During the last part of the activity some optimizations were implemented to RTEMS SPARC register window overflow and underflow trap handling and SPARC interrupt level enabling and disabling trap handling.

# 3.1.8 LEON SMP development environment

In parallel to the RTEMS SMP development the SMP support of the LEON development environment was overviewed. Some of the major discoveries are listed below:

- Certain discoveries The new GCC-4.9 based toolchain required by RTEMS SMP generated DWARF-2 debugging information that was not fully compatible with older GDB version supported by GRMON. The default debugging information format of GCC-4.9 is DWARF-3 which was not either supported by older GDB versions.

- GRMON did not support SMP or RTEMS-4.11 thread information

- GRMON issues when it came to restarting an SMP application and exit code

The ability to do C source level debugging is very important and considered a fundamental requirement. The solution to the above issues were developed and tested:

- GDB-7.7.x support in GRMON2

- SMP and bare metal thread model support in GRMON2

- RTEMS-4.11 and RTEMS-4.11 SMP task information support in GRMON2

- Found GRMON2 multi-core issues fixed and exit code can now be propagated to user shell

#### 3.2 Parallelisation library

The following sub sections described the major development work performed related to the parallelisation library.

#### 3.2.1 Parallelisation survey

The SIDMS study final results showed that the most interesting use case for multi-core processors within the space segment is scientific payload data processing applications. The survey focuses on the multi-core issues and needs of payload applications. To compare different available parallelisation techniques a set of criterion important for space applications in general and payload processing application specifically was identified based on earlier studies and experiences. Aspects taken into account are summarized below,

- the overall parallelisation scheme

- task synchronization method(s)

- task dispatching techniques supported

- support for hardware accelerators and multi-core systems

- compiler dependability and modifications required

- execution determinism

- software qualification

- adaptation complexity

A couple of widely used parallelisation libraries that were initially considered interesting given the context were selected for the analysis. The following libraries were selected and part of the analysis,

- OpenMP

- Intel Cilk plus

- Multicore Association (MCA) APIs [MCA]

- POSIX Threads

The libraries were scored based on the summary of all above described criterion. The results justified that the Multicore Association APIs was selected. The scores of MTAPI [MTAPI] were overall high apart from the adaptation complexity.

#### 3.2.1.1 MCA MTAPI

The Multicore Association distributes the open specification MCAPI and MTAPI. The MCAPI [MCAPI] specification provides platform independent communication services based on message passing over any communication channel. Whereas the MTAPI specification provides task management services, some of which are common in all task-based programming libraries. This includes spawning tasks and waiting for tasks to be completed. One difference between MTAPI and other libraries, however, is in its support for heterogeneous platforms.

When spawning a task one does not provide a function pointer. This would not work when communicating between different types of hardware architecture. Instead an identifier is used that corresponds to some abstract work. In MTAPI this identifier is called a *job*. A processing node can register an *action* for a specific job. An action is a software or hardware function that the node can execute to perform the abstract work specified by the job. Spawning a task thus consists of creating a

task object with input arguments for the task and a job identifier. The MTAPI scheduler then decides which node, out of the ones that have registered an action for the job, should perform the actual task, using its registered action. This system allows different nodes in the system to perform operations in the manner that is the most efficient for that hardware. It also allows for work sharing between different types of hardware, since there is no exchange of function pointers.

# 3.2.2 MCA Parallelisation Library implementation

MCAPI and MTAPI has been design such that a MTAPI implementation can rely on MCAPI for a platform independent and scalable communication service between processor cores or processor devices. Both specifications were analysed in parallel with the ongoing analysis of the demonstrator application requirements. At first it was determined only a minor number of MCAPI services was required, mainly to support MTAPI communication. During the development process it became evident that it was beneficial to make a smaller more efficient custom communication solution for the implementation of MTAPI. The communication in this case is limited to on-chip communication between processor cores using shared memory resources and services to generate interrupt for signalling.

The MTAPI implementation was written in C and performs no dynamic memory allocation. The maximum number of jobs, groups, active tasks, action and queues, are all specified at compile time. To lower latencies, all common functions, such as spawning and dispatching tasks, have been written in a lock-free manner. Less time critical operations, such as the creation and deletion of queues, are instead blocking. A *node* is defined as a RTEMS task with affinity to a unique core. The nodes communicate via shared data structures. A centralized scheme is used for load balancing, where nodes ask a common data structure for new applicable tasks when they have finished their previous work.

Most MTAPI services were developed and unit tested by implementing a test-suite supported by coverage analysis. The coverage results were close to full coverage at 92.5%. A system level test was developed to mimic the expected task scheduling behaviour of the demonstrator. It was developed in order to verify the MTAPI functionality in an RTEMS SMP LEON multi core environment prior to running the demonstrator. This turned out to be a successful approach saving a lot of time in the project.

Performance tests performed showed that creating a MTAPI group, starting 16 tasks on other CPU cores and waiting for the group execution completes took in average about 50us on a LEON4-N2X 150MHz. This results in an about 300KHz MTAPI task start and join rate. The tasks did not perform any work.

# 3.3 Demonstrator

The demonstrator consists of a flight-tested space payload software, the Gaia Video Processing Unit (VPU) application. The original software was designed to run on a single-core PowerPC processor mounted on a Maxwell SCS750 board (ITAR) using VxWorks. The original VPU software consists of about 32000 lines of code.

The major development work performed related to the Gaia VPU application demonstrator are summaried below.

- Ported to LEON architecture and RTEMS-4.10 single-core configuration

- Ported to RTEMS-4.11 SMP and parallelisation using MTAPI

- Analysed and after restructured software to optimize task scheduling to better utilize the processor cores present.

- Measured and compared performance in different hardware and software configurations

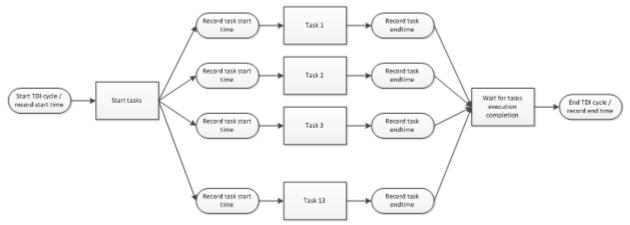

The VPU software is structured as a large software pipeline made of several relatively independent processing functions. To parallelise the application, these functions were initially grouped into 13 tasks that works on independent data sets and thus can be executed concurrently. Using MTAPI these tasks

|        | Doc. No.: |            | RTEMSS | MP-FR-002 |

|--------|-----------|------------|--------|-----------|

|        | Issue:    | 2          | Rev.:  | 1         |

| COBHAM | Date:     | 2015-03-20 | Page:  | 15 of 17  |

are all scheduled concurrently once per Time Delayed Integration (TDI) cycle. The cycle frequency is around 1KHz. The duration of each task was recorded for each TDI cycle using a high resolution timer.

The parallelisation of the application was found to be straightforward. Initially the performance was poor. To gain understanding on what was the limiting factor the actual time spent in the processing tasks were measured by recording the start and end time of tasks. How well the application was parallelised could this way be quantified and compared between different hardware and software configurations. It was concluded that processors were idling at certain times waiting on other tasks to complete their computations.

Illustration 2: Task execution flow graph

The application code was restructured into 16 tasks. By splitting the longest executing tasks into smaller parts the work load could be spread more evenly between cores.

| Board     | CPU core clock speed | Memory type and speed     | Memory timings               |

|-----------|----------------------|---------------------------|------------------------------|

| LEON4-N2X | 150 MHz              | 64-bit DDR SDRAM @ 300MHz | Col 10, ref 7.8us, trfc 82ns |

| LEON4-N2X | 200 MHz              | 64-bit DDR SDRAM @ 300MHz | Col 10, ref 7.8us, trfc 82ns |

| GR712RC   | 48 MHz               | 32-bit SDR SDRAM @ 48MHz  | Col 10, CAS 2, ref 7.8us     |

| GR712RC   | 80 MHz               | 32-bit SDR SDRAM @ 80MHz  | Col 10, CAS 2, ref 7.8us     |

The below table shows the hardware configurations for which the demonstrator was run.

Table 1: Test hardware configurations

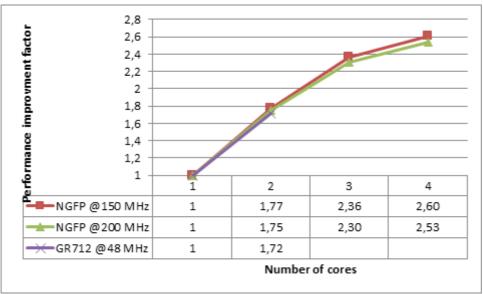

The LEON4-N2X at 150MHz achieved the highest performance factors. The performance scaled well up to two cores (1.77x) and three cores (2.36x), but gained little going up to four cores (2.60x). The GR712RC performance improvement utilising both cores was 1.72x. The dual-core performance of the GR712RC per MHz was about 13% lower compared to LEON4-N2X running at 150MHz.

| Doc. No.: |            | RTEMSSMP-FR-002 |          |

|-----------|------------|-----------------|----------|

| Issue:    | 2          | Rev.:           | 1        |

| Date:     | 2015-03-20 | Page:           | 16 of 17 |

Illustration 3: Performance improvement factors with number of cores used (higher is better)

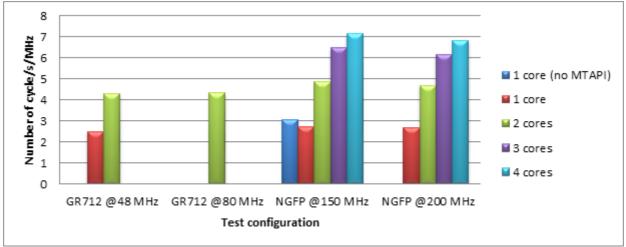

After normalizing the number of TDI cycles with the CPU frequency one can see how performance scales between the configurations.

Illustration 4: Number of TDI cycles per second and per MHz (higher is better)

The overhead caused by MTAPI+RTEMS was measured to about 12.5% of the overall execution time. The figure was calculated by comparing the application in a RTEMS-4.10 single-core configuration to a MTAPI parallelised application in a RTEMS-4.11 SMP single-core configuration.

The L2 cache hit ratio of the LEON4-N2X was measured using the L4STAT unit. GRMON periodically read the cache hit/miss/access statistical counters. The average L2 cache hit ratio was measured to 96.5%.

| Doc. No.: |            | RTEMSSMP-FR-002 |          |

|-----------|------------|-----------------|----------|

| Issue:    | 2          | Rev.:           | 1        |

| Date:     | 2015-03-20 | Page:           | 17 of 17 |

# 4 CONCLUSIONS

This activity has resulted in that the SMP support of RTEMS on the LEON3 and NGMP BSPs is working and usable in practise. The SMP scheduler and BSP interrupt handling now supports CPU affinity. It makes it easier to adopt RTEMS SMP and the fundamental pieces are in place for SMP applications. The new LEON toolchain for RTEMS has been extensively tested building a large confidence. The LEON development environment now supports RTEMS SMP.

All code developed for RTEMS Operating System, BSPs and toolchain has been submitted upsteams to respective project repository and is freely and publicly available. It will be part of the next stable RTEMS release RTEMS-4.11. This ensures that the software developed are available and possible for reuse in future ESA space missions.

Existing parallelisation techniques were analysed to find that the MTAPI task management library meets space payload application requirements best. The MTAPI specification was implemented for RTEMS SMP on LEON. The MTAPI library can be used to help existing and new space software to exploit multi-core processor resources using a platform-independent API.

The Gaia VPU application was successfully ported from the single-core PowerPC VxWorks environment to RTEMS SMP on the GR712RC and LEON4-N2X platforms. By using RTEMS SMP CPU Affinity Scheduler together with the MTAPI library the application could effectively be parallelised and partly restructured to improve the performance significantly. All the developed pieces were integrated and it was demonstrated that they worked together by verifying the correct execution and output. Various performance figures were measured in different configuration using the extensive performance instrumentation framework of the VPU Gaia test platform. Performance was compared between different hardware and software configurations.

The performance increase of the parallelised demonstrator scaled well up to three CPU cores. On a LEON4-N2X in a quad core configuration it resulted in a speed up of about 2.6 times the single-core performance. By measuring the subtask start and exit times it could be concluded that only 273% of the actual time was spent in the calculation algorithm. The other time spent is overhead and waiting for other CPUs to complete their work load. This leaves room for performance improvements, however could require a more fine grained parallelisation of the space application and that MTAPI might not be an optimal solution in that case. It shows that a payload application like the demonstrator can be parallelised using MTAPI in a couple of months to gain a significant performance improvement over the single-core system.

Based on the NGMP prototype performance results and assuming that the future GR740 runst at 250MHz using SDR SDRAM memory the GR740 would be fast enough to run the existing VPU application. Comparing against the reference PowerPC SCS750, Airbus Defence & Space concludes that the GR740 could be a future candidate to replace the PowerPC for this kind of application. Its notable that the power efficiency of the GR740 in this case is much better, approximated to consume only one third of the power required today.