## Assembly Language Syntax

The notations given in this section are taken from Sun's SPARC Assembler and are used to describe the suggested assembly language syntax for the instruction definitions explained on page 5.

Understanding the use of type fonts is crucial to understanding the assembly language syntax in the instruction definitions. Items in typewriterfont are literals, to be entered exactly as they appear. Items in *italic font* are metasymbols that are to be replaced by numeric or symbolic values when actual assembly language code is written. For example, *asi* would be replaced by a number in the range of 0 to 255 (the value of the bits in the binary instruction), or by a symbol that has been bound to such a number.

Subscripts on metasymbols further identify the placement of the operand in the generated binary instruction. For example, *regrs2* is a *reg* (i.e., register name) whose binary value will end up in the *rs2* field of the resulting instruction.

# SPARC 7 Instruction Set

## **Register Names**

| reg                  | A <i>reg</i> is an      | n integer u   | nit regi | ster. It can have a value of:                                                                                                                                                   |

|----------------------|-------------------------|---------------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                      | %0 t                    | through       | %31      | all integer registers                                                                                                                                                           |

|                      | %g0 t                   | through       | %g7      | global registers—same as %0 through %7                                                                                                                                          |

|                      | %o0 t                   | through       | %07      | out registers—same as %8 through %15                                                                                                                                            |

|                      | %10 1                   | through       | %17      | local registers—same as %16 through %23                                                                                                                                         |

|                      | %i0 1                   | through       | %i7      | in registers—same as %24 through %31                                                                                                                                            |

|                      | Subscripts of the follo |               | entify t | he placement of the operand in the binary instruction as one                                                                                                                    |

|                      | reg <sub>rs1</sub>      |               |          | —rs1 field                                                                                                                                                                      |

|                      | reg <sub>rs2</sub>      |               |          | —rs2 field                                                                                                                                                                      |

|                      | reg <sub>rd</sub>       |               |          | —rd field                                                                                                                                                                       |

| freg                 |                         |               |          | gister. It can have a value from %f0 through %f31. Subscripts<br>nent of the operand in the binary instruction as one of the                                                    |

|                      | freg <sub>rs1</sub>     | —rs1          | field    |                                                                                                                                                                                 |

|                      | freg <sub>rs2</sub>     | —rs2          | field    |                                                                                                                                                                                 |

|                      | freg <sub>rd</sub>      | —rd           | field    |                                                                                                                                                                                 |

| creg                 |                         | ther identif  |          | egister. It can have a value from %c0 through %c31. Sub-<br>placement of the operand in the binary instruction as one of                                                        |

|                      | creg <sub>rs1</sub>     | —rs1          | field    |                                                                                                                                                                                 |

|                      | creg <sub>rs2</sub>     | —rs2          | field    |                                                                                                                                                                                 |

|                      | creg <sub>rd</sub>      | —rd           | field    |                                                                                                                                                                                 |

| Special Symbol Names |                         |               |          |                                                                                                                                                                                 |

|                      | These app               | pear in typ   | ewrite   | eed to be written exactly as they appear in the syntax table.<br>font, and are preceded by a percent sign (%). The percent<br>ame; it must appear as part of the literal value. |

|                      | The symbol              | ol names a    | are:     |                                                                                                                                                                                 |

|                      | %psr F                  | Processor Sta | ate Regi | ster                                                                                                                                                                            |

|                      | %wim \                  | Window Inval  | lid Mask | register                                                                                                                                                                        |

%tbr Trap Base Register

|        | %у       | Y register                                                                                                                                                                                                  |

|--------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|        | %fsr     | Floating-point State Register                                                                                                                                                                               |

|        | %csr     | Coprocessor State Register                                                                                                                                                                                  |

|        | %fq      | Floating-point Queue                                                                                                                                                                                        |

|        | %cq      | Coprocessor Queue                                                                                                                                                                                           |

|        | %hi      | Unary operator that extracts high 22 bits of its operand                                                                                                                                                    |

|        | %lo      | Unary operator that extracts low 10 bits of its operand                                                                                                                                                     |

| Values |          |                                                                                                                                                                                                             |

| S      | Some ins | tructions use operands comprising values as follows:                                                                                                                                                        |

|        |          | 13—A signed immediate constant that fits in 13 bits                                                                                                                                                         |

|        |          | t22—A constant that fits in 22 bits<br>An alternate address space identifier (0 to 255)                                                                                                                     |

|        |          |                                                                                                                                                                                                             |

| Label  |          |                                                                                                                                                                                                             |

| la     | ower cas | a sequence of characters comprised of alphabetic letters (a-z, A-Z (upper and se distinct)), underscore (_), dollar sign (\$), period (.), and decimal digits (0-9), a does not begin with a decimal digit. |

| S      | Some ins | tructions offer a choice of operands. These are grouped as follows:<br>regaddr:                                                                                                                             |

|        |          | regrs1<br>regrs1 + regrs2                                                                                                                                                                                   |

|        |          | address:                                                                                                                                                                                                    |

|        |          | regrs1<br>regrs1 + regrs2<br>regrs1 + simm13<br>regrs1 - simm13<br>simm13<br>simm13 + regrs1                                                                                                                |

|        |          | reg_or_imm:                                                                                                                                                                                                 |

|        |          | regrs1<br>simm13                                                                                                                                                                                            |

### **Instruction Mnemonics**

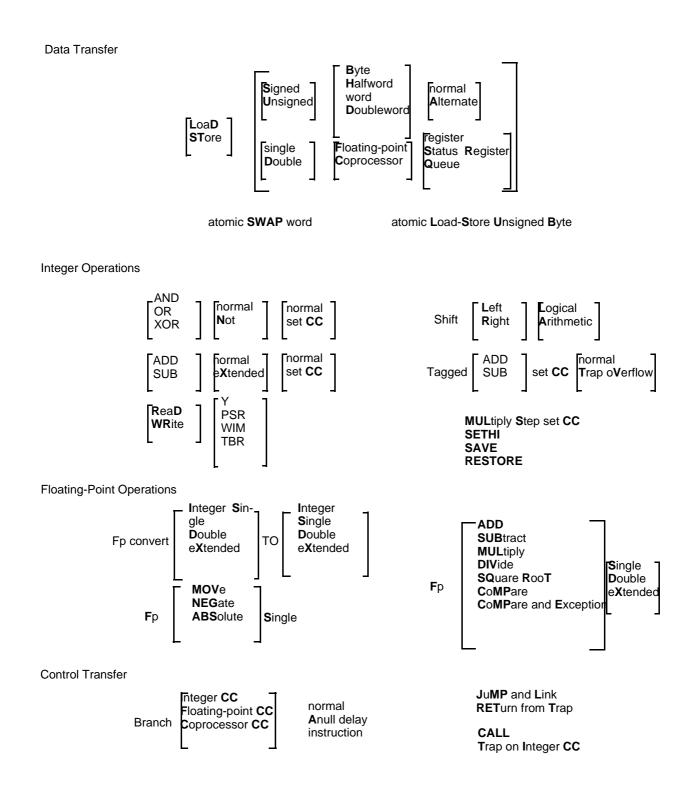

*Figure 1.* illustrates the mnemonics used to describe the SPARC instruction set. Note that some combinations possible in Figure 1. do not correspond to valid instructions (such as store signed or floating-point convert extended to extended). Refer to the instruction summary on PageBreak 7 for a list of valid SPARC instructions.

Figure 1. SPARC Instruction Mnemonic Summary

SPARC

### Definitions

This section provides a detailed definition for each ERC 32 instruction. Each definition includes: the instruction operation; suggested assembly language syntax; a description of the salient features, restrictions and trap conditions; a list of synchronous or floating-point\coprocessor traps which can occur as a consequence of executing the instruction; and the instruction format and op codes. Instructions are defined in alphabetical order with the instruction mnemonic shown in large bold type at the top of the PageBreak for easy reference. The instruction set summary that precedes the definitions, (Table 2), groups the instructions by type.

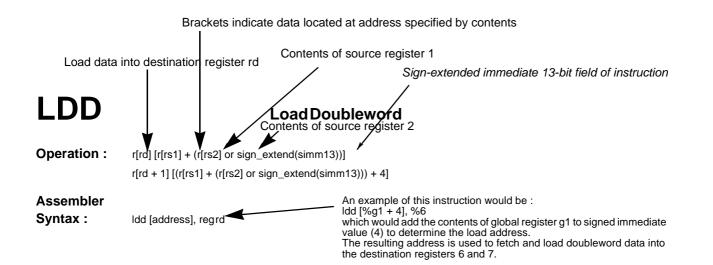

*Table 1.* identifies the abbreviations and symbols used in the instruction definitions. An example of how some of the description notations are used is given below in *Figure 2.* Register names, labels and other aspects of the syntax used in these instructions are described in the previous section.

Figure 2. Instruction Description

**Description** :The LDD instruction moves a doubleword from memory into a destination register pair, r[rd] and r[rd+1]. The effective memory address is derived by summing the contents of r[rs1] and either the....

| Symbol              | Description                                                                                                          |

|---------------------|----------------------------------------------------------------------------------------------------------------------|

| а                   | Instruction field that controls instruction annulling during control transfers                                       |

| AND, OR XOR, etc.   | AND, OR, XOR, etc operators                                                                                          |

| asr_reg             | Any implemented ASR (Ancillary State )                                                                               |

| c                   | The icc carry bit                                                                                                    |

| ссс                 | The coprocessor condition code field of the CCSR                                                                     |

| CONCAT              | Concatenate                                                                                                          |

| cond                | Instruction field that selects the condition code test for branches                                                  |

| creg                | Communication Coprocessor Register : can be %ccsr, %ccfr, %ccpr, %cccrc                                              |

| CWP                 | PSR's Current Window Pointer field                                                                                   |

| disp22              | Instruction field that contains the 22-bit sign-extended displacement for branches                                   |

| ET                  | PSR's Enable Traps bit                                                                                               |

| i                   | Instruction field that selects rs2 or sign_extend(simm13) as the second operand                                      |

| icc                 | The integer condition code field of the PSR                                                                          |

| imm22               | Instruction field that contains the 22-bit constant used by SETHI                                                    |

| n                   | The icc negative bit                                                                                                 |

| not                 | Logical complement operator                                                                                          |

| nPC                 | next Program Counter                                                                                                 |

| орс                 | Instruction field that specifies the count for Coprocessor-operate instructions                                      |

| operand2            | Either r[rs2] or sign_extend(simm13)                                                                                 |

| PC                  | Program Counter                                                                                                      |

| pS                  | PSR's previous Supervisor bit                                                                                        |

| PSR                 | Processor State Register                                                                                             |

| r[15]               | A directly addressed register (could be floating-point or coprocessor)                                               |

| rd                  | Instruction field that specifies the destination register (except for store)                                         |

| r[rd]               | Depending on context, the integer register (or its contents) specified by the instruction field, e.g. , rd, rs1, rs2 |

| r[rd]<31>           | <> are used to specify bit fields of a particular register or I/O signal                                             |

| [r[rs1] + r[rs2]]   | The contents of the address specified by r[rs1] + r[rs2]                                                             |

| rs1                 | Instruction field that specifies the source 1 register                                                               |

| rs2                 | Instruction field that specifies the source 2 register                                                               |

| S                   | PSR's Supervisor bit                                                                                                 |

| shcnt               | Instruction field that specifies the count for shift instructions                                                    |

| sign_extend(simm13) | Instruction field that contains the 13-bit, sign-extended immediate value                                            |

| Symbol              | Description                                                                                                          |

| TBR                 | Trap Base Register                                                                                                   |

| tt                  | TBR's trap type field                                                                                                |

| uf                  | Floating-point exception : underflow                                                                                 |

| V                   | The icc overflow bit                                                                                                 |

| Symbol   | Description                       |

|----------|-----------------------------------|

| WIM      | Window Invalid Mask register      |

| Y        | Y Register                        |

| Z        | The icc zero bit                  |

| -        | Subtract                          |

| х        | Multiply                          |

| /        | Divide                            |

| <        | Replaced by                       |

| 7FFFFF H | Hexadecimal number representation |

| +        | Add                               |

| Table 2. | Instruction Set Summary |

|----------|-------------------------|

|----------|-------------------------|

|                                 | Name                                                                               |                                                                                                                                 | Operation                                                                                                            |                              |

|---------------------------------|------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|------------------------------|

| r                               |                                                                                    | Land Cinerad Duty                                                                                                               | Operation                                                                                                            | Cycles                       |

|                                 | LDSB(LDSBA*)<br>LDSH(LDSHA*)<br>LDUB(LDUBA*)<br>LDUH(LDUHA*)                       | Load Signed Byte<br>Load Signed Halfword<br>Load Unsigned Byte<br>Load Unsigned Halfword                                        | (from Alternate Space)<br>(from Alternate Space)<br>(from Alternate Space)<br>(from Alternate Space)                 | 2<br>2<br>2                  |

|                                 | LD(LDA*)<br>LDD(LDDA*)                                                             | Load Word<br>Load Doubleword                                                                                                    | (from Alternate Space)<br>(from Alternate Space)                                                                     | 2<br>2<br>3                  |

| Ictions                         | LDF<br>LDDF<br>LDFSR                                                               | Load Floating Point<br>Load Double Floating Point<br>Load Floating Point StateRegister                                          |                                                                                                                      | 2<br>3<br>2                  |

| e Instru                        | LDC<br>LDDC<br>LDCSR                                                               | Load Coprocessor<br>Load Double Coprocessor<br>Load Coprocessor State Register                                                  |                                                                                                                      | 2<br>3<br>2                  |

| Load and Store Instructions     | STB(STBA*)<br>STH(STHA*)<br>ST(STA*)<br>STD(STDA*)                                 | Store Byte<br>Store Halfword<br>Store Word<br>Store Doubleword                                                                  | (into Alternate Space)<br>(into Alternate Space)<br>(into Alternate Space)<br>(into Alternate Space)                 | 3<br>3<br>3<br>4             |

| Load                            | STF<br>STDF<br>STFSR<br>STDFQ*                                                     | Store Floating Point<br>Store Double Floating Point<br>Store Floating Point State Register<br>Store Double Floating Point Queue |                                                                                                                      | 3<br>4<br>3<br>4             |

|                                 | STC<br>STDC<br>STCSR<br>STDCQ*                                                     | Store Coprocessor<br>Store Double Coprocessor<br>Store Coprocessor State Register<br>Store Double Coprocessor Queue             |                                                                                                                      | 3<br>4<br>3<br>4             |

|                                 | LDSTUB(LDSTUBA*)<br>SWAP(SWAPA*)                                                   | Atomic Load/Store Unsigned Byte<br>Swap r Register with Memory                                                                  | (in Alternate Space)<br>(in Alternate Space)                                                                         | 4                            |

|                                 | ADD(ADDcc)<br>ADDX(ADDXcc)                                                         | Add<br>Add with Carry                                                                                                           | (and modify icc)<br>(and modify icc)                                                                                 | 1<br>1                       |

| ft                              | TADDcc(TADDccTV)<br>SUB(SUBcc)<br>SUBX(SUBXcc)                                     | Tagged Add and modify icc<br>Subtract<br>Subtract with Carry                                                                    | (and Trap on overflow)<br>(and modify icc)<br>(and modify icc)                                                       | 1                            |

| al/Shi                          | TSUBcc(TSUBccTV)<br>MULScc                                                         | Tagged Subtract and modify icc<br>Multiply Step and modifyicc                                                                   | (and Trap on overflow)                                                                                               | <u> </u>                     |

| Arithmetic/Logical/Shift        | AND(ANDcc)<br>ANDN(ANDNcc)<br>OR(ORcc)<br>ORN(ORNcc)<br>XOR(XORcc)<br>XNOR(XNORcc) | And<br>And Not<br>Inclusive Or<br>Inclusive Or Not<br>Exclusive Or<br>Exclusive Nor                                             | (and modify icc)<br>(and modify icc)<br>(and modify icc)<br>(and modify icc)<br>(and modify icc)<br>(and modify icc) | 1<br>1<br>1<br>1<br>1<br>1   |

| Ar                              | SLL<br>SRL<br>SRA                                                                  | Shift Left Logical<br>Shift Right Logical<br>Shift Right Arithmetic                                                             |                                                                                                                      | 1<br>1<br>1                  |

|                                 | SETHI<br>SAVE<br>RESTORE                                                           | Set High 22 Bits of r Register<br>Save caller's window<br>Restore caller's window                                               |                                                                                                                      | 1                            |

| er                              | Bicc<br>FBicc<br>CBccc                                                             | Branch on Integer Condition Codes<br>Branch on Floating PointCondition C<br>Branch on Coprocessor Condition C                   |                                                                                                                      | 1<br>1**<br>1**<br>1**       |

| Control<br>Transfer             | CALL<br>JMPL                                                                       | Call Jump and Link                                                                                                              |                                                                                                                      | 1**<br>1**<br>2**            |

| Ύ⊢                              | RETT<br>Ticc                                                                       | Return from Trap<br>Trap on Integer Condition Codes                                                                             |                                                                                                                      | 2**<br>2**<br>1 (4 if Taken) |

| ters                            | RDY<br>RDPSR*<br>RDWIM*                                                            | Read Y Register<br>Read Processor State Register<br>Read Window Invalid Mask                                                    |                                                                                                                      | 1                            |

| Read/Write<br>Control Registers | RDTBR*<br>WRY                                                                      | Read Trap Base Register<br>Write Y Register                                                                                     |                                                                                                                      | 1<br>1<br>1                  |

| Rea                             | WRPSR*<br>WRWIM*                                                                   | Write Processor State Register<br>Write Window Invalid Mask                                                                     |                                                                                                                      | 1<br>1                       |

| ŭ                               | WRTBR*<br>UNIMP                                                                    | Write Trap Base Register<br>Unimplemented Instruction                                                                           |                                                                                                                      | 1                            |

|                                 | I IFLUSH                                                                           | I INSTRUCTION GACHE FILISO                                                                                                      |                                                                                                                      |                              |

| FP<br>Ops                       | IFLUSH<br>FPop                                                                     | Instruction Cache Flush<br>Floating Point Unit Operations                                                                       |                                                                                                                      | 1 to Launch                  |

\* privileged instruction

\*\* assuming delay slot is filled with useful instruction

| ADD                  | Add                                    |                            |                                                                                                                               |                         |  |

|----------------------|----------------------------------------|----------------------------|-------------------------------------------------------------------------------------------------------------------------------|-------------------------|--|

| Operation:           | r[rd] <del> -</del> r[rs1] +           | (r[rs2] or sign extnd(sin  | nm13))                                                                                                                        |                         |  |

| Assembler<br>Syntax: | add regrs1, reg_c                      | or_imm, regrd              |                                                                                                                               |                         |  |

| Description:         | either the content<br>extended immedia | s of r[rs2] if the instruc | of the register named in the tegister named in the tegister named in the tegister, of in the instruction if <i>i</i> equated. | or to the 13-bit, sign- |  |

| Traps:               | none                                   |                            |                                                                                                                               |                         |  |

| Format:              |                                        |                            |                                                                                                                               |                         |  |

|                      | 31 30 29 2                             | 25 24 19 18                | 14 13 12                                                                                                                      | 5 4 0                   |  |

|                      | 1 0 rd                                 | 000 000 rs1                | i=0 ignored                                                                                                                   | rs2                     |  |

|                      | 31 30 29 2                             | 5 24 19 18                 | 14 13 12                                                                                                                      | 0                       |  |

|                      | 10 rd                                  | 000 000 rs1                | i=1 si                                                                                                                        | mm13                    |  |

| ADDcc                | Add and modify icc                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |

|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Operation:           | $ r[rd] \leftarrow r[rs1] + operand2, where operand2 = (r[rs2] \text{ or sign extnd(simm13)}) $ $ n \leftarrow r[rd]<31> $ $ z \leftarrow if r[rd] = 0 \text{ then 1, else 0} $ $ v \leftarrow (r[rs1]<31> \text{ AND operand2}<31> \text{ AND not } r[rd]<31>) $ $ OR (not r[rs1]<31> \text{ AND not operand2}<31> \text{ AND } r[rd]<31>) $ $ c \leftarrow (r[rs1]<31> \text{ AND operand2}<31>) $ $ OR (not r[rd]<31> \text{ AND operand2}<31>) $ $ OR (not r[rd]<31> \text{ AND } (r[rs1]<31> \text{ OR operand2}<31>) $ |  |  |  |  |

| Assembler<br>Syntax: | addcc regrs1, reg_or_imm, regrd                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

| Description:         | ADDcc adds the contents of r[rs1] to either the contents of r[rs2] if the instruction's <i>i</i> bit equals zero, or to a 13-bit, sign-extended immediate operand if <i>i</i> equals one. The result is placed in the register specified in the <i>rd</i> field. In addition, ADDcc modifies all the integer condition codes in the manner described above.                                                                                                                                                                  |  |  |  |  |

| Traps:               | none                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |

| Format:              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

|                      | 31 30 29       25 24       19 18       14 13 12       5 4       0         1 0       rd       0 1 0 0 0 0       rs1       i=0       ignored       rs2         31 30 29       25 24       19 18       14 13 12       0                                                                                                                                                                                                                                                                                                         |  |  |  |  |

| 31 30 | 29 2 | 25 24 | 19   | 18  | 14 | 13  | 12 0   |

|-------|------|-------|------|-----|----|-----|--------|

| 1 0   | rd   | 0 1   | 0000 | rs1 |    | i=1 | simm13 |

| ADDX                 | Add with Carry                                                                                                                                                                                                                                                                                                                                                                                                     |

|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Operation:           | $r[rd] \rightarrow r[rs1] + (r[rs2] \text{ or sign extnd(simm13)}) + c$                                                                                                                                                                                                                                                                                                                                            |

| Assembler<br>Syntax: | addx regrs1, reg_or_imm, regrd                                                                                                                                                                                                                                                                                                                                                                                     |

| Description:         | ADDX adds the contents of r[rs1] to either the contents of r[rs2] if the instruction's <i>i</i> bit equals zero, or to a 13-bit, sign-extended immediate operand if <i>i</i> equals one. It then adds the PSR's carry bit ( <i>c</i> ) to that result. The final result is placed in the register specified in the <i>rd</i> field.                                                                                |

| Traps:               | none                                                                                                                                                                                                                                                                                                                                                                                                               |

| Format:              | 31       30       29       25       24       19       18       14       13       12       5       4       0         1       0       rd       0       0       1       0       rs1       i=0       ignored       rs2         31       30       29       25       24       19       18       14       13       12       0         1       0       rd       0       0       1       0       rs1       i=1       simm13 |

| ADDXcc                            | Add with Carry and modify icc                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |

|-----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Operation:                        | $ r[rd] \leftarrow r[rs1] + operand2 + c, where operand2 = (r[rs2] or sign extnd(simm13)) n \leftarrow r[rd]<31> z \leftarrow if r[rd] = 0 then 1, else 0 v \leftarrow (r[rs1]<31> AND operand2<31> AND not r[rd]<31>) OR (not r[rs1]<31> AND not operand2<31> AND r[rd]<31>) c \leftarrow (r[rs1]<31> AND operand2<31>) OR (not r[rd]<31> AND (r[rs1]<31> OR operand2<31>)) $                                                                                                                                                                                                                                                                                              |  |  |  |  |  |

| Assembler<br>Syntax:              | addxcc regrs1, reg_or_imm, regrd                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |

| Description:                      | ADDXcc adds the contents of r[rs1] to either the contents of r[rs2] if the instruction's <i>i</i> bit equals zero, or to a 13-bit, sign-extended immediate operand if <i>i</i> equals one. It then adds the PSR's carry bit ( <i>c</i> ) to that result. The final result is placed in the register specified in the <i>rd</i> field. ADDXcc also modifies all the integer condition codes in the manner described above.                                                                                                                                                                                                                                                   |  |  |  |  |  |

| Traps:                            | none                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |

| Format:                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |

|                                   | 1 0 rd 011000 rs1 i=0 ignored rs2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |

|                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |

| Syntax:<br>Description:<br>Traps: | OR (not r[rd]<31> AND (r[rs1]<31> OR operand2<31>))<br>addxcc regrs1, reg_or_imm, regrd<br>ADDXcc adds the contents of r[rs1] to either the contents of r[rs2] if the instruction's <i>i</i> bit<br>equals zero, or to a 13-bit, sign-extended immediate operand if <i>i</i> equals one. It then<br>adds the PSR's carry bit ( <i>c</i> ) to that result. The final result is placed in the register spec-<br>ified in the <i>rd</i> field. ADDXcc also modifies all the integer condition codes in the manner<br>described above.<br>none<br>$\frac{31 \ 30 \ 29 \ 25 \ 24 \ 19 \ 18 \ 14 \ 13 \ 12 \ 5 \ 4 \ 0}{1 \ 0 \ rd \ 0 \ 1 \ 10 \ 0 \ rs1 \ i=0 \ ignored \ rs2}$ |  |  |  |  |  |

| AND                  | And                                                                                                                                                                                                                                                                              |

|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Operation:           | r[rd] — r[rs1] AND (r[rs2] or sign extnd(simm13))                                                                                                                                                                                                                                |

| Assembler<br>Syntax: | and regrs1, reg_or_imm, regrd                                                                                                                                                                                                                                                    |

| Description:         | This instruction does a bitwise logical AND of the contents of register r[rs1] with either the contents of r[rs2] (if if bit field i=0) or the 13-bit, sign-extended immediate value contained in the instruction (if if bit field i=1). The result is stored in register r[rd]. |

| Traps:               | none                                                                                                                                                                                                                                                                             |

| Format:              |                                                                                                                                                                                                                                                                                  |

|                      | <u>31 30 29 25 24 19 18 14 13 12 5 4 0</u>                                                                                                                                                                                                                                       |

|                      | 1 0 rd 0 0 0 0 0 1 rs1 i=0 ignored rs2                                                                                                                                                                                                                                           |

|                      |                                                                                                                                                                                                                                                                                  |

|                      | <u>31 30 29 25 24 19 18 14 13 12 0</u>                                                                                                                                                                                                                                           |

|                      | 1         0         rd         0         0         0         1         i=1         simm13                                                                                                                                                                                        |

### And and modify icc

**Operation:** r[rd] - r[rs1] AND (r[rs2] or sign extnd(simm13)) n - r[rd]<31> z - if r[rd] =0 then 1, else 0 v 🗕 0 c → 0 Assembler andcc regrs1, reg\_or\_imm, regrd

none

This instruction does a bitwise logical AND of the contents of register r[rs1] with either the contents of r[rs2] (if if bit field i=0) or the 13-bit, sign-extended immediate value contained in the instruction (if if bit field i=1). The result is stored in register r[rd]. ANDcc also modifies all the integer condition codes in the manner described above.

#### Traps:

Syntax:

**Description:**

Format:

| 3 | 1 | 30 | 29 |    | 25 | 24    | 19  | 18 |     | 14 | 13  | 12      | 5 4    | 4   | 0 |

|---|---|----|----|----|----|-------|-----|----|-----|----|-----|---------|--------|-----|---|

|   | 1 | 0  |    | rd |    | 01000 | 1   |    | rs1 |    | i=0 | ignored |        | rs2 |   |

| 3 | 1 | 30 | 29 |    | 25 | 24    | 19  | 18 |     | 14 | 13  | 12      |        |     | 0 |

|   | 1 | 0  |    | rd |    | 01000 | ) 1 |    | rs1 |    | i=1 |         | simm13 | 3   |   |

| ANDN                 | And Not                                                                                                                                                                                                                                                                                      |

|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Operation:           | r[rd] → r[rs1] AND (r[rs2] or sign extnd(simm13))                                                                                                                                                                                                                                            |

| Assembler<br>Syntax: | andn regrs1, reg_or_imm, regrd                                                                                                                                                                                                                                                               |

| Description:         | ANDN does a bitwise logical AND of the contents of register r[rs1] with the logical com-<br>pliment (not) of either r[rs2] (if if bit field i=0) or the 13-bit, sign-extended immediate<br>value contained in the instruction (if if bit field i=1). The result is stored in register r[rd]. |

| Traps:               | none                                                                                                                                                                                                                                                                                         |

| Format:              |                                                                                                                                                                                                                                                                                              |

|                      | <u>31 30 29 25 24 19 18 14 13 12 5 4 0</u>                                                                                                                                                                                                                                                   |

|                      | 1 0 rd 0 0 0 1 0 1 rs1 i=0 ignored rs2                                                                                                                                                                                                                                                       |

|                      | 31 30 29 25 24 19 18 14 13 12 0                                                                                                                                                                                                                                                              |

|                      | $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                        |

| ANDNcc               | And Not and modify icc                                                                                                                                                                                                                                                                                                                                               |

|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Operation:           | r[rd] - r[rs1] AND (r[rs2] or sign extnd(simm13))<br>n - r[rd] < 31 ><br>z - if r[rd] = 0 then 1, else 0<br>v - 0<br>c - 0                                                                                                                                                                                                                                           |

| Assembler<br>Syntax: | andncc regrs1, reg_or_imm, regrd                                                                                                                                                                                                                                                                                                                                     |

| Description:         | ANDNcc does a bitwise logical AND of the contents of register r[rs1] with the logical compliment (not) of either r[rs2] (if bit field i=0) or the 13-bit, sign-extended immediate value contained in the instruction (if bit field i=1). The result is stored in register r[rd]. ANDNcc also modifies all the integer condition codes in the manner described above. |

| Traps:               | none                                                                                                                                                                                                                                                                                                                                                                 |

| Format:              |                                                                                                                                                                                                                                                                                                                                                                      |

|                      | <u>31 30 29 25 24 19 18 14 13 12 5 4 0</u>                                                                                                                                                                                                                                                                                                                           |

|                      | 1 0 rd 010101 rs1 i=0 ignored rs2                                                                                                                                                                                                                                                                                                                                    |

|                      | <u>31 30 29 25 24 19 18 14 13 12 0</u>                                                                                                                                                                                                                                                                                                                               |

rs1

i=1

simm13

1 0

rd

**SPARC**

| Bicc                 | Integer Conditional Branch                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Operation:           | PC $\leftarrow$ nPC<br>If condition true then nPC $\leftarrow$ PC + (sign extnd(disp22) x 4)<br>else nPC $\leftarrow$ nPC + 4                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Assembler<br>Syntax: | ba{,a} <i>label</i><br>bn{,a} <i>label</i><br>bne{,a} <i>label</i> synonym: bnz<br>be{,a} <i>label</i> synonym: bz<br>bg{,a} <i>label</i><br>ble{,a} <i>label</i><br>ble{,a} <i>label</i><br>ble{,a} <i>label</i><br>ble{,a} <i>label</i><br>ble{,a} <i>label</i><br>ble{,a} <i>label</i><br>ble{,a} <i>label</i><br>bleu{,a} <i>label</i><br>bleu{,a} <i>label</i><br>bleu{,a} <i>label</i><br>bleu{,a} <i>label</i><br>bcc{,a} <i>label</i> synonym: blu<br>bpos{,a} <i>label</i><br>bneg{,a} <i>label</i><br>bvc{,a} <i>label</i><br>bvc{,a} <i>label</i> |

|                      | Note: The instruction's annul bit field, <i>a</i> , is set by appending ",a" after the branch name. If it is not appended, the <i>a</i> field is automatically reset. ",a" is shown in braces because it is optional.                                                                                                                                                                                                                                                                                                                                        |

| Description:         | The Bicc instructions (except for BA and BN) evaluate specific integer condition code combinations (from the PSR's <i>icc</i> field) based on the branch type as specified by the value in the instruction's <i>cond</i> field. If the specified combination of condition codes evaluates as true, the branch is taken, causing a delayed, PC-relative control transfer to the address (PC + 4) + (sign extnd(disp22) x 4). If the condition codes evaluate as false, the branch is not taken.                                                               |

|                      | If the branch is not taken, the annul bit field ( <i>a</i> ) is checked. If <i>a</i> is set, the instruction immediately following the branch instruction (the delay instruction) <i>is not</i> executed (i.e., it is annulled). If the annul field is zero, the delay instruction <i>is</i> executed. If the branch is taken, the annul field is ignored, and the delay instruction is executed.                                                                                                                                                            |

|                      | Branch Never (BN) executes like a NOP, except it obeys the annul field with respect to its delay instruction.                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                      | Branch Always (BA), because it always branches regardless of the condition codes, would normally ignore the annul field. Instead, it follows the same annul field rules: if $a=1$ , the delay instruction is annulled; if $a=0$ , the delay instruction is executed.                                                                                                                                                                                                                                                                                         |

|                      | The delay instruction following a Bicc (other than BA) should not be a delayed-control-<br>transfer instruction. The results of following a Bicc with another delayed control transfer<br>instruction are implementation-dependent and therefore unpredictable.                                                                                                                                                                                                                                                                                              |

| Traps:   |       | none                                                       |                     |  |  |

|----------|-------|------------------------------------------------------------|---------------------|--|--|

| Mnemonic | Cond. | Operation                                                  | icc Test            |  |  |

| BN       | 0000  | Branch Never                                               | No test             |  |  |

| BE       | 0001  | Branch on Equal                                            | Z                   |  |  |

| BLE      | 0010  | Branch on Less or Equal                                    | z OR (n XOR v)      |  |  |

| BL       | 0011  | Branch on Less                                             | n XOR v             |  |  |

| BLEU     | 0100  | Branch on Less or Equal, Unsigned                          | c OR z              |  |  |

| BCS      | 0101  | Branch on Carry Set<br>(Less than, Unsigned)               | с                   |  |  |

| BNEG     | 0110  | Branch on Negative                                         | n                   |  |  |

| BVS      | 0111  | Branch on oVerflow Set                                     | v                   |  |  |

| ВА       | 1000  | Branch Always                                              | No test             |  |  |

| BNE      | 1001  | Branch on Not Equal                                        | not z               |  |  |

| BG       | 1010  | Branch on Greater                                          | not(z OR (n XOR v)) |  |  |

| BGE      | 1011  | Branch on Greater or Equal                                 | not(n XOR v)        |  |  |

| BGU      | 1100  | Branch on Greater, Unsigned                                | not(c OR z)         |  |  |

| BCC      | 1101  | Branch on Carry Clear<br>(Greater than or Equal, Unsigned) | not c               |  |  |

| BPOS     | 1110  | Branch on Positive                                         | not n               |  |  |

| BVC      | 1111  | Branch on oVerflow Clear                                   | not v               |  |  |

| <u>31 30 29</u> | 28 25 | 24 22 | 21 0   |

|-----------------|-------|-------|--------|

| 00 a            | cond. | 010   | disp22 |

| CALL                 | Call                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Operation:           | r[15]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Assembler<br>Syntax: | call <i>label</i>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Description:         | The CALL instruction causes a delayed, unconditional, PC-relative control transfer to the address (PC + 4) + (disp30 x 4). The CALL instruction does not have an annul bit, therefore the delay slot instruction following the CALL instruction is always executed. CALL first writes its return address (PC) into the <i>outs</i> register, r[15], and then adds 4 to the PC. The 32-bit displacement which is added to the new PC is formed by appending two low-order zeros to the 30-bit word displacement contained in the instruction. Consequently, the target address can be anywhere in the ERC 32's user or supervisor address space. |

|                      | If the instruction following a CALL uses register r[15] as a source operand, hardware interlocks add a one cycle delay.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                      | <i>Programming note:</i> a register-indirect CALL can be constructed using a JMPL instruction with <i>rd</i> set to 15.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Traps:               | none                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Format:              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                      | 31 30 29 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| <u>31 30</u> | 29     |

|--------------|--------|

| 01           | disp30 |

| СВссс                | Coprocessor Conditional Branch                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Operation:           | PC $\leftarrow$ nPC<br>If condition true then nPC $\leftarrow$ PC + (sign extnd(disp22) x 4)<br>else nPC $\leftarrow$ nPC + 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |