| AEO-004148              |                      |                          |  |

|-------------------------|----------------------|--------------------------|--|

| ARTES 4                 |                      |                          |  |

| FECHA/DATE:<br>14/01/02 | EDICIÓN/ISSUE:<br>01 | <b>PÁG./PAGE:</b> 1 / 95 |  |

| Título / Title          |  |

|-------------------------|--|

| DOCC IP DETAILED DESIGN |  |

| Redactado por / Written by     | Responsabilidad / Responsibility | Fecha / Date | Firma / Signature |

|--------------------------------|----------------------------------|--------------|-------------------|

| Pedro Rodríguez                | ASIC Design Engineer             |              |                   |

|                                |                                  |              |                   |

| Revisado por / Reviewed by     | Responsabilidad / Responsibility | Fecha / Date | Firma / Signature |

| Luis Berrojo                   | ASIC Design Manager              |              |                   |

| Aprobado por / Approved by     | Responsabilidad / Responsibility | Fecha/ Date  | Firma / Signature |

| Josep Prat                     | New Products Engineering Manager |              |                   |

| Jaime Arias                    | P.A. Manager                     |              |                   |

|                                |                                  |              |                   |

|                                |                                  |              |                   |

|                                |                                  |              |                   |

| Registrado por / Registered by | Responsabilidad / Responsibility | Fecha / Date | Firma / Signature |

| P. de Francisco                | Configuration Control manager    |              |                   |

| AEO-004148  |                |            |  |

|-------------|----------------|------------|--|

| ARTES 4     |                |            |  |

| FECHA/DATE: | EDICIÓN/ISSUE: | PÁG./PAGE: |  |

| 14/01/02    | 01             | 2 / 95     |  |

| REGISTRO DE CAMBIOS / CHANGE RECORD |                                  |                       |                     |  |  |

|-------------------------------------|----------------------------------|-----------------------|---------------------|--|--|

| EDICIÓN                             | EDICIÓN FECHA AUTOR MODIFICACIÓN |                       |                     |  |  |

| ISSUE                               | DATE                             | AUTHOR                | CHANGE              |  |  |

| Λ1                                  | 14/01/02                         | D. D. a. dark ann arr | De sum out exection |  |  |

01 14/01/02 P. Rodríguez Document creation

AEO-004148

ARTES 4

TE: EDICIÓN/ISSUE: PÁG./PAGE:

**FECHA/DATE:** 14/01/02

01

3/95

#### **CONTENTS**

| 1 | P       | PURPOSE                                                 |    |

|---|---------|---------------------------------------------------------|----|

| 2 | n       | OCUMENTS                                                |    |

| 4 |         |                                                         |    |

|   | 2.1 2.2 | APPLICABLE DOCUMENTS                                    |    |

|   | 2.2     | DEFINITIONS AND CONVENTIONS.                            |    |

| • |         | CAD TOOLS AND DESIGN DATA BASE ORGANIZATION DESCRIPTION |    |

| 3 | C       |                                                         |    |

|   | 3.1     | CAD TOOLS                                               |    |

|   | 3.2     | DESIGN DATA BASE ORGANIZATION DESCRIPTION.              | 8  |

| 4 | I       | NPUT/OUTPUT SIGNALS                                     | 1  |

|   | 4.1     | I/O FUNCTIONAL DESCRIPTION                              | 1  |

|   | 4.      | .1.1 Control Signals                                    | 1  |

|   | 4.      | .1.2 Data Bus Signals                                   |    |

|   |         | .1.3 "DHS" Physical Level SAP's Signals                 |    |

|   |         | .1.4 "OBDH" DBI Signals                                 |    |

|   |         | .1.5 IUB Signals                                        |    |

|   |         | .1.6 Test Signals                                       |    |

|   | 4.      | .1.7 I/O Summary                                        | 28 |

| 5 | F       | UNCTIONAL DESCRIPTION                                   | 29 |

| 6 | D       | DETAILED DESCRIPTION                                    | 30 |

| • |         |                                                         |    |

|   |         | BLOCK DIAGRAM                                           |    |

|   |         | .2.1 Clock and Data Recovery                            |    |

|   |         | 2.2 Watchdog and Bus Selection                          |    |

|   |         | OBDH Bus Terminal (DBI)                                 |    |

|   |         | 3.1 BAR1 Port (RIR)                                     |    |

|   |         | .3.2 BAR2 Port (RRR/CRR)                                |    |

|   | 6.      | .3.3 BAR3 Port (RBR/CBR)                                |    |

|   | 6.      | .3.4 BAT1 Port (RRT/CIT)                                | 4  |

|   |         | .3.5 BAT2 Port (RBT/CBT)                                |    |

|   |         | .3.6 IUB                                                |    |

|   |         | DHS Bus Terminal                                        |    |

|   |         | .4.1 BTS Service                                        |    |

|   |         | 4.2 ITS Service                                         |    |

|   | ٠.      | 4.3 IRS Service                                         |    |

|   |         | 4.5 RRS Service                                         |    |

|   |         | .4.6 BTTS Service                                       |    |

|   |         | 4.7 BTRS Service                                        |    |

|   |         | CLOCK DOMAINS.                                          |    |

|   | 6.6     | RESET STRATEGY AND GENERATION OF INTERNAL RESET         |    |

|   | 6.7     | METASTABILITY PROTECTION                                |    |

|   | 6.8     | GLITCH-FREE OUTPUTS DISCUSSION                          | 6′ |

| 7 | T       | TESTS                                                   | 70 |

#### AEO-004148

#### ARTES 4

**FECHA/DATE:** 14/01/02

EDICIÓN/ISSUE: 01 **PÁG./PAGE:** 4 / 95

| 7.1 FUNG | CTIONAL VALIDATION                    | 70 |

|----------|---------------------------------------|----|

| 7.1.1    | Quality of the Testbench              | 70 |

| 7.2 Logi | IC LEVEL VERIFICATION                 | 70 |

| ANNEXE A | IMPLEMENTATION EXAMPLE I: MG2RT       | 7. |

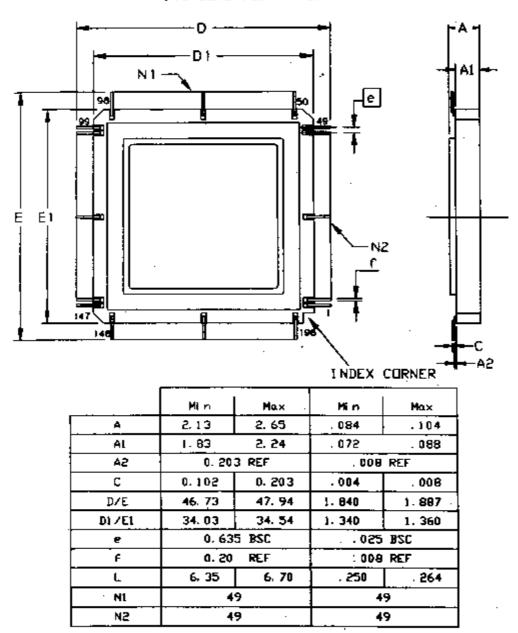

| A.1 Four | NDRY, TECHNOLOGY AND DEVICE SELECTION | 7  |

| A.2 ELEC | CTRICAL CHARACTERISTICS               |    |

| A.2.1    | Absolute Maximum Ratings              | 7. |

| A.2.2    | DC Characteristics                    | 72 |

| A.2.3    | Radiation Characteristics             |    |

| A.3 PACE | KAGING                                | 73 |

| A.4 GAT  | E COUNT AND POWER CONSUMPTION         | 74 |

| A.4.1    | Number of Gates                       | 7- |

| A.4.2    | Power Consumption                     | 74 |

| A.5 INPU | TS/OUTPUTS CHARACTERISTICS            | 70 |

| A.5.1    | I/O Timing                            | 70 |

| A.5.2    | Pinout                                |    |

| A.6 MAN  | IUFACTURING TESTS                     | 84 |

| A.6.1    | Manufacturing Test Approach           | 8  |

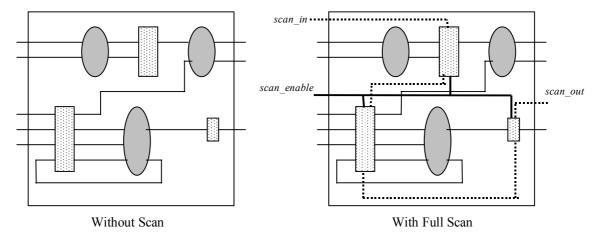

| A.6.2    | DFT                                   | 8  |

| A.6.3    | Fault Coverage                        |    |

| A.6.4    | DC Parameters Measure                 |    |

| A.6.3    | AC Parameters Measure                 | 8  |

| ANNEXE B | IMPLEMENTATION EXAMPLE II: ACTEL FPGA | 88 |

| B.1 Four | NDRY, TECHNOLOGY AND DEVICE SELECTION | 88 |

| B.2 ELEC | CTRICAL CHARACTERISTICS               | 89 |

| B.2.1    | Maximum Operating Conditions          | 8  |

| B.2.2    | Recommended Operating Conditions      | 8  |

| B.2.3    | Electrical Characteristics "DC"       | 91 |

| B.2.4    | Electrical Characteristics "AC".      | 90 |

|          | KAGING                                |    |

| B.4 GATI | E COUNT AND POWER CONSUMPTION         |    |

| B.4.1    | Gate Count.                           |    |

| B.4.2    | Power Estimation.                     | 9  |

| R 5 INPU | TS/OUTPUTS TIMING                     | 92 |

| ARTES 4  FECHA/DATE: EDICIÓN/ISSUE: PÁG./PAGE:  14/01/02 01 5 / 95 |         |                      | AEO-004148     |                          |

|--------------------------------------------------------------------|---------|----------------------|----------------|--------------------------|

| FECHA/DATE: EDICION/ISSUE: PAG./PAGE:                              | DOCC IP | ARTES 4              |                |                          |

|                                                                    |         | FECHA/DATE: 14/01/02 | EDICIÓN/ISSUE: | <b>PÁG./PAGE:</b> 5 / 95 |

#### 1 PURPOSE

This document specifies the DOCC IP including scenarios 1 and 2. It includes the following functionalities: OBDH (*On Board Data Handling Bus*) basic modem and DHS (*Data Handling System*) basic modem (for scenery 1), and RTU kernel (for scenery 2).

The resulting DOCC design can work in three different modes:

- "OBDH" compatibility mode. Just to substitute old MA28139 Plessey IC, therefore DOCC is functionally identical to Plessey OBT

- "DHS" mode. It acts as a "4-201 DHS basic modem" compliant CT or RT entity

- Cross-mode, i.e. a "DHS" mode with an IUB interface.

| DOCC IP | AEO-004148              |                      |                          |

|---------|-------------------------|----------------------|--------------------------|

|         | ARTES 4                 |                      |                          |

|         | FECHA/DATE:<br>14/01/02 | EDICIÓN/ISSUE:<br>01 | <b>PÁG./PAGE:</b> 6 / 95 |

#### 2 DOCUMENTS

#### 2.1 APPLICABLE DOCUMENTS

- 1. "MA28139 OBDH Bus Terminal", GEC Plessey, Ref: DS3592-4.5, November 1994.

- 2. "Spacecraft Data Handling Interface Standards", ESA, Ref: TTC-B-01 Issue: 1.

- 3. "OBDH DIGITAL BUS INTERFACE SPECIFICATION", ESA, Ref. THB/Apo/KZ/1386/av Issue 2

- 4. "Data Handling System Standard", ESA, Ref: PSS-04-201.

- 5. "Data Bus Specification", ESA, Ref: PSS-04-255.

- 6. "DHS Data Bus Modem Specification", ESA, Ref: PSS-04-257.

- 7. "DOCC ASIC Technical Specification", AEO-003077.

- 8. "CMOS DOCC ASIC Specification", AEO-003078.

- 9. "DOCC ASIC Test Plan", AEO-003652.

#### 2.2 REFERENCE DOCUMENTS

- 1. "VHDL Modelling Guidelines", ESA, Ref: ASIC/001 Issue 1, September 1994.

- 2. "ASIC Design and Manufacturing Requirements", WDN/PS/700, Issue 2, October 1994.

- 3. "VHDL Models for Board-level Simulation", WSM/SH/010, Issue 1, February 1996.

- 4. "PLAN DE DESARROLLO DE ASICS DIGITALES SEMICUSTOM". Ref. AEO/PD61.00-S, edición 01, 21/09/92.

- 5. "ASIC Design Manual MG2/MG2RT", Ref: TEMIC Semiconductors ATD-TS-GR-R0162, Revision 2.3. July 1997.

#### 2.3 DEFINITIONS AND CONVENTIONS

**DOCC:** DHS On Board Communication Controller.

**BAR:** Bus Adapter for Reception.

**BAT:** Bus Adapter for Transmission.

**Block Transfer Bus (BT-Bus):** An optional component bus of the 4-255 Data Bus, which carries block transmissions between terminals.

CT:Control terminal.

**DHS:** Data Handling System.

**DB:** Data Bus.

**DBI:** Digital Bus Interface.

**IP:** Intelectual Property.

**Interrogation Bus (I-Bus):** A mandatory component bus of the 4-255 Data Bus or the OBDH Bus which carries interrogation words from the BC to other bus terminals.

**Interrogation Word (Interrogation):** Is the 32 data bit sequence, which is transmitted by the BC into the I-Bus to one or more RT in each slot.

| AEO-004148              |                      |                          |  |

|-------------------------|----------------------|--------------------------|--|

|                         | ARTES 4              |                          |  |

| FECHA/DATE:<br>14/01/02 | EDICIÓN/ISSUE:<br>01 | <b>PÁG./PAGE:</b> 7 / 95 |  |

**IUB:** Internal User Bus.

**Modem Service (Service):** A capability that is provided by the modem.

**OBDH:** On Board Data Handling.

**Response Bus (R-Bus):** A mandatory component bus of the 4-255 Data Bus or the OBDH Bus, which carries response words between terminals.

**Response Word (Response):** Is the data bit sequence transmitted by a RT into the R-Bus in response to an Interrogation from the BC.

RT: Remote terminal. SAP: Service access point.

Service User (User): Entity that makes use of a service.

|         |                         | AEO-004148           |                          |

|---------|-------------------------|----------------------|--------------------------|

| DOCC IP | ARTES 4                 |                      |                          |

|         | FECHA/DATE:<br>14/01/02 | EDICIÓN/ISSUE:<br>01 | <b>PÁG./PAGE:</b> 8 / 95 |

## 3 CAD TOOLS AND DESIGN DATA BASE ORGANIZATION DESCRIPTION

#### 3.1 CAD TOOLS

The tools used in this design are:

• VHDL Simulation: LEAPFROG v. 2.7. by CADENCE

VHDL Simulation Coverage: Vnavigator by TransEDA

VHDL Synthesis: SYNOPSYS v. 2001.08.

• VERILOG Simulation: Verilog v. 2.5.12.

• ACTEL Synthesis: ACTmap VHDL synthesis R-2 1998 3.3.0.15.

• ACTEL Place & Route: DESIGNER R-2 1998 3.3.0.15.

• ACTEL Programming: ACTIVATOR 2s.

• Foundry Tools MHS\_DK, for synopsys v. 5.1, for Cadence v. 8.1

#### 3.2 DESIGN DATA BASE ORGANIZATION DESCRIPTION

A data CD contains the files related with this document and needed for manufacturing.

The different Files used in the design of the IP have been distributed in four directories as described bellow. All this information is contained in the DOCC directory.

- CODIGO: Here are included the files that contain the VHDL code. These files are separated in two directories:

- BASIC: Includes the packages of the Basic library.

- attributes.vhd standard attributes.

- std logic arith.vhd arithmetical functions.

- std logic misc.vhd includes the Xor Reduce fucntion used in the DOCC design.

- DESIGN: Includes the VHDL code of the DOCC ASIC design, and also the VHDL files for the test modules and for the test benches.

- Docc.vhd VHDL code of the DOCC ASIC design.

- CLKSelection.vhd selection of the clocks and resets depending on if the ASIC works in normal or test mode.

- BUFGS.vhd: The internal clock buffers are substituted by shortcuts in order to simulate the design, before the pads are inserted by Synopsys.

- GenBAR1.vhd test module that generates the signals for the BAR1 (in OBDH mode) or the IRS Service (in DHS mode).

- GenBAR2.vhd the same as for BAR2 or RRS Service.

- GenBAR3.vhd the same as for BAR3 or BTRS Service.

| DOCC IP | AEO-004148              |                      |                          |

|---------|-------------------------|----------------------|--------------------------|

|         | ARTES 4                 |                      |                          |

|         | FECHA/DATE:<br>14/01/02 | EDICIÓN/ISSUE:<br>01 | <b>PÁG./PAGE:</b> 9 / 95 |

- GenBAT1.vhd the same as for BAT1 or ITS/RTS Service

- GenBAT2.vhd the same as for BAT2 or BTTS Service.

- GenRTRTU.vhd test module that generates the NIDS1n, NIDS2n, RIDS1n and RIDS2n signals that codify the IUB commands to be checked in RT mode.

- GenCTRTU.vhd test module that generates the ROR signals that codify the IUB commands in CT mode.

- tb OBDHRT.vhd test bench to prove the ASIC working in OBDH and RT mode.

- tb OBDHCT.vhd test bench for the OBDH in CT mode.

- tb\_OBDHRTRTU.vhd test bench to probe the RTU Kernel in RT mode (for OBDH and DHS, changing only the configuration signal OBDHpDHSn).

- tb OBDHCTRTU.vhd test bench to test the RTU Kernel in CT mode.

- tb DHSRT.vhd test bench for the DHS in RT mode.

- tb DHSCT.vhd test bench for the DHS in CT mode.

- LEAPFROG: In this directory are the files needed to simulate the VHDL code with the tool called Leapfrog v2.7 by CADENCE.

- BASIC directory that contains the files produced in the compilation of the VHDL files included in the CODIGO/BASIC directory.

- DESIGN files generated in the compilation of the CODIGO/DESIGN files.

- sv.shm data saved of the last simulation.

- cds.lib set leapfrog libraries.

- hdl.var set leapfrog variables.

- traceOBDHRT contains the name of the signals to be traced when testing the DOCC ASIC working in OBDH and RT mode.

- traceOBDHCT likewise in OBDH and CT mode.

- traceOBRTRTU likewise when testing the RTU kernel in RT mode.

- traceOBCTRTU likewise when testing the RTU kernel in CT mode.

- traceDHSRT likewise in DHS and RT mode.

- traceDHSCT likewise in DHS and CT mode.

- VNAVIGATOR: Contains all the files generated by the tool VNavigator by TransEda. This tool is used to make an estimation of the code quality.

- SYNOPSYS: Contains the SYNOPSYS files, including database netlists (synthesis results), synthesis scripts and reports. The following files appear:

- DOCC.db: Synthesised netlist in SYNOPSYS database format for MG2RT.

- DOCCSCAN.db: Synthesised netlist, including inserted scan chains, in SYNOPSYS database format.

- DOCCATC.db: Synthesised netlist in SYNOPSYS database format for ACTEL.

- DOCC1.vdb: Test pattern file in SYNOPSYS database format. First file.

- DOCC2.vdb: Test pattern file in SYNOPSYS database format. Second file.

- DOCC3.vdb: Test pattern file in SYNOPSYS database format. Third file.

- DOCC4.vdb: Test pattern file in SYNOPSYS database format. Fourth file.

| DOCC IP | AEO-004148              |                      |                           |

|---------|-------------------------|----------------------|---------------------------|

|         | ARTES 4                 |                      |                           |

| DOCC II | FECHA/DATE:<br>14/01/02 | EDICIÓN/ISSUE:<br>01 | <b>PÁG./PAGE:</b> 10 / 95 |

There are the following subdirectories:

- BASIC: analysis result files of the BASIC library.

- DESIGN: analysis result files of the DESIGN library (Docc and clockSelection modules).

- SCR: Contains Synthesis scripts:

- Docc.scr for synthesising the design with MG2RT.

- DoccScan.scr: inserts scan chains and performs ATPG.

- DoccActel.scr: synthesis by using ACTEl as target technology.

- REPORT: contains different reports for area, timing, scan chains, and fault coverage for the synthesis with MG2RT.

- REPORTACT: contains different reports for area, timing, etc, for the synthesis with ACTEL.

## AEO-004148 ARTES 4 FECHA/DATE: EDICIÓN/ISSUE: PÁG./PAGE: 14/01/02 01 11/95

#### 4 INPUT/OUTPUT SIGNALS

#### 4.1 I/O FUNCTIONAL DESCRIPTION

#### 4.1.1 Control Signals

| Control signals |      |  |

|-----------------|------|--|

| Signal          | Type |  |

| LOSCEXTpINTn    | I    |  |

| OBDHpDHSn       | I    |  |

| CTpRTn          | I    |  |

| RESETN          | I    |  |

| SIMUL           | I    |  |

| CASCADING       | I    |  |

| LOSCINT         | I    |  |

| LOSCEXT         | I    |  |

| LOSCDIV4        | О    |  |

| TIMEOUTn        | О    |  |

Table 4.1 Control signals for both standards.

#### • LOSCEXTpINTn: Input signal.

Select between the internal ASIC's oscillator and an external clock.

If LOSCEXTpINTn = '1', the Asic's clock is proportioned externally through the input LOSCEXT.

If LOSCEXTpINTn = '0', the Asic's clock is generated by an internal oscillator.

#### • **OBDHpDHSn:** Input signal.

Select between "OBDH" standard and "DHS" standard:

If OBDHpDHSn = '1', selects OBDH standard

If OBDHpDHSn = '0', selects DHS standard

#### • **CTpRTn:** Input signal.

Select between CT mode and RT mode:

If CTpRTn = '1', the modem is in CT ("Control Terminal") mode

If CTpRTn = '0', the modem is in non controller mode (RT, "Remote Terminal")

#### • **RESETN:** Input signal (Schmidt).

Reset the device when low.

| DOCC IP | AEO-004148              |                      |                           |

|---------|-------------------------|----------------------|---------------------------|

|         | ARTES 4                 |                      |                           |

|         | FECHA/DATE:<br>14/01/02 | EDICIÓN/ISSUE:<br>01 | <b>PÁG./PAGE:</b> 12 / 95 |

#### • **SIMUL:** Input signal.

Controls simultaneous transmission through nominal and redundant response buses. This signal controls both DHS and OBDH modems and CT and RT modes.

#### • CASCADING: Input signal.

When asserted at low level, normal bus selection matrix. If asserted at high level, both buses deselected. This signal controls both DHS and OBDH modems and CT and RT modes.

#### • LOSCINT: Input signal (Schmidt).

Is included in order to add an internal RC oscillator, when the IP is implemented as ASIC. I.e. Two sources can be used for the internal net, an Input pad as well as a RC internal oscillator. A control line performs selection between the two choices. It's an 8 MHz clock signal.

#### • LOSCEXT: Input signal (Schmidt).

Local oscillator input signal. It's multiplexed with an internal RC oscillator. I.e. Two sources can be used for the internal net, an Input pad as well as a RC internal oscillator. A control line performs selection between the two choices. It's an 8 MHz clock signal.

#### • LOSCDIV4: Output signal.

This is a clock which frequency is four times less than the LOSC frequency. It can be used as master clock for the DHS mode by connecting the LOSCDIV4 pin with the MASTEROSCIN pin.

#### • TIMEOUTn: Output signal.

Low when I-Bus timeout. Indicates the period when no bus is available to transmission, due no activation. Also indicates that the bus selected has changed.

| AEO-004148              |                      |                           |  |

|-------------------------|----------------------|---------------------------|--|

| ARTES 4                 |                      |                           |  |

| FECHA/DATE:<br>14/01/02 | EDICIÓN/ISSUE:<br>01 | <b>PÁG./PAGE:</b> 13 / 95 |  |

#### 4.1.2 Data Bus Signals

| Buses signals    |   |  |  |

|------------------|---|--|--|

| (both standards) |   |  |  |

| Signal Name Type |   |  |  |

| NIDS1n           | I |  |  |

| NIDS2n           | I |  |  |

| RIDS1n           | I |  |  |

| RIDS2n           | I |  |  |

| NRDS1n           | I |  |  |

| NRDS2n           | I |  |  |

| RRDS1n           | I |  |  |

| RRDS2n           | I |  |  |

| RR1n             | О |  |  |

| RR2              | O |  |  |

| RR3n             | O |  |  |

| RR4              | О |  |  |

| NRE              | O |  |  |

| RRE              | O |  |  |

| NBDS1n           | I |  |  |

| NBDS2n           | I |  |  |

| RBDS1n           | I |  |  |

| RBDS2n           | I |  |  |

| BR1n             | О |  |  |

| BR2              | О |  |  |

| BR3n             | О |  |  |

| BR4              | О |  |  |

| NBE              | О |  |  |

| RBE              | О |  |  |

Table 4.2 Modem signals toward/from discriminators and drivers

• NIDS1n, NIDS2n: Input Signals.

Signals recovered from Nominal I-Bus in RT.

• RIDS1n, RIDS2n: Input Signals.

Signals recovered from Redundant I-Bus in RT. It could be used in CT mode for diagnostics.

• NRDS1n, NRDS2n: Input signals.

Signals recovered from Nominal R-Bus in CT. Also used in RT "Listening mode".

| DOCC IP | AEO-004148           |                      |                           |

|---------|----------------------|----------------------|---------------------------|

|         | ARTES 4              |                      |                           |

|         | FECHA/DATE: 14/01/02 | EDICIÓN/ISSUE:<br>01 | <b>PÁG./PAGE:</b> 14 / 95 |

• RRDS1n, RRDS2n: Input signals.

Signals recovered from Redundant R-Bus in CT. Also used in RT "Listening mode".

• NBDS1n, NBDS2n: Input signals.

Signals recovered from Nominal BT-Bus in CT mode. Also used in RT mode for bi-directional BTB.

• RBDS1n, RBDS2n: Input signals.

Signals recovered from Redundant BT-Bus in CT mode. Also used in RT mode for bi-directional BTB.

• RR1n, RR2, RR3n, and RR4: Output signals.

They come from the sampled data to modem and it is targeted to R-Bus (RT mode) or I-Bus (CT mode) since both modes never exist simultaneously.

• NRE, RRE: Output signals.

These signals control transmission to the R-Bus through nominal or redundant Buses.

• BR1n, BR2, BR3n, and BR4: Output signals.

They come from the sampled data fed to modem and it is targeted to BT-Bus in both RT and CT modes.

• **NBE**, **RBE**: Output signals.

These signals control transmission to the BT-Bus through nominal or redundant Buses.

| AEO-004148              |                      |                           |  |

|-------------------------|----------------------|---------------------------|--|

| ARTES 4                 |                      |                           |  |

| FECHA/DATE:<br>14/01/02 | EDICIÓN/ISSUE:<br>01 | <b>PÁG./PAGE:</b> 15 / 95 |  |

#### 4.1.3 "DHS" Physical Level SAP's Signals

| "DHS" standard |                          |      |  |

|----------------|--------------------------|------|--|

| SAP            | Signal                   | Type |  |

| BTS            | BTSCLKOUT                | О    |  |

| BTS            | BTSSYNC                  | О    |  |

| BTS            | BTSENABLE                | I    |  |

| BTS            | MASTEROSCIN              | I    |  |

| BSS            | ACTIVEN                  | О    |  |

| BSS            | ACTIVER                  | О    |  |

| BSS            | SELECTOUTN               | О    |  |

| BSS            | SELECTOUTR               | О    |  |

| BSS            | SELECTINN                | I    |  |

| BSS            | SELECTINR                | Ι    |  |

| ITS            | ITSENABLE                | I    |  |

| ITS            | ITSDATAIN                | I    |  |

| ITS            | ITSCLOCKOUT              | О    |  |

| IRS            | IRSENABLE                | I    |  |

| IRS            | IRSDATAOUT               | О    |  |

| IRS            | IRSVALIDOUT              | О    |  |

| IRS            | IRSCLOCKOUT              | О    |  |

| RTS            | RTSENABLE                | I    |  |

| RTS            | RTSDATAIN                | I    |  |

| RTS            | RTSCLOCKOUT              | О    |  |

| RRS            | RRSENABLE                | I    |  |

| RRS            | RRSDATAOUT               | О    |  |

| RRS            | RRSVALIDOUT              | О    |  |

| RRS            | RRSCLOCKOUT              | О    |  |

| BTTS           | BTTSENABLE               | I    |  |

| BTTS           | BTTSDATAIN               | Ι    |  |

| BTTS           | BTTSCLOCKOUT             | О    |  |

| BTRS           | BTRSENABLE               | I    |  |

| BTRS           | BTRSDATAOUT              | О    |  |

| BTRS           | BTRSVALIDOUT             | О    |  |

| BTRS           | BTRSCLOCKOUT             | О    |  |

| T.11. 4 3      | Modem signals in "DHC" s | 4 1  |  |

Table 4.3 Modem signals in "DHS" standard

| DOCC IP | AEO-004148              |                      |                           |

|---------|-------------------------|----------------------|---------------------------|

|         | ARTES 4                 |                      |                           |

|         | FECHA/DATE:<br>14/01/02 | EDICIÓN/ISSUE:<br>01 | <b>PÁG./PAGE:</b> 16 / 95 |

#### **4.1.3.1** BTS Service

#### • MASTEROSCIN: Input signal.

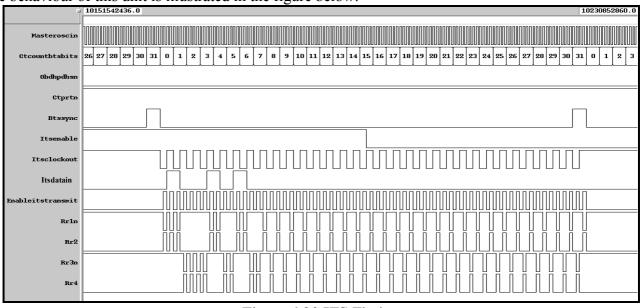

Only for CT modems. It is a train of pulses of frequency  $f_{Master\_Osc\_In}$ . It is used to provide the BTS a reference oscillator input.  $f_{Master\_Osc\_In}$  is four times BTSCLKOUT's frequency.

#### • BTSCLKOUT: Output signal.

Is a rectangular pulse train, the interval between two consecutive falling edges mark the Data Bus bit period. It has a frequency  $f_{bit}$  (=1/t<sub>C</sub>) and a mark-space ratio of MSR<sub>bit</sub>. In disabled mode it is maintained at a steady high level. It is derived internally from MASTEROSCIN.

#### • BTSSYNC: Output signal.

Each rising edge signifies that the next bit period corresponds to bit '0' of a bus slot. This signal is high during bus bit period 31. In disable mode it is maintained at steady low level.

#### • BTSENABLE (H): Input signal.

Only for CT modems. In high state the Bus Timing Service is enabled otherwise it is disabled.

#### **4.1.3.2 BSS Service**

#### • ACTIVEN (H): Output signal.

It indicates that the associated bus (nominal) is active or inactive, that is, the activity criteria is checked and signal is updated accordingly.

#### • **SELECTOUTN** (H): Output signal.

It indicates that the associated bus is currently selected.

#### • **SELECTINN (H)**: Input signal.

A request for the nominal set of buses to be used when asserted. This signal exists only on CT modems.

#### • ACTIVER (H): Output signal.

It indicates that the associated bus (redundant) is active or inactive, that is, the activity criteria is checked and signal is updated accordingly.

#### • **SELECTOUTR** (H): Output signal.

It indicates that the redundant bus is currently selected.

#### • **SELECTINR (H)**: Input signal.

A request for the redundant set of buses to be used when asserted. This signal exists only on CT modems.

| DOCC IP | AEO-004148              |                      |                           |

|---------|-------------------------|----------------------|---------------------------|

|         | ARTES 4                 |                      |                           |

|         | FECHA/DATE:<br>14/01/02 | EDICIÓN/ISSUE:<br>01 | <b>PÁG./PAGE:</b> 17 / 95 |

#### **4.1.3.3** ITS Service

#### • **ITSENABLE** (H): Input signal.

When is asserted by the user and the BTS is enabled, the ITS must operate in enabled mode. If the signal is not asserted then the ITS must operate in disabled mode.

#### • ITSDATAIN: Input signal.

Must be used by the user to provide the data. The ITS must sample it on each falling edge of the ITSCLOCKOUT.

#### • ITSCLOCKOUT: Output signal.

In enabled mode the signal shall convey a train of negative going rectangular pulses. The falling edge of each pulse is the data sampling instant for the ITSDATAIN to be modulated onto the driver signals. It must be the same as BTSCLKOUT in CT modems. In disabled mode must be maintained at a steady high level.

#### **4.1.3.4** IRS Service

#### • **IRSENABLE (H)**: Input signal.

When is asserted by the user, and the BTS is in enabled mode IRS must operate in enabled mode. When is not asserted IRS must operate in disabled mode.

#### • **IRSDATAOUT**: Output signal.

Must provide the received data to the user. In disabled mode must be maintained at steady low level.

#### • **IRSVALIDOUT (H)**: Output signal.

Must indicate the validity of the modulated symbol received in each bit. In disabled mode must be maintained at steady low level.

#### • **IRSCLOCKOUT**: Output signal.

In enabled mode must be a train of low going pulses during the receiving of data from the I-Bus. The falling of each pulse is the data sampling instant for the IRSDATAOUT and IRSVALIDOUT (H) that indicates the user that data can be read form the SAP. In disabled mode must be maintained at a steady high level.

| DOCC IP | AEO-004148              |                      |                           |

|---------|-------------------------|----------------------|---------------------------|

|         | ARTES 4                 |                      |                           |

|         | FECHA/DATE:<br>14/01/02 | EDICIÓN/ISSUE:<br>01 | <b>PÁG./PAGE:</b> 18 / 95 |

#### **4.1.3.5** RTS Service

#### • RTSENABLE (H): Input signal.

When is asserted by the user, and the BTS is in enabled mode, RTS must operate in enabled mode. When is not asserted RTS must operate in disabled mode. Changes from mode to mode (enabled, disabled) are synchronised with BTSSYNC.

#### • RTSDATAIN: Input signal.

Must be used by the user to provide data to be transmitted on the R-Bus.

#### • RTSCLOCKOUT: Output signal.

In enabled mode must be a train of low going pulses. The falling of each pulse is the data sampling instant for the RTSDATAIN to be modulated onto the driver signals. In disabled mode shall be maintained at a steady high level.

#### **4.1.3.6** RRS Service

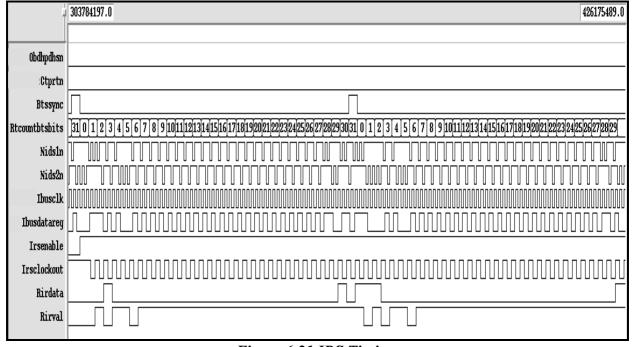

#### • **RRSENABLE** (H): Input signal.

When is asserted by the user, and the BTS is in enabled mode RRS must operate in enabled mode. When is not asserted RRS must operate in disabled mode.

#### • **RRSDATAOUT**: Output signal.

Must provide the received data to the user. In disabled mode must be maintained at a steady low level.

#### • **RRSVALIDOUT (H)**: Output signal.

Must indicate the validity of the modulated symbol received in each bit. In disabled mode must be maintained at a steady low level.

#### • **RRSCLOCKOUT**: Output signal.

In enabled mode must be a train of low going pulses during the receiving of data from the R-Bus. The falling of each pulse is the data sampling instant for the RRSDATAOUT and RRSVALIDOUT (H) that indicates the user that data can be read from the SAP. In disabled mode or during the period between response transmission burst must be maintained at steady high level.

| DOCC IP | AEO-004148              |                      |                           |

|---------|-------------------------|----------------------|---------------------------|

|         | ARTES 4                 |                      |                           |

| DOCC II | FECHA/DATE:<br>14/01/02 | EDICIÓN/ISSUE:<br>01 | <b>PÁG./PAGE:</b> 19 / 95 |

#### 4.1.3.7 BTTS Service

#### • BTTSENABLE (H): Input signal.

When is asserted by the user and the BTS is enabled, the BTTS must operate in enabled mode. If the signal is not asserted then the BTTS must operate in disabled mode.

#### • BTTSDATAIN: Input signal.

Must be used by the user to provide the data. The BTTS must sample it on each falling edge of the BTTSCLOCKOUT.

#### • BTTSCLOCKOUT: Output signal.

In enabled mode the signal must convey a train of negative going rectangular pulses. The falling edge of each pulse is the data sampling instant for the BTTSDATAIN. In disabled mode must be maintained at a steady high level.

#### 4.1.3.8 BTRS Service

#### • BTRSENABLE (H): Input signal.

When is asserted by the user, and the BTS is in enabled mode, BTRS must operate in enabled mode. When is not asserted BTRS must operate in disabled mode.

#### • BTRSDATAOUT: Output signal.

Must provide the received data to the user.

#### • BTRSVALIDOUT (H): Output signal.

Must indicate the validity of the modulated symbol received in each bit. In disabled mode must be maintained at a steady low level.

#### • BTRSCLOCKOUT: Output signal.

In enabled mode must be a train of low going pulses during the receiving of data from the block transfer bus. The falling of each pulse is the data sampling instant for the BTRSDATAOUT and BTRSVALIDOUT (H) that indicates the user than data can be read from the SAP. In disabled mode or if no data is being received must be maintained at a steady high level.

| AEO-004148              |                      |                           |  |

|-------------------------|----------------------|---------------------------|--|

| ARTES 4                 |                      |                           |  |

| FECHA/DATE:<br>14/01/02 | EDICIÓN/ISSUE:<br>01 | <b>PÁG./PAGE:</b> 20 / 95 |  |

#### 4.1.4 "OBDH" DBI Signals

| "OBDH" standard |             |      |  |

|-----------------|-------------|------|--|

| Port            | Signal      | Type |  |

| CIT             | CITMOD      | I    |  |

| CIT             | CITSEL      | I    |  |

| CIT             | CITDATA     | I    |  |

| CIT             | CITCLK      | I    |  |

| CIT             | CITSYNC     | I    |  |

| RRR/CRR         | RRR/CRRINIT | I    |  |

| RRR/CRR         | RRR/CRRDATA | О    |  |

| RRR/CRR         | RRR/CRRVAL  | О    |  |

| RRR/CRR         | RRR/CRRCLK  | О    |  |

| RBR/CBR         | RBR/CBRINIT | I    |  |

| RBR/CBR         | RBR/CBRDATA | О    |  |

| RBR/CBR         | RBR/CBRVAL  | О    |  |

| RBR/CBR         | RBR/CBRCLK  | О    |  |

| RIR             | CTRIRSYNC   | I    |  |

| RIR             | CTRIRDATA   | I    |  |

| RIR             | CTRIRVAL    | I    |  |

| RIR             | CTRIRCLK    | I    |  |

| RIR             | RIRSYNC     | О    |  |

| RIR             | RIRDATA     | О    |  |

| RIR             | RIRVAL      | О    |  |

| RIR             | RIRCLK      | О    |  |

| RRT             | RRTDATA     | I    |  |

| RRT             | RRTEN       | I    |  |

| RBT/CBT         | RBT/CBTEN   | I    |  |

| RBT/CBT         | RBT/CBTDATA | I    |  |

Table 4.4 Modem signals in "OBDH" standard.

#### 4.1.4.1 RIR Output Signals

These signals are active when the RTU Kernel is coupled to the basic modem. It occurs when it operates in RT mode.

#### • **RIRCLK:** Output signal.

It's a train of pulses of frequency equal to data rate (524488 Hz). One data bit period is equal to one RIRCLK period; first half period low, second half high. It is recovered from I-Bus.

# AEO-004148 ARTES 4 FECHA/DATE: EDICIÓN/ISSUE: PÁG./PAGE: 14/01/02 01 21/95

#### • **RIRSYNC:** Output signal.

It's a pulse of a one bit period duration, at bit 2 of the frame.

#### • **RIRDATA:** Output signal.

NRZ data received from I-Bus at the falling edge of RIRCLK. Each bit is contained in one data bit period.

#### • **RIRVAL:** Output signal.

Asserted at the falling edge of RIRSYNC, de-asserted at the RIRCLK falling edge of an invalid RIRDATA bit sampling.

#### 4.1.4.2 RIR Input Signals

These signals become active when the RTU Kernel is isolated to the basic modem. It occurs when the basic modem operates in CT mode.

#### • **CTRIRCLK:** Input signal.

It's a train of pulses of frequency equal to data rate (524488 Hz). One data bit period is equal to one CTRIRCLK period; first half period low, second half high. It is generated outside the design.

#### • **CTRIRSYNC:** Input signal.

It's a pulse of a one bit period duration, at bit 2 of the frame.

#### • **CTRIRDATA:** Input signal.

NRZ data received from I-Bus at the falling edge of CTRIRCLK. Each bit is contained in one data bit period.

#### • **CTRIRVAL:** Input signal.

Asserted at the falling edge of CTRIRSYNC, de-asserted at the CTRIRCLK falling edge of an invalid CTRIRDATA bit sampling.

#### 4.1.4.3 RRR/CRR Signals

#### • **CRR/RRRCLK:** Output signal.

A train of pulses of frequency equal to data rate (524488 Hz) One data bit period is equal to one CRR/RRRCLK period; First half period low, second half high. It is recovered from R-Bus, so when no signal is detected at the R-Bus CRR/RRRCLK is at low state.

#### • **CRR/RRRDATA:** Output signal.

NRZ data recovered from the R-Bus at the falling edge of CRR/RRRCLK. Each bit is contained in one data bit period.

| DOCC IP |                         | AEO-004148           |                    |

|---------|-------------------------|----------------------|--------------------|

|         | ARTES 4                 |                      |                    |

|         | FECHA/DATE:<br>14/01/02 | EDICIÓN/ISSUE:<br>01 | PÁG./PAGE: 22 / 95 |

#### • **CRR/RRRINIT:** Input signal.

A pulse of one bit period during bit '1'. At the CRR/RRRINIT rising edge the CRR/RRRCLK and CRR/RRRDATA signals are set to low level and CRR/RRRVAL signal is asserted.

#### • CRR/RRRVAL: Output signal.

Asserted at the rising edge of CRR/RRRINIT, de-asserted at the CRR/RRRCLK falling edge of a invalid CRR/RRRDATA bit sampling.

#### 4.1.4.4 RBR/CBR Signals

#### • **CBRCLK:** Output signal.

It's a train of pulses of frequency equal to data rate (524488 Hz). One data bit period is equal to one CBRCLK period; first half period low, second half high. It is recovered from BT-Bus, so when no signal is detected at the BT-Bus CBRCLK is at low state.

#### • **CBRDATA:** Output signal.

NRZ data recovered from the BT-Bus at the falling edge of CBRCLK. Each bit is contained in one data bit period.

#### • **CBRINIT:** Input signal.

A pulse of one bit period at bit '1'. At the CBRINIT rising edge the CBRCLK and CBRDATA signals are set to low level and CBRVAL is asserted.

#### • **CBRVAL:** Output signal.

Asserted at the rising edge of CBRINIT, de-asserted at the CBRCLK falling edge of an invalid CBRDATA bit sampling.

#### 4.1.4.5 CIT Signals

#### • **CITMOD:** Input signal.

A train of pulses of frequency equal to double of data rate. One data bit period is equal to two CITMOD periods; First half period low, second half period high, each edge marks the limits of pulses for the bus driver signals (RR1n, RR2...).

#### • **CITCLK:** Input signal.

A train of pulses of frequency equal to data rate. One data bit period is equal to one CITCLK period; first half period low, second half high.

#### • **CITDATA:** Input signal.

NRZ data at a rate equal to CITCLK bps from the user. Each data is contained in one bit period (time between consecutive CITCLK falling edges) and is sampled in each CITCLK rising edge to be modulated onto I-Bus.

| DOCC IP | AEO-004148              |                      |                           |

|---------|-------------------------|----------------------|---------------------------|

|         | ARTES 4                 |                      |                           |

|         | FECHA/DATE:<br>14/01/02 | EDICIÓN/ISSUE:<br>01 | <b>PÁG./PAGE:</b> 23 / 95 |

#### • **CITSYNC:** Input signal.

Is a pulse of one bit period duration at bit '0'. Marks the start of an interrogation.

#### • **CITSEL:** Input signal.

Assert or de-assert with the falling edge of CITCLK. When is de-asserted (low level), it selects the Nominal Bus. When it is asserted (high level), selects the Redundant Bus.

#### 4.1.4.6 RRT/CRT Signals

#### • **RRTEN:** Input signal.

Asserted at the falling edge of the RIRSYNC, de-asserted at the RIRCLK falling edge that indicates the end of the last data bit of the transmitted respond word (bit 12 or 20). Enabled response transmission.

#### • **RRTDATA:** Input signal.

NRZ data at a rate equal to RIRCLK BPS from the user. It begins with the rising edge of the RRTEN. Each data is contained in one bit period (time between consecutive RIRCLK falling edges) and is sampled in each RIRCLK rising edge to be modulated onto R-Bus.

#### 4.1.4.7 RBT/CBT Signals

#### • **RBTEN:** Input signal.

Asserted at a RIRSYNC falling edge, de-asserted at the RIRCLK falling edge that indicates the end of the last data bit of the transmitted transfer block data.

#### • **RBTDATA:** Input signal.

NRZ data at a rate equal to RIRCLK bps. It begins with the rising edge of the RBTEN. Each data is contained in one bit period (i.e. time between consecutive RIRCLK falling edges) and is sampled in each RIRCLK rising edge.

|         |             | AEO-004148     |            |

|---------|-------------|----------------|------------|

| DOCC IP | ARTES 4     |                |            |

|         | FECHA/DATE: | EDICIÓN/ISSUE: | PÁG./PAGE: |

|         | 14/01/02    | 01             | 24 / 95    |

#### 4.1.5 IUB Signals

| Signal            | Type        | Description                                              |  |

|-------------------|-------------|----------------------------------------------------------|--|

|                   | IUB SECTION |                                                          |  |

| IRCLK             | O           | Interrogation rate clock                                 |  |

| CTCLK             | О           | Continuous clock                                         |  |

| TRCLK             | Ο           | Transfer clock                                           |  |

| MLDATA            | O           | Memory load data to user                                 |  |

| MLADD(0:4)        | O           | Memory load address MSB:LSB (Interrogation bit 10:14)    |  |

| <b>CHADD(0:7)</b> | O           | Channel address 0:7 (Interrogation bit 23:30)            |  |

| MOSC              | O           | Mode short command (Interrogation mode bits 19/22 = '1') |  |

| MOLC              | O           | Switch closure ON/OFF command                            |  |

| MOHL              | Ο           | High power ON/OFF command                                |  |

| MOBT              | Ο           | Mode block Transfer                                      |  |

| MODBL             | Ο           | Digital bi-level data acquisition                        |  |

| MODS16            | Ο           | 16 bit serial digital data acquisition                   |  |

| MODS8             | Ο           | 8 bit serial digital data acquisition                    |  |

| MOANS             | О           | Single ended analogue data acquisition                   |  |

| MOAND             | Ο           | Double ended analogue data acquisition                   |  |

| PC                | Ο           | Power on to analogue to digital converter                |  |

| ANCLK             | Ο           | ADC shift clock                                          |  |

| SOC               | O           | Start of conversion                                      |  |

| SH                | Ο           | Sample/Hold                                              |  |

| DIGIN             | I           | Digital serial data input                                |  |

| ANSIN             | I           | Analogue serial data input                               |  |

| BCP(1:4)          | Ο           | Broadcast pulse (1:4)                                    |  |

| BCPVAL            | Ο           | Broadcast pulse valid                                    |  |

| DATARRT           | Ο           | Data to RRT when used as RTU kernel                      |  |

| ENRRT             | Ο           | Enable RRT when used as RTU kernel                       |  |

| TA(0:5)           | I           | Terminal address bit (0:5)                               |  |

| EXTFMT            | I           | Extended format Enable                                   |  |

| EXTMLA1           | I           | Extended Memory Load Address 1 Enable                    |  |

| EXTMLA2           | I           | Extended Memory Load Address 2 Enable                    |  |

| OOINH             | I           | ON/OFF Inhibit of MOLC commands                          |  |

| TAV               | I           | Terminal available (take low to disable IUB interface)   |  |

Table 4.5 IUB signals.

## AEO-004148 ARTES 4 FECHA/DATE: EDICIÓN/ISSUE: PÁG./PAGE: 14/01/02 01 25 / 95

• IRCLK: Output signal.

Interrogation rate clock.

• CTCLK: Output signal. Continuous clock ½ RIRCLK.

• TRCLK: Output signal.

Transfer clock.

• MLDATA: Output signal.

Memory load data to user.

• MLADD(0:4): Output signal.

Memory load address MSB: LSB (Interrogation bit 10:14).

• **CHADD(0:7):** Output signal.

Channel address 0:7 (Interrogation bit 23:30).

• **MOSC:** Output signal.

Mode short command (Interrogation mode bits 19/22 = '1').

• MOLC: Output signal.

Switch closure ON/OFF command.

• **MOHL:** Output signal.

High power ON/OFF command.

• **MOBT:** Output signal.

Mode block Transfer.

• **MODBL:** Output signal.

Digital bi-level data acquisition.

• MODS16: Output signal.

16 bit serial digital data acquisition.

• MODS8: Output signal.

8 bit serial digital data acquisition.

• **MOANS:** Output signal.

Single ended analogue data acquisition.

| ARTES 4                            | DOCC IP | AEO-004148 |  |                    |  |

|------------------------------------|---------|------------|--|--------------------|--|

|                                    |         | ARTES 4    |  |                    |  |

| FECHA/DATE: EDICIÓN/ISSUE: PAG./PA |         |            |  | PÁG./PAGE: 26 / 95 |  |

• **MOAND:** Output signal.

Double ended analogue data acquisition.

• **PC:** Output signal.

Power on to analogue to digital converter.

• **ANCLK:** Output signal.

ADC shift clock.

• **SOC:** Output signal.

Start of conversion control for external ADC.

• SH: Output signal.

Sample/Hold control for external ADC.

• **DIGIN:** Input signal.

Digital serial data input.

• **ANSIN:** Input signal.

Analogue serial data input.

• **BCP(1:4)**: Output signal.

Broadcast pulse (1:4).

• BCPVAL: Output signal.

Broadcast pulse valid.

• **DATARRT:** Output signal.

Data to RRT when used as RTU kernel.

• **ENRRT:** Output signal.

Enable RRT when used as RTU kernel.

• **TA(0:5)**: Input signal.

Terminal address bit (0:5).

• **EXTFMT:** Input signal.

Extended format Enable.

• **EXTMLA1:** Input signal.

Extended Memory Load Address 1 Enable.

| DOCC IP | AEO-004148  |                |            |

|---------|-------------|----------------|------------|

|         | ARTES 4     |                |            |

|         | FECHA/DATE: | EDICIÓN/ISSUE: | PÁG./PAGE: |

|         | 14/01/02    | 01             | 27 / 95    |

• **EXTMLA2:** Input signal.

Extended Memory Load Address 2 Enable.

• **OOINH:** Input signal.

ON/OFF Inhibit of MOLC commands.

• TAV: Input signal.

Terminal available (take low to disable IUB interface).

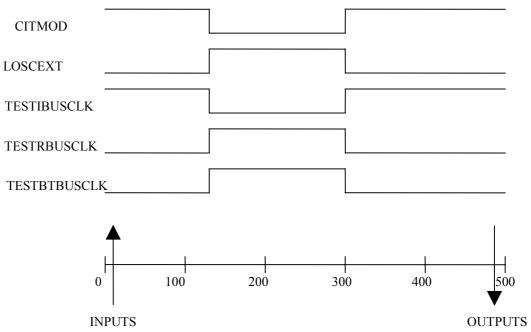

#### 4.1.6 Test Signals

| <b>Test Signals</b> |      |  |  |

|---------------------|------|--|--|

| Signal              | Type |  |  |

| TESTMODE            | I    |  |  |

| TESTIBUSCLK         | I    |  |  |

| TESTRBUSCLK         | I    |  |  |

| TESTBTBUSCLK        | I    |  |  |

Table 4.6 Test Signals.

• **TESTMODE:** Input signal.

Selects between test or normal mode of function.

If TESTMODE = '1', the Asic works in test mode.

If TESTMODE = '0', the Asic works in normal mode.

• **TESTIBUSCLK:** Input signal.

Trough this pin an IbusClk equivalent signal is inyected, when the Asic runs in test mode.

• TESTRBUSCLK: Input signal.

Trough this pin a RbusClk equivalent signal is inyected, when the Asic runs in test mode.

• TESTBTBUSCLK: Input signal.

Trough this pin a BTbusClk equivalent signal is invected, when the Asic runs in test mode.

# AEO-004148 ARTES 4 FECHA/DATE: EDICIÓN/ISSUE: PÁG./PAGE: 14/01/02 01 28 / 95

#### **4.1.7 I/O Summary**

| MODULE    | Inputs | Outputs | Total |

|-----------|--------|---------|-------|

| Control   | 8      | 2       | 10    |

| DataBuses | 12     | 12      | 24    |

| DHS       | 13     | 18      | 31    |

| OBDH      | 15     | 10      | 25    |

| IUB       | 13     | 37      | 50    |

| Test      | 4      |         | 4     |

| Total     | 65     | 79      | 144   |

Table 4.7 I/O sumary.

Since the ASIC can not be OBDH and DHS at the same time and it will not work in CT and RT mode, many of this inputs and outputs never are going to have stimuli at the same moment. So the design has been made sharing ports between some of those inputs or outputs, which have a similar functionality in different modes. In the following table are shown the signals that will be connected to the same pin.

| Inputs and outputs connected with the same pin |

|------------------------------------------------|

| RIRDATA = IRSDATAOUT                           |

| RIRVAL = IRSVALIDOUT                           |

| CRRINIT = RRSENABLE                            |

| CRRCLK = RRSCLOCKOUT                           |

| CRRDATA = RRSDATAOUT                           |

| CRRVAL = RRSVALIDOUT                           |

| CBRINIT = BTRSENABLE                           |

| CBRCLK = BTRSCLOCKOUT                          |

| CBRDATA = BTRSDATAOUT                          |

| CBRVAL = BTRSVALIDOUT                          |

| CITMOD = MASTEROSCIN                           |

| CITDATA = RRTDATA = ITSDATAIN = RTSDATAIN      |

| CITSEL = SELECTINN                             |

| RRTEN = ITSENABLE = RTSENABLE                  |

| ITSCLOCKOUT = RTSCLOCKOUT                      |

| RBTDATA = BTTSDATAIN                           |

| RBTEN = BTTSENABLE                             |

|                                                |

Table 4.8 Inputs and Outputs connected with the same pin.

Taking into account the last consideration, the final number of I/O in this design is:

**Total I/O Number = 144 - 20 = 124**

| DOCC IP | AEO-004148              |                      |                           |

|---------|-------------------------|----------------------|---------------------------|

|         | ARTES 4                 |                      |                           |

|         | FECHA/DATE:<br>14/01/02 | EDICIÓN/ISSUE:<br>01 | <b>PÁG./PAGE:</b> 29 / 95 |

#### 5 FUNCTIONAL DESCRIPTION

The DOCC IP implementation described in this document follows the functionality described in documents [AD\_1] for the OBDH bus, [AD\_7] for the DHS bus, and [AD\_1] for the RTU module. It also follows the technical specification described in [AD\_7]. The following differences are going to be implemented in the DOCC IP against the functionality implemented by Plessey:

- 1.- The Watchdog and Bus selection module follows the [AD\_7] DHS bus implementation. This is in order to standardise the bus selection in a common functionality for both buses.

- 2.- RIR signals are divided in input signals and output signals, while they are bi-directional signals in the MA28139 ASIC. In that way some technological problems are avoided.

- 3.- VAL signals timing is delayed ¼ bit. Thus, waveforms on pages 7 and 8 in AD\_1 changes slightly. This is applicable to RIRVAL, CRRVAL, and CBRVAL signals on ports BAR 1, 2, and 3. The reason for this change is to perform a synchronous design that otherwise will be impossible. The signals RIRSYNC, RRE, NRE, RBE and NBE are also delayed ¼ bit due the same reason (pages 5,6,7 in AD\_1).

- 4.- The signal CITINV has been eliminated.

- 5.- SHORTRESP and its function have not been implemented.

- 6.- There is a new signal, CASCADING, that is used to deselect all the buses. It works for OBDH and DHS and in CT and RT modes.

- 7.- For OBDH the inverted sync pattern LOLOLOHOHOHO is also valid, as for DHS.

- 8.- All the references to the Bus Monitor have been avoided in this document. The reason is that in terms of VHDL code, RT and BM are the same design. So the RT mode refers to both types of equipment. The pin RTpBMn is not necessary.

| AEO-004148              |                      |                           |

|-------------------------|----------------------|---------------------------|

| ARTES 4                 |                      |                           |

| FECHA/DATE:<br>14/01/02 | EDICIÓN/ISSUE:<br>01 | <b>PÁG./PAGE:</b> 30 / 95 |

#### 6 DETAILED DESCRIPTION

#### 6.1 BLOCK DIAGRAM

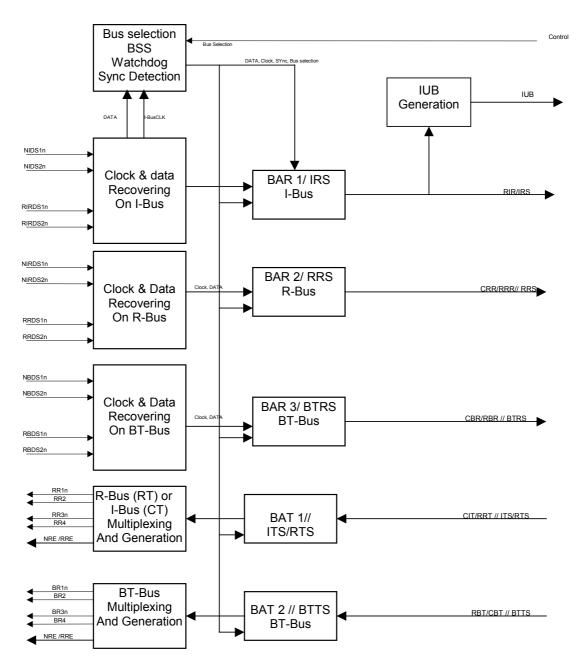

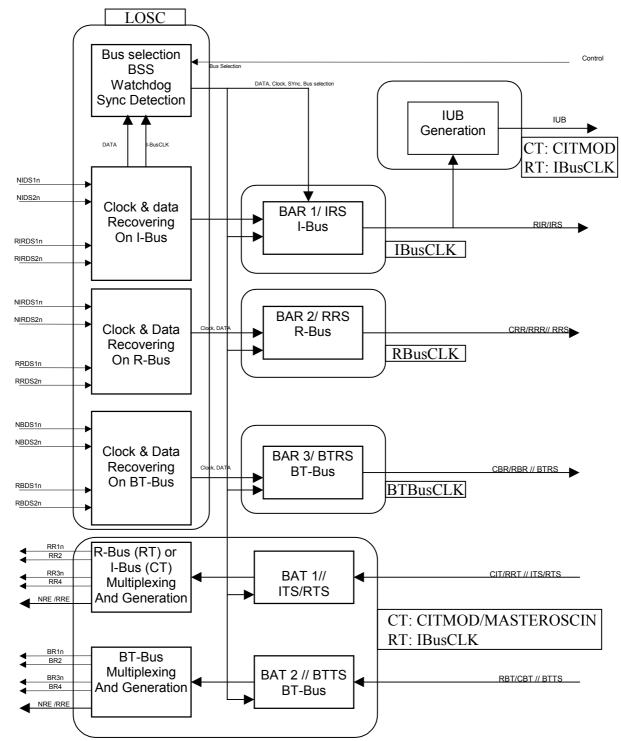

Figure 6.1 DOCC Block Diagram.

| DOCC IP | AEO-004148  |                |            |

|---------|-------------|----------------|------------|

|         | ARTES 4     |                |            |

|         | FECHA/DATE: | EDICIÓN/ISSUE: | PÁG./PAGE: |

|         | 14/01/02    | 01             | 31 / 95    |

#### **6.2 INTERFACE WITH THE I-BUS**

#### **6.2.1** Clock and Data Recovery

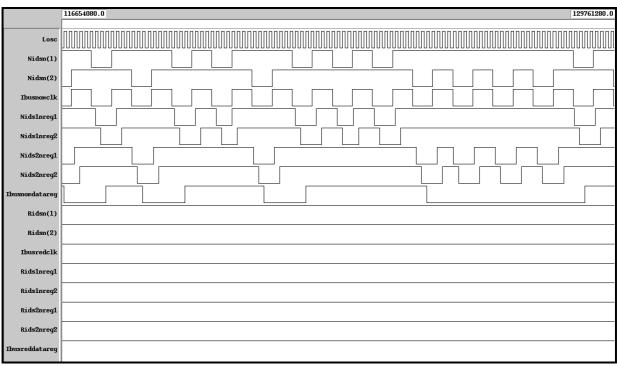

CLOCK Signals

LOSC

Input Signals

- NIDS1n

- NIDS2n

- RIDS1n

- RIDS2n

Output Signals

- IBusNomCLK

- IBusRedCLK

- IBusNomDataReg

- IbusRedDataReg

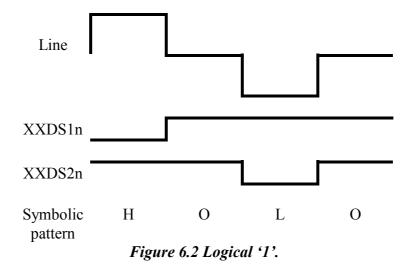

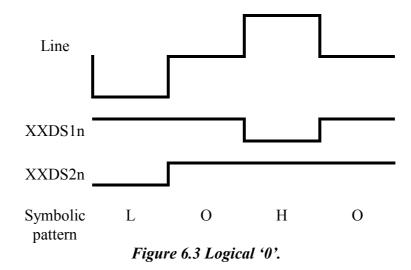

The digital data coming from CT or RT have to be modulated before be placed in the physical wires of the bus. Also the data flowing trough the data bus to the terminals have to be demodulated into digital signals to be understand by the design. The data and clock arrive to the DOCC design from the I-bus modulated using a Litton code. There are two input signals (NIDS1n and NIDS2n) for the nominal bus, and two for the redundant (RIDS1n and RIDS2n). In Litton modulation a unique scheme is assigned to logical '0' and '1'. A modulation clock with a frequency four times of the data clock has to be used, since four changes in Litton signal happen in each bit time. Litton Patterns have three possible voltage values: 'H' positive voltage, 'L' negative voltage or 'O' zero.

In the following graphics a '1'nd a '0' transmission are illustrated:

| DOCC IP | AEO-004148  |                |            |

|---------|-------------|----------------|------------|

|         | ARTES 4     |                |            |

|         | FECHA/DATE: | EDICIÓN/ISSUE: | PÁG./PAGE: |

|         | 14/01/02    | 01             | 32 / 95    |

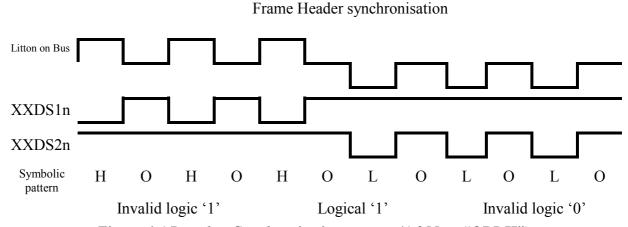

Also a synchronisation pattern is send at the beginning of every slot transmission. It includes an invalid '1' and '0' codification that make easy the synchronisation header recognition and appears in the following figure:

Figure 6.4 Data bus Synchronisation pattern (4-255 or "OBDH").

It must be noted that for the OBDH and DHS modems two possible synchronisation patterns are considered: the previous one and LOLOLOHOHOHO.

This unit performs the following tasks:

- Detects Low logic levels in the nominal and redundant input signals.

- Extracts the recovered clock from the nominal and redundant buses.

| DOCC IP | AEO-004148  |                |            |

|---------|-------------|----------------|------------|

|         | ARTES 4     |                |            |

|         | FECHA/DATE: | EDICIÓN/ISSUE: | PÁG./PAGE: |

|         | 14/01/02    | 01             | 33 / 95    |

This unit performs a first demodulation of the incoming signals as a series of '0's and '1's. It must be pointed out that whenever NIDS1n or RIDS1n is '0', it considers there is a '1' in the corresponding bus, and if NIDS2n or RIDS2n is '0', it considers there is a '0'. Both buses are sampled by using the LOSC input signal as a clock. It must be an 8 MHz signal in order to obtain a correct decoding. It must be noted that the four signals are captured two times in order to avoid metastability. This series of data will be further decoded in order to obtain the synchronisation sequence and the valid or invalid '0's and '1's transmitted through the bus.

The nominal and redundant clocks are generated by simply performing the logical and of the NIDS1n and NIDS2n signals for the nominal clock, and the RIDS1n and RIDS2n signals for the redundant clock. The behaviour of this unit is illustrated in the figure below.

Figure 6.5 Clock and Data recovering on the I-bus.

# AEO-004148 ARTES 4 FECHA/DATE: EDICIÓN/ISSUE: PÁG./PAGE: 14/01/02 01 34/95

#### 6.2.2 Watchdog and Bus Selection

#### CLOCK Signals

• LOSC

#### Input Signals

- OBDHpDHSn

- CASCADING

- SIMUL

- CITSEL

- CTpRTn

- SELECTINN

- SELECTINR

- IBusNomCLK

- IBusRedCLK

- IBusNomDataReg

- IbusRedDataReg

#### Output Signals

- DetectINomSync

- DetectIRedSync

- IBusNomSync

- IBusRedSync

- INomActive

- IRedActive ACTIVEN

- ACTIVER

- ACTIVER

- SelNomIBusSELECTOUTN

- SELECTOUTR

- TIMEOUTn

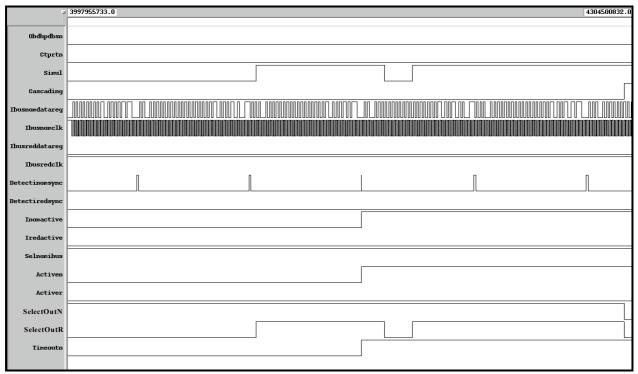

#### This unit performs the following tasks:

- Decodes the raw data bits coming from the Clock and Data recovering unit as series of bits synchronous with the Recovered clocks.

- Detects Synchronisation patterns.

- Activates the INomActive or IRedActive signals by detecting three consecutive sync patterns.

- Deactivates the INomActive and IRedActive signals by loosing three consecutive sync patterns. (Watchdog function).

- Generates the ACTIVEN and ACTIVER BSS output signals.

| DOCC IP | AEO-004148  |                |            |

|---------|-------------|----------------|------------|

|         | ARTES 4     |                |            |

|         | FECHA/DATE: | EDICIÓN/ISSUE: | PÁG./PAGE: |

|         | 14/01/02    | 01             | 35 / 95    |

- Activates the Selection flag SelNomIBus (SelNomIBus = '1', nominal set of buses selected; SelNomIBus = '0', redundant buses selected) according to the value of the INomActive and IRedActive signals in RT mode or of the Selection inputs in CT mode (see also SIMUL and CASCADING discussion below).

- Generates the SELECTOUTN and SELECTOUTR BSS output signals.

- Activates the TIMEOUTn signal when transition occurs in bus selection.

This unit is composed of two submodules that perform some of the previous tasks for the nominal and redundant buses. Bellow appears the description of one of the submodules. The other has the same behaviour but applied to the redundant bus.

The IBusNomCLK nominal I-bus incoming clock signal is doubly registered in this unit in order to avoid metastability. After that, rising edges on this signal are checked. When detected, the series of incoming data bits IbusNomDataReg are stored in a shift register (6 bits in depth), called IbusNomSync. This shift register is checked in order to detect synchronisation patterns. When detected, a pulse is generated in the DetectINomSync signal. It must be noted that for OBDH and DHS the "111000" and "000111" patterns are valid. When three consecutive sync patterns are detected with the correct separation (64 IBusNomCLK clock pulses), the INomActive flag is activated. A watchdog counter is reset every time a Sync pattern is detected. Otherwise, the INomActive signal is deactivated.

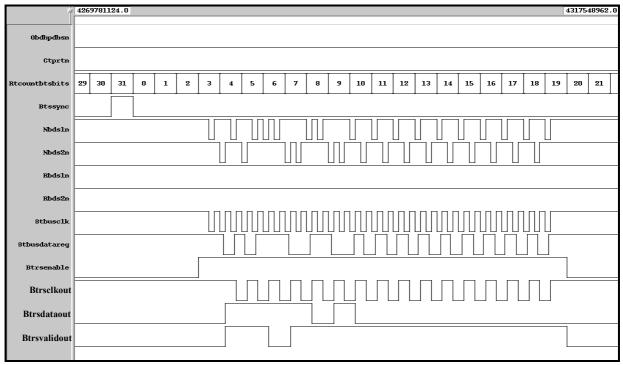

Bus Activity detection and Bus selection behaviour is shown in the following figure.

Figure 6.6 Bus activation and selection.

## AEO-004148 ARTES 4 FECHA/DATE: EDICIÓN/ISSUE: PÁG./PAGE: 14/01/02 01 36/95

The selection of the buses depends on the function mode (OBDH or DHS and CT or RT), on the activity detected and also on the inputs CITSEL, SELECTINN, SELECTINR, CASCADING and SIMUL. In the following tables can be seen how the selection is made:

| <b>CASCADING Signal</b> | Bus selection status    |  |

|-------------------------|-------------------------|--|

| L                       | Normal selection matrix |  |

| Н                       | Both buses deselected   |  |

Table 6.1 Bus selection in CASCADING configuration.

If CASCADING is not asserted the bus selection is performed by taken into account the SIMUL input in the following way:

| SIMUL Signal | Bus selection status    |  |

|--------------|-------------------------|--|

| L            | Normal selection matrix |  |

| Н            | Both buses selected     |  |

Table 6.2 Bus selection according to SIMUL.

If CASCADING and SIMUL are not asserted bus selection is performed as shown in tables 6.3, 6.4 and 6.5.

When basic modem operates in RT mode, selection of the buses is performed according to the next table:

| Nominal Bus | Redundant Bus | Selected Bus |

|-------------|---------------|--------------|

| Inactive    | Inactive      | N-Bus        |

| Active      | Inactive      | N-Bus        |

| Inactive    | Active        | R-Bus        |

| Active      | Active        | N-Bus        |

Table 6.3 Selection matrix in RT mode

|         | AEO-004148  |                |            |

|---------|-------------|----------------|------------|

| DOCC IP | ARTES 4     |                |            |

| DOCC II | FECHA/DATE: | EDICIÓN/ISSUE: | PÁG./PAGE: |

|         | 14/01/02    | 01             | 37 / 95    |

When DHS basic modem operates in CT mode, selection of the buses is performed according to the following table:

| Nominal Bus<br>Selection Request Input | Redundant Bus<br>Selection Request Input | Selected Bus |

|----------------------------------------|------------------------------------------|--------------|

| Not-asserted                           | Not-asserted                             | N-Bus        |

| Asserted                               | Not-asserted                             | N-Bus        |

| Not-Asserted                           | Asserted                                 | R-Bus        |

| Asserted                               | Asserted                                 | N-Bus        |

Table 6.4 BSS selection matrix in CT modem

When OBDH basic modem operates in CT mode, selection of the Buses is performed according to the table 6.5.

| CITSEL Signal | Selected Bus |

|---------------|--------------|

| L             | R-Bus        |

| Н             | N-Bus        |

Table 6.5 Selection matrix in OBDH CT modem.

# AEO-004148 ARTES 4 FECHA/DATE: EDICIÓN/ISSUE: PÁG./PAGE: 14/01/02 01 38 / 95

## 6.3 OBDH BUS TERMINAL (DBI)

All these interfaces are available only for OBDH modem, if the line OBDHpDHSn is at low logic level all the outputs remain at low logic level.

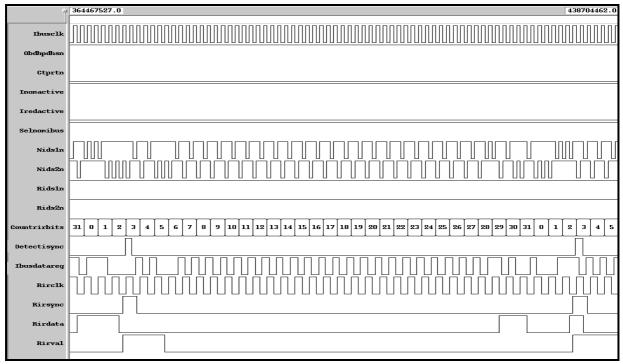

## **6.3.1 BAR1 Port (RIR)**

### CLOCK Signals

• IbusCLK

## Input Signals

- OBDHpDHSn

- CTpRTn

- TIMEOUTn

- INomActive

- IRedActive

- SelNomIBus

- CountRIRBits

- DetectISvnc

- IBusSync

- IBusDataReg

### Output Signals

- RIRCLK

- RIRDATA

- RIRVAL

- RIRSYNC

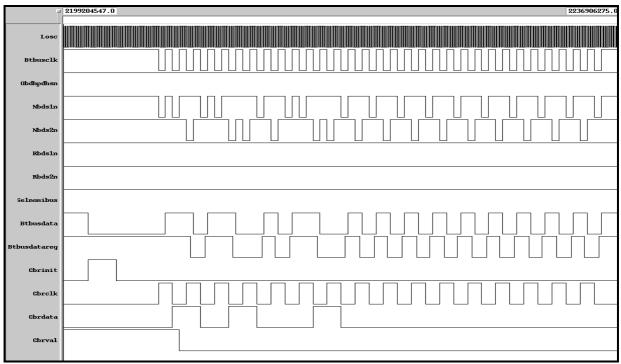

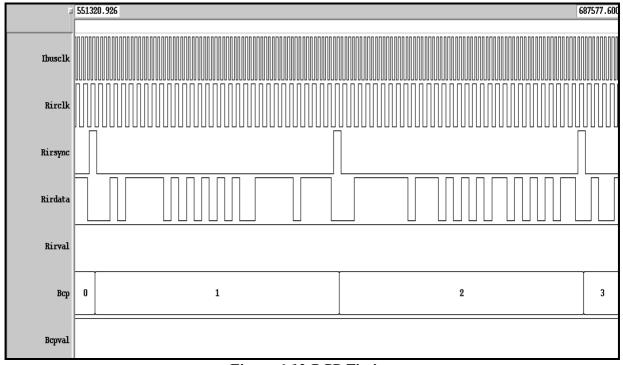

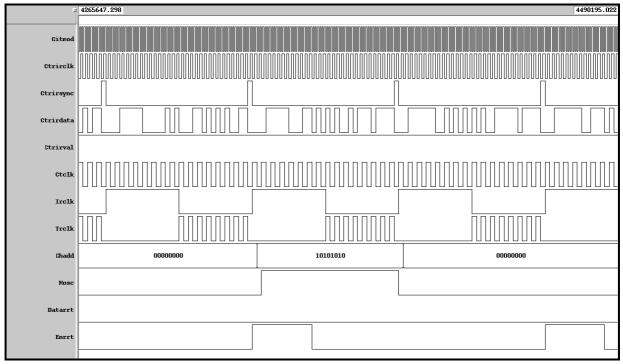

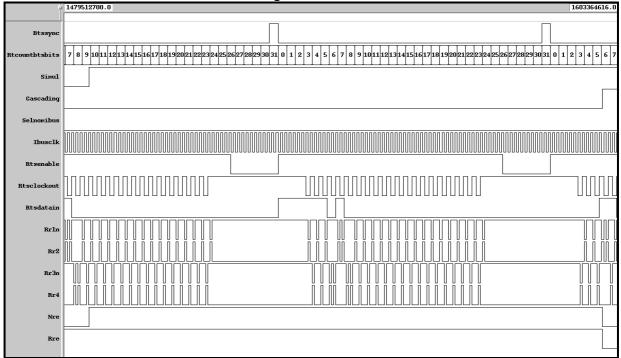

This interface behaves according to AD\_1 (page 7). But RIRVAL and RIRSYNC signals are delayed ½ bit. The reason is because this interface is synchronous with the IBusCLK signal. Thus RIRVAL changes in the Rising edge of clock (not in the falling edge). Otherwise, an asynchronous design must be performed.

The second difference with the AD\_1 applicable document is that the RIR signals are going to be divided in two sets of input and output signals. It must be noted that they were bidirectional signals in the OBT chip. The reason for this change against the original specification is that technological problems may occur due to the bidirectional clock signal RIRCLK.

This unit performs the following tasks, when active. It detects DetectISync, which indicates that a synchronisation pattern has been received. If so, a counter is started (CountRIRBits) and the signal RIRCLK is put in phase according to page 7 in AD\_1. After that, a sequencer is activated. Data received through the IbusSync shift register are checked in order to:

| DOCC IP | AEO-004148 |                |            |

|---------|------------|----------------|------------|

|         | ARTES 4    |                |            |

|         |            | EDICIÓN/ISSUE: | PÁG./PAGE: |

|         | 14/01/02   | 01             | 39 / 95    |

- Detect Synchronisation patterns (Note that DetectISync signal occurs after RIRSYNC).

- Decodes incoming data and put it in the RIRDATA output signal.

- Detects invalid bits and deasserts, if necessary, the RIRVAL output signal.

•

This interface is active only under the following conditions:

- CTpRTn input signal is Low.

- OBDHpDHSn input signal is High.

- There is activity in one of the I-buses (nominal or redundant).

- The TIMEOUTn signal is asserted at high level logic state.

When one of the previous conditions doesn't occur the RIR output signals remains at inactive low level logic state.

The behaviour of this unit is reflected in the following figure.

Figure 6.7 BAR1 Timing

# AEO-004148 ARTES 4 FECHA/DATE: EDICIÓN/ISSUE: PÁG./PAGE: 14/01/02 01 40/95

### 6.3.2 BAR2 Port (RRR/CRR)

### CLOCK Signals

- LOSC

- RbusCLK (internal)

### Input Signals

- OBDHpDHSn

- NRDS1n

- NRDS2n

- RRDS1n

- RRDS2n

- SelNomIbus

- CRRINIT

### Output Signal

- RBusDataReg

- RBusData

- CRRCLK

- CRRDATA

- CRRVAL

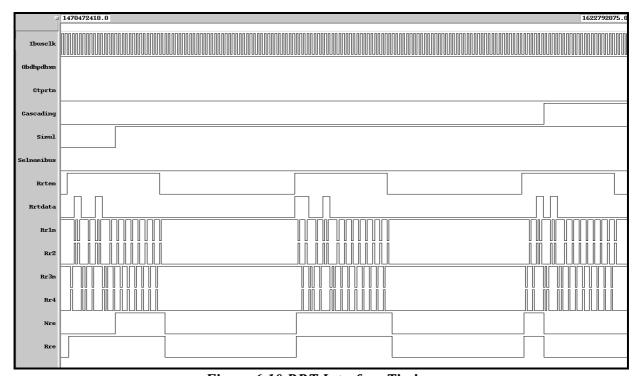

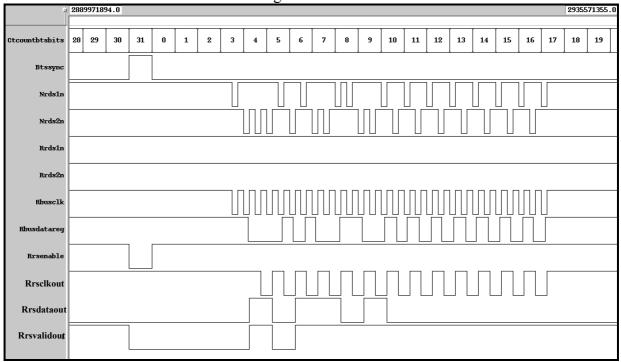

It must be noted that CRRVAL signal is delayed by ½ bit against the specification in AD\_1, page 8. The reason for this change is to perform a synchronous design that otherwise would be impossible.

This unit receives data from the R-bus and puts the incoming data in the RRR/CRR output signals.

This unit is divided in two submodules: the first one recovers data and clock from the R-bus Litton code, the second submodule generates the RRR/CRR signals. This interfaces works only when the signal OBDHpDHSn is at high level.

### **Clock and Data Recovering submodule**

R-bus clock is recovered by performing the logical "and" of the XRDS1n and XRDS2n input signals. The SelNomIBus input signal selects the nominal or redundant bus. R-bus Data is recovered by sampling the XRDS1n and XRDS2n input signals synchronously with the LOSC input oscillator. These signals are doubly registered in order to avoid metastability. The incoming data is put in the RBusDataReg register. This signal is captured in the RbusData register clocked by the RBusCLK internal clock. Thus, decoded data is produced synchronously with the RBusCLK signal.

| DOCC IP | AEO-004148              |                      |                           |

|---------|-------------------------|----------------------|---------------------------|

|         | ARTES 4                 |                      |                           |

|         | FECHA/DATE:<br>14/01/02 | EDICIÓN/ISSUE:<br>01 | <b>PÁG./PAGE:</b> 41 / 95 |

### RRR/CRR interface submodule

In this submodule the CRRINIT input signals asynchronously resets the CRRCLK, CRRDATA, and CRRVALID signals. Then this submodule is ready to start a transmission.

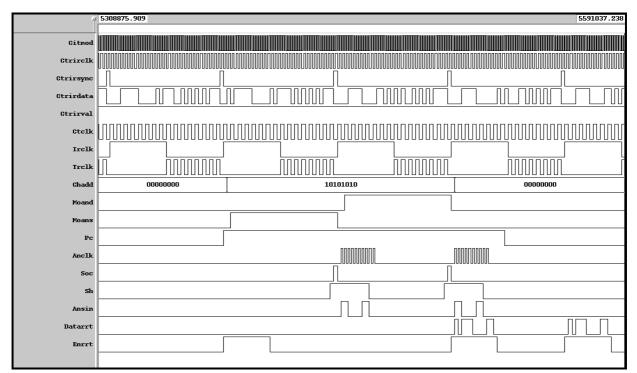

CRRCLK and CRRDATA are produced in the falling edge of RBusCLK. CRRVAL is produced in the Rising edge of the RBusCLK clock. Thus, CRRVAL signal is delayed by ¼ bit against the specification in AD\_1, page 8. CRRDATA is generated by sampling the RbusData signal value. CRRVAL is generated by checking the RbusData and RbusDataReg registers, in order to detect invalid Litton codes. The behaviour of this unit is illustrated in the figure below.

Figure 6.8 BAR2 Timing.

## AEO-004148 ARTES 4 FECHA/DATE: EDICIÓN/ISSUE: PÁG./PAGE: 14/01/02 01 42/95

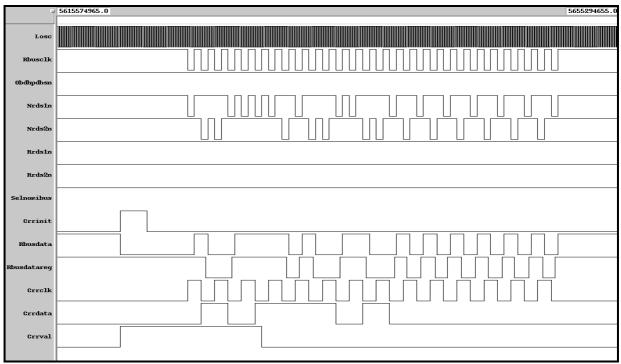

### 6.3.3 BAR3 Port (RBR/CBR)

### CLOCK Signals

- LOSC

- BTBusCLK (internal)

### Input Signals

- OBDHpDHSn

- CTpRTn

- NBDS1n

- NBDS2n

- RBDS1n

- RBDS2n

- SelNomIbus

- CBRINIT

### Output Signals

- BTBusDataReg

- BTBusData

- CBRCLK

- CBRDATA

- CBRVAL

This module makes its function when the modem works as OBDH.

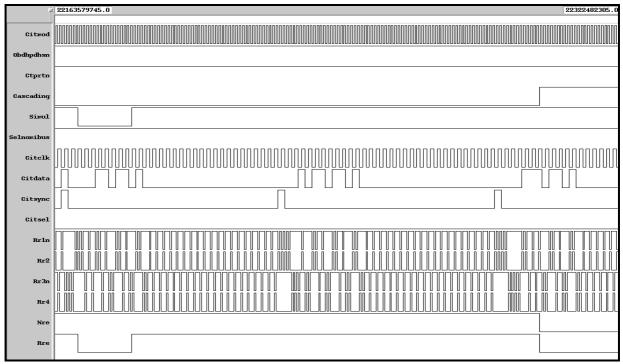

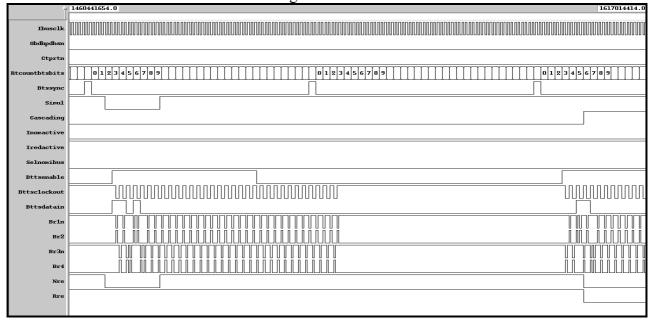

It must be noted that CBRVAL signal is delayed by ¼ bit against the specification in AD\_1, page 8. The reason for this change is to perform a synchronous design that otherwise would be impossible.

This unit receives data from the BT-bus and puts the incoming data in the RBR/CBR output signals. It is divided in two submodules: the first one recovers data and clock from the BT-bus Litton code, the second submodule generates the RBR/CBR signals.

### Clock and Data Recovering submodule

R-bus clock is recovered by performing the logical "and" of the XBDS1n and XBDS2n input signals. The SelNomIBus input signal selects the nominal or redundant bus. Then, the BTBusCLK internal clock signal is generated.

BT-bus Data is recovered by sampling the XBDS1n and XBDS2n input signals synchronously with the LOSC input oscillator. These signals are doubly registered in order to avoid metastability. SelNomIBus input signals selects the nominal or redundant input data. Thus the incoming data is put in the BTBusDataReg register. This signal is captured in the BTbusData register clocked by the BTBusCLK internal clock. Then, decoded data is produced synchronously with the BTBusCLK signal.

|         | AEO-004148  |    |            |

|---------|-------------|----|------------|

| DOCC IP | ARTES 4     |    |            |

|         | FECHA/DATE: |    | PÁG./PAGE: |

|         | 14/01/02    | 01 | 43 / 95    |

### RBR/CBR interface submodule

In this submodule the CBRINIT input signals asynchronously resets the CBRCLK, CBRDATA, and CBRVALID signals and force a known state before the transmission is performed.

CBRCLK and CBRDATA are generated in the falling edge of BTBusCLK. CBRVAL is produced in the Rising edge of this clock. Thus, CBRVAL signal is delayed by ¼ bit against the specification in AD\_1, page 8. CBRDATA is generated by sampling the BTbusData signal value. CBRVAL is deasserted by checking the BTbusData and BTbusDataReg registers in order to detect invalid Litton codes. The behaviour of this unit is illustrated in the figure below:

Figure 6.9 BAR3 Timing.

# AEO-004148 ARTES 4 FECHA/DATE: EDICIÓN/ISSUE: PÁG./PAGE: 14/01/02 01 44/95

### 6.3.4 BAT1 Port (RRT/CIT)

### CLOCK Signals

- CITMOD

- IBusCLK.

### Input Signals

- OBDHpDHSn

- CTpRTn

- CASCADING

- SIMUL

- SelNomIbus

- RRTEN

- RRTDATA

- CITCLK

- CITDATA

- CITSYNC

- CITSEL

### Output Signals

- NRE

- RRE

- RR1n

- RR2

- RR3n

- RR4

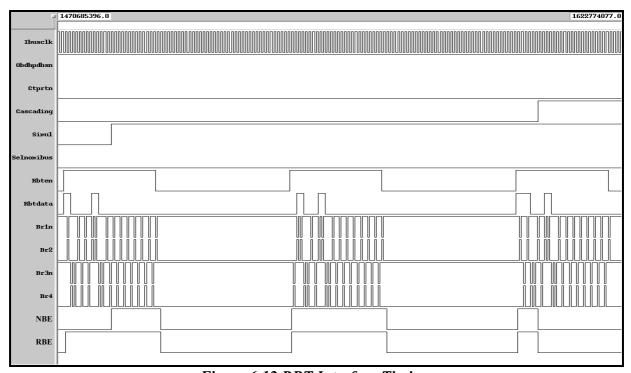

This unit implements exactly the functionality described in [AD\_1] document (pages 5 and 6). The only difference is that the signal CITINV and its function, explained in that document, has been remove from the design described in this pages.

This unit is composed of three submodules:

- RRT interface module.

- CIT interface module.

- I/R-Bus transmission interface module.

### **RRT** interface module

This submodule is active when the ASIC performs the function of an OBDH's remote terminal (OBDHpDHSn = '1' and CTpRTn = '0'). The RRTEN and RRTDATA incoming signals are sampled with the IBusCLK clock. When RRTEN is at high level, the data presented in RRTDATA is passed to the I/R-Bus transmission interface submodule.

## AEO-004148 ARTES 4 FECHA/DATE: EDICIÓN/ISSUE: PÁG./PAGE: 45 / 95 14/01/02 01 45 / 95

### CIT interface module.

This submodule is on for an OBDH bus controller (OBDHpDHSn = '1' and CTpRTn = '1') and the CITMOD input signal is the active clock. The CITCLK signal has two times the period of CITMOD and is used to enable capture of CITDATA when stable. When a pulse is introduced by the CITSYNC input a synchronisation pattern is sent to the bus. If the CITDATA value in that moment is '0' then is sent the normal sync pattern ("HOHOHOLOLOLO"), otherwise if it's '1' is generated the inverted pattern ("LOLOLOHOHOHO"). The signal CITSEL is used to select the bus to transmit to in CT mode.

### I/R-Bus transmission interface module

This unit receives series of data from the RRT and CIT interfaces and puts them in the RR1n, RR2, RR3n, and RR4 output signals.

It controls also the generation of the NRE and RRE output signals. NRE and RRE take the following values: When CASCADING = '1' then both signals are always deasserted.

In CT mode (CTpRTn = '1'):

NRE is '1' if SIMUL is high, otherwise it takes the SelNomIbus value.

RRE is '1' if SIMUL is high, otherwise it takes the inverted value of SelNomIbus.

In RT mode (CTpRTn = '0'):

NRE and RRE take the same value as in CTpRTn but they are active high just when RRTEN is high.

I/R bus transmitted data is selected considering the following possibilities: OBDHpDHSn is '1' or '0' and CTpRTn is '1' or 0. In the following table selected data is described.

| OBDHpDHSn | CTpRTn | Source  |

|-----------|--------|---------|

| 1         | 1      | CITDATA |

| 1         | 0      | RRTDATA |

| 0         | 1      | ITSDATA |

| 0         | 0      | RTSDATA |

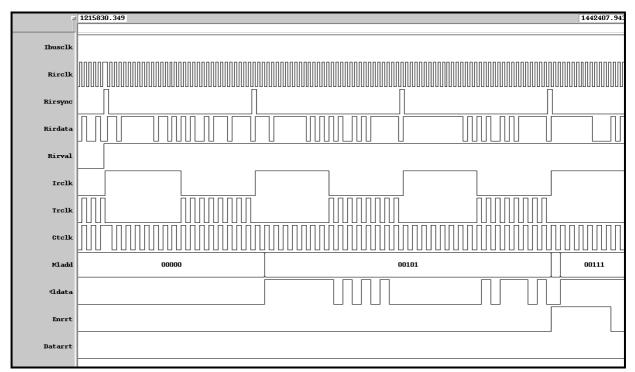

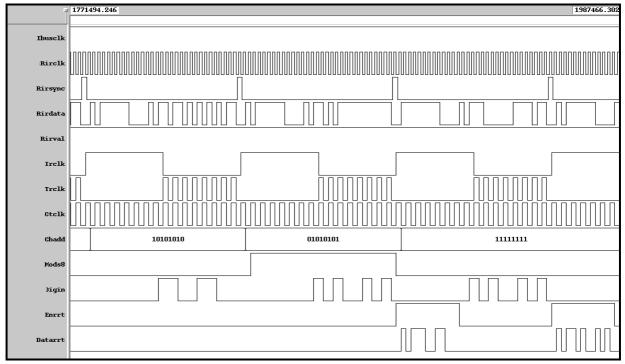

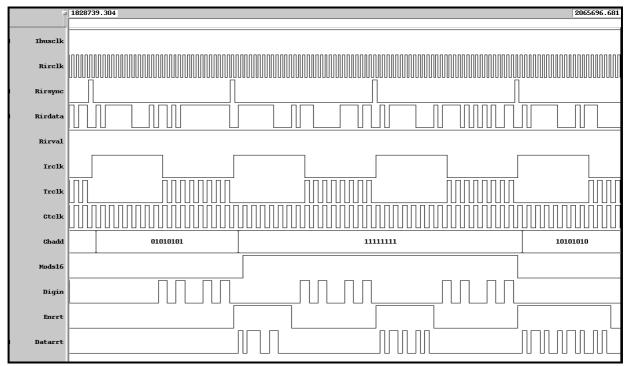

Table 6.6 I-Bus source Data.