Giltighet begränsad till Validity restricted to

Fördelning Distribution

Dokument ID Document ID P-ASIC-NOT-00122-SE

Frisläppt datum Date Released

2006-03-22

11

Dok.status Doc.Status

Sida Page

1(324)

Released Utgåva Issue

Utgåva Issue

Company Restricted

Alt. Dokument ID Alt. Document ID

Informationsklass Classification

PROJEKT PROJECT ASIC

# TITEL TITLE SCTMTC ASIC User's Manual

Utfärdat av Issued by Martin Rönnbäck

Godkänt av Approved by Håkan Kärnhagen

Funktion Function ASIC Object Manager

Funktion Function Project Manager

Datum *Date* 2006-03-14

This document or software is confidential to Saab Ericsson Space AB and must not:

a) be used for any purpose other than those for which it was supplied;

b) be copied or reproduced in whole or in part without the prior written consent of Saab Ericsson Space AB;

c) be disclosed to any third party without the prior written consent of Saab Ericsson Space AB.

## Saab Ericsson Space AB

Postadress Postal address

SE-405 15 Göteborg Sweden Telefon Telephone

+46 (0)31 735 00 00

Telefax

+46 (0)31 735 40 00

Organisationsnummer Registered number 556134-2204 Momsreg.-nr VAT No

SE556134220401

Sida Page Dokument ID Document ID

2 P-ASIC-NOT-00122-SE

Frisläppt datum Date Released 2006-03-22

Utgåva *Issue* 11 Informationsklass *Classification*Company Restricted

#### **SUMMARY**

The SCTMTC ASIC User's Manual defines how the SCTMTC ASIC is to be used.

This document will eventually be replaced by the SCTMTC ASIC data sheet produced by Atmel.

**Disclaimer:** Saab Ericsson Space AB assumes no responsibility for any errors which may appear in this document or the corresponding device, reserves the right to make changes to detailes herein at any time without notice, and does not make any commitment to update the information contained herein. No licenses to patents or other intellectual property of Saab Ericsson Space AB are granted by the company in connection with this document and device, expressly or by implication.

#### **DOCUMENT CHANGE RECORD**

Changes between issues are marked with an outside-bar.

| Issue | Date       | Paragraphs affected                  | Change information                                                           |

|-------|------------|--------------------------------------|------------------------------------------------------------------------------|

| 3     | 2003-02-07 |                                      | Updated before the Design Review                                             |

| 4     | 2003-02-26 | See change bars                      | Updated after the Design Review                                              |

| 5     | 2003-05-22 | 5.4.3, 6.3.2, 6.10.3                 | Updated description of NewFar interrupt                                      |

|       |            | 6.10, 6.10.1                         | Added power-on reset register                                                |

|       |            | 7.1.2                                | Updated TAP register                                                         |

|       |            | 7.1.3                                | Updated description of reset                                                 |

|       |            | 7.10                                 | Updated signal list                                                          |

|       |            | 7.17                                 | Added pinout                                                                 |

|       |            | 4.7, 4.8.1, 4.9.6, 5.1.2, 5.4.1,     | Updated or added section                                                     |

|       |            | 5.4.2, 5.4.3, 5.4.5, 5.4.6, 5.4.9,   | •                                                                            |

|       |            | 6.1.3, 6.2.2, 6.3.2, 6.3.3, 6.4.1,   |                                                                              |

|       |            | 6.4.2, 6.4.3, 6.5.2, 6.5.3, 6.5.5,   |                                                                              |

|       |            | 6.6.2, 6.9.2, 6.10, 6.10.1, 6.10.2   | ,                                                                            |

|       |            | 6.10.3, 6.10.5, 6.10.6, 6.10.7,      |                                                                              |

|       |            | 6.11.3, 7.5.1, 7.6.1, 7.6.2, 7.10,   |                                                                              |

|       |            | 7.10.2, 7.10.3, 7.10.4, 7.10.7,      |                                                                              |

|       |            | 7.10.8, 7.10.9, 7.11, 7.12, 7.13,    |                                                                              |

|       |            | 7.14, 7.15, 7.16                     |                                                                              |

| 6     | 2003-09-09 | Marked                               | Updates from review                                                          |

| 7     | 2003-11-03 | 5.4.2.3                              | Flush usage description updated                                              |

|       |            | 5.4.2.5, 6.2.2, 6.10.2.5, 7.2.1.5    | EEPROM write cycle anomaly                                                   |

|       |            | 5.4.3.1.1.3                          | Dynamic mode anomaly                                                         |

|       |            | 6.2.1, 6.2.2, 6.5, 6.6, 6.7, 6.8, 6. | 9 Clarification regarding initialisation and functions available to the user |

|       |            | 6.2.3.7, 6.2.3.8, 6.10.2             | Correctable error addresses anomaly                                          |

|       |            | 6.8, 6.10.8                          | Updated available functions in SPW module                                    |

|       |            | 6.10.7.3                             | CfE flag in TME TM Status Register anomaly                                   |

|       |            | 7.1.2.1                              | Corrected hexadecimal value for TAP register                                 |

|       |            | 7                                    | Added timing paramters                                                       |

|       |            | 7.12                                 | Updated operating conditions                                                 |

|       |            |                                      |                                                                              |

a) be used for any purpose other than those for which it was supplied;

b) be copied or reproduced in whole or in part without the prior written consent of Saab Ericsson Space AB;

c) be disclosed to any third party without the prior written consent of Saab Ericsson Space AB.

Sida Page Dokument ID Document ID Frisläppt datum Date Released Informationsklass Classification Utgåva Issue P-ASIC-NOT-00122-SE 2006-03-22 11 Company Restricted

| Issue | Date         | Paragraphs affected                        | Change information                                                                       |

|-------|--------------|--------------------------------------------|------------------------------------------------------------------------------------------|

| 8     | 2004-02-13   | 1                                          | Added clarifying statement                                                               |

|       |              | 4.10                                       | Updated list of abbreviations                                                            |

|       |              | 5.1.2, 5.3, 5.4.3.1.1, 7.3.1.5, 7.10, 7.17 | Updated description of selection mechanisms                                              |

|       |              |                                            | Updated description of non-volatile memories                                             |

|       |              | 5.4.5.1                                    | Added clarification                                                                      |

|       |              | 5.4.5.5, 7.5.3.1                           | Clarified ussage of the status interface                                                 |

|       |              | 5.4.7.3.2.1                                | Updated polarity of Synchronisation flag                                                 |

|       |              | 5.4.7.12, 6.10.7.5                         | Clarified clock frequency relations                                                      |

|       |              | 5.4.8.2                                    | Added clarification regarding bandwidth from SPW to TME                                  |

|       |              | 6.1.4.2                                    | Clarified description of refresh                                                         |

|       |              | 6.1.4.3                                    | Updated usage constraints                                                                |

|       |              | 6.2.2.5.1                                  | Clarified scrubber end address configuration                                             |

|       |              | 6.2.3.7                                    | Clarified register behaviour                                                             |

|       |              | 6.2.4.1                                    | Updated usage constraint                                                                 |

|       |              | 6.2.5.1                                    | Added example                                                                            |

|       |              | 6.3.2.1                                    | Clarified interrupt usage                                                                |

|       |              | 6.7.2.2.3                                  | Added clarification                                                                      |

|       |              | 6.8                                        | Clarified SPW configuration                                                              |

|       |              | 6.10                                       | Clarified usage of unused register bits                                                  |

|       |              | 6.10.1.4                                   | Updated register access type and added note                                              |

|       |              | 6.10.2.4                                   | Added clarification                                                                      |

|       |              | 6.10.2.5                                   | Added clarification regarding timeout                                                    |

|       |              | 6.11.1                                     | Updated configuration block memory                                                       |

|       |              | 7.18                                       | Added JTAG bit order                                                                     |

| 0     | 2004-05-07   | 6.1.3.7                                    | Added section about power-on reset status                                                |

| 7     | 9 2004-05-07 | 6.2.2.7                                    | Clarified buffer flush usage                                                             |

|       |              | 7.5.3.1                                    | Added clarification about interface disabling                                            |

| 10    | 2005-03-03   |                                            |                                                                                          |

| 10    | 2003-03-03   | 5.4.1.4.3, 5.4.7.2, 6.7.2.1,<br>6.10.7.2   | Changed term for idle packets on the telemetry link to Idle Packets                      |

|       |              |                                            | Clarified relation between VC buffer size and                                            |

|       |              | 5.4.7.2, 6.7.2.1                           |                                                                                          |

|       |              | 5 4 7 2 4                                  | maximum TM packets for that VC<br>Clarified VC ID for idle frames                        |

|       |              | 5.4.7.3.4                                  |                                                                                          |

|       |              | 6.2.3.8                                    | Added section about EDAC errors during read-fill                                         |

|       |              | 6.10                                       | Depict 32 bits in all register descriptions                                              |

|       |              | 6.10.2.3                                   | Clarified that register contents of PIM_FFCEAR are unaffected by a write                 |

|       |              | 6.10.2.5                                   | Clarified that error trap registers are cleared when PIM_ET is written                   |

|       |              | 6.10.2.5                                   | Added description of PIM_EI register contents                                            |

|       |              | 6.10.6.3                                   | Clarified differences between CPDM_SRR and CPDM_SR                                       |

|       |              | 6.10, 6.10.7.3                             | Removed TME TM Status Register                                                           |

|       |              | 6.11.3.1                                   | Added reference to section where the contents of the look-up table entries are described |

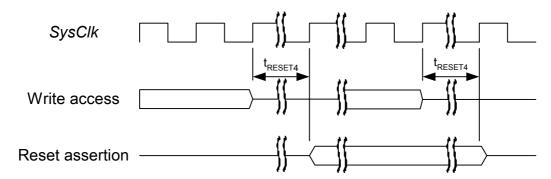

|       |              | 7.2.2                                      | Added note about WEN behaviour when write waitstates is set to 0                         |

| 11    | 2006-03-14   | 5.4.5.2                                    | Updated CSEL action table                                                                |

|       |              | 6.2.3.3, 6.10.2.5                          | Clarified that TME does not affect error trap                                            |

|       |              | 6.6.3.3                                    | Clarified CPDM abort delay                                                               |

|       |              | 6.10.2.5                                   | Removed TME from error trap table                                                        |

|       |              | 6.10.5.4                                   | Added note about CS_RSTAT Timeout bit                                                    |

|       |              | 7.7.1.3                                    | Added TimeStrobe timing                                                                  |

|       |              |                                            |                                                                                          |

This document or software is confidential to Saab Ericsson Space AB and must not:

a) be used for any purpose other than those for which it was supplied;

b) be copied or reproduced in whole or in part without the prior written consent of Saab Ericsson Space AB;

c) be disclosed to any third party without the prior written consent of Saab Ericsson Space AB.

| TABLE          | OF CONTENTS                                                | PAGE |

|----------------|------------------------------------------------------------|------|

| 1              | INTRODUCTION                                               | 8    |

| 2              | SCOPE                                                      | 8    |

| 2.1            | How to read this manual                                    |      |

| 2.2            | Turbo code patent                                          |      |

| 3              | DOCUMENTS                                                  | 0    |

| 3.1            | Applicable Documents                                       |      |

| 3.1            | Reference Documents                                        |      |

| J. <b>2</b>    |                                                            |      |

| 4              | DEFINITIONS                                                |      |

| 4.1            | Requirement Numbering                                      |      |

| 4.2            | Bit Numbering                                              |      |

| 4.3            | Names                                                      |      |

| 4.4            | Radix                                                      |      |

| 4.5<br>4.6     | Signal Names                                               |      |

| 4.0<br>4.7     | Externally Accessible Register Names Primitive Polynomials |      |

| 4.7            | Terminology                                                |      |

| 4.8.1          | General SCTMTC ASIC terminology                            |      |

| 4.9            | Data structures                                            |      |

| 4.9.3          | Packet Telecommand Decoder (PDEC3) specific                |      |

| 4.9.4          | Command Pulse Distribution Module (CPDM) specific          |      |

| 4.9.7          | Packet Telemetry Encoder (TME) specific                    |      |

| 4.9.8          | SpaceWire (SPW) specific                                   | 26   |

| 4.9.9          | Control Interface (CI) specific                            | 27   |

| 4.10           | Abbreviations                                              | 29   |

| 5              | FUNCTIONAL OVERVIEW                                        | 31   |

| 5.1            | System Overview                                            |      |

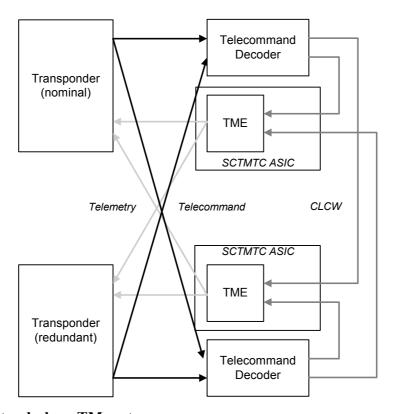

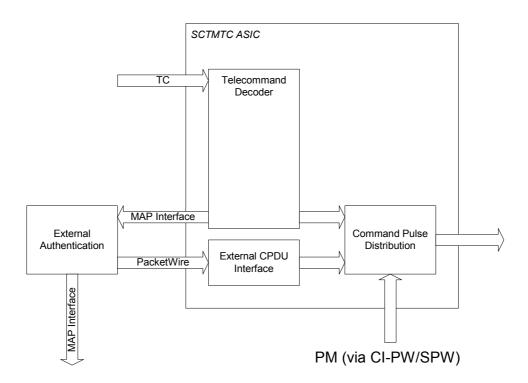

| 5.1.1          | Examples of systems using the SCTMTC ASIC                  |      |

| 5.1.2          | Compliance and compatibility with standards                |      |

| 5.2            | Functions                                                  | 39   |

| 5.3            | Interfaces                                                 | 41   |

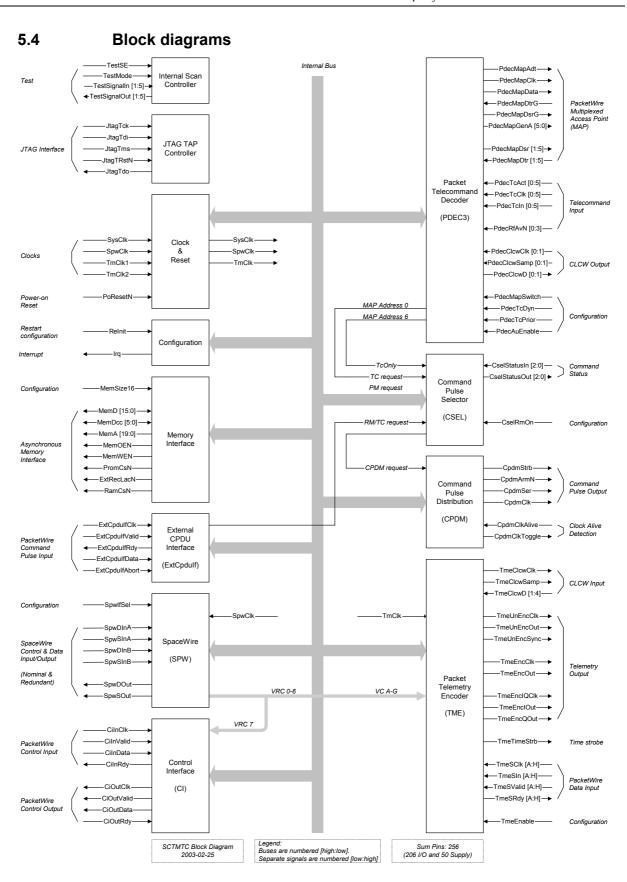

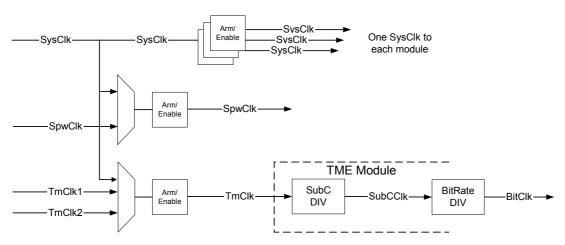

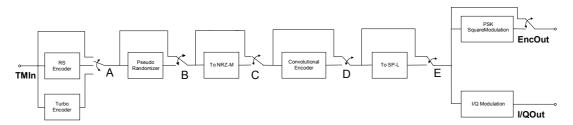

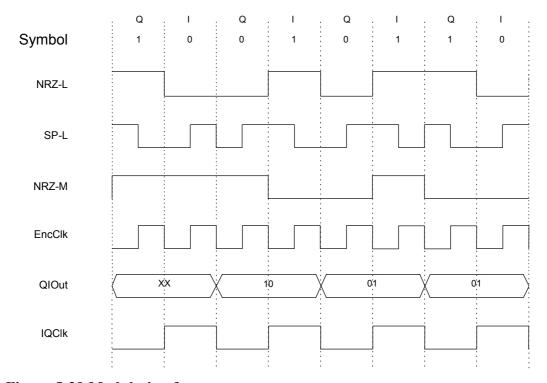

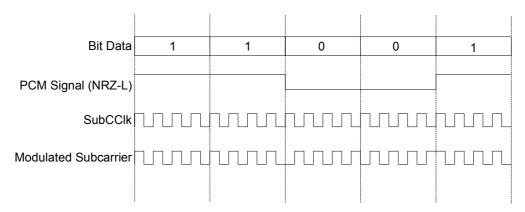

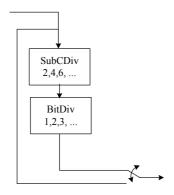

| 5.4            | Block diagrams                                             |      |

| 5.4.1          | General SCTMTC ASIC Functions                              |      |

| 5.4.2          | Memory Interface                                           |      |

| 5.4.3          | Packet Telecommand Decoder Module (PDEC3)                  |      |

| 5.4.4          | External CPDU Interface Module (ExtCpduIf)                 |      |

| 5.4.5          | CPDM Selector Module (CSEL)                                |      |

| 5.4.6<br>5.4.7 | Command Pulse Distribution Module (CPDM)                   |      |

| 5.4.7<br>5.4.8 | Packet Telemetry Encoder Module (TME)                      |      |

| 5.4.8<br>5.4.9 | Control Interface Module (CI)                              |      |

| J. T.J         | Control interface Module (C1)                              | 143  |

| 6              | SOFTWARE INTERFACE                                         | 126  |

| 6.1            | General SCTMTC ASIC Functions                              | 126  |

|                |                                                            |      |

a) be used for any purpose other than those for which it was supplied;

b) be copied or reproduced in whole or in part without the prior written consent of Saab Ericsson Space AB;

c) be disclosed to any third party without the prior written consent of Saab Ericsson Space AB.

Frisläppt datum Date Released

2006-03-22

Utgåva Issue

11

Dokument ID Document ID

P-ASIC-NOT-00122-SE

| 6.1.1 | Internal Scan Controller block             | 126 |

|-------|--------------------------------------------|-----|

| 6.1.2 | Test Access Port (TAP) block               |     |

| 6.1.3 | Clock and Reset (CAR) block                |     |

| 6.1.4 | Configuration block                        |     |

| 6.2   | Memory Interface                           |     |

| 6.2.1 | Initialisation                             |     |

| 6.2.2 | Operation/Usage                            |     |

| 6.2.3 | Error Handling                             |     |

| 6.2.4 | Usage Constraints                          |     |

| 6.2.5 | Examples                                   |     |

| 6.3   | Packet Telecommand Decoder Module (PDEC3)  |     |

| 6.3.1 | Initialisation                             |     |

| 6.3.2 | Operation/Usage                            |     |

| 6.3.3 | Error Handling                             |     |

| 6.3.4 | Usage Constraints                          |     |

| 6.3.5 | Examples                                   |     |

| 6.4   | External CPDU Interface Module (ExtCpduIf) |     |

| 6.4.1 | Initialisation                             |     |

| 6.4.2 | Operation/Usage                            |     |

| 6.4.3 | Error Handling                             |     |

| 6.4.4 | Usage Constraints                          |     |

| 6.5   | CPDM Selector Module (CSEL)                |     |

| 6.5.1 | Initialisation                             |     |

| 6.5.2 | Operation/Usage                            |     |

| 6.5.3 | Error Handling                             |     |

| 6.5.4 | Usage Constraints                          |     |

| 6.5.5 | Examples                                   |     |

| 6.6   | Command Pulse Distribution Module (CPDM)   |     |

| 6.6.1 | Initialisation                             |     |

| 6.6.2 | Operation/Usage                            |     |

| 6.6.3 | Error Handling                             |     |

| 6.6.4 | Examples                                   |     |

| 6.7   | Packet Telemetry Encoder Module (TME)      |     |

| 6.7.1 | Initialisation                             |     |

| 6.7.2 | Operation/Usage                            |     |

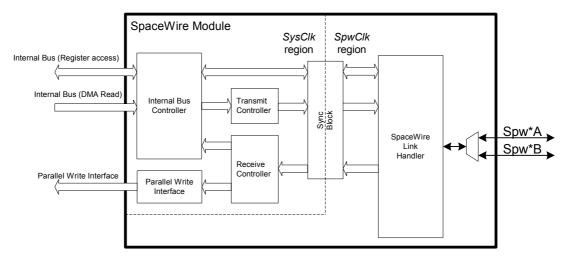

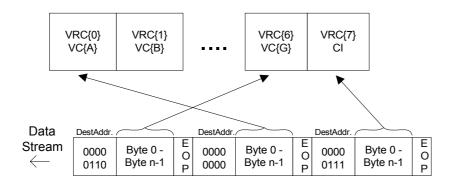

| 6.8   | SpaceWire Module (SPW)                     |     |

| 6.8.1 | Initialisation                             |     |

| 6.8.2 | Operation/Usage                            |     |

| 6.8.3 | Error Handling                             |     |

| 6.8.4 | Usage Constraints                          |     |

| 6.8.5 | Examples                                   | 183 |

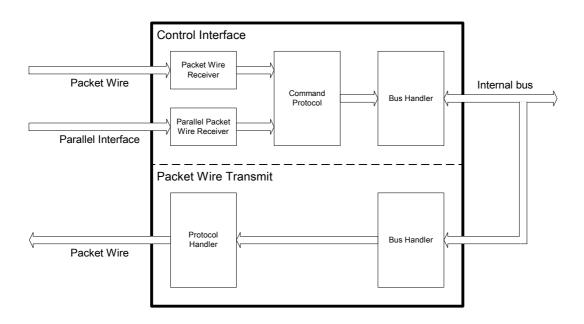

| 6.9   | Control Interface Module (CI)              | 185 |

| 6.9.1 | Initialisation                             |     |

| 6.9.2 | Operation/Usage                            |     |

| 6.9.3 | Error Handling                             |     |

| 6.9.4 | Usage Constraints                          |     |

| 6.9.5 | Examples                                   |     |

| 6.10  | Register Definition Summary                |     |

Sida Page

5

Informationsklass Classification

Company Restricted

a) be used for any purpose other than those for which it was supplied;

b) be copied or reproduced in whole or in part without the prior written consent of Saab Ericsson Space AB; c) be disclosed to any third party without the prior written consent of Saab Ericsson Space AB.

Dokument ID Document ID

Sida Page

| Sida Page | Dokument ID Document ID P-ASIC-NOT-00122-SE | Frisläppt datum Date Released 2006-03-22 | Utgåva <i>Issue</i><br>11 | Informationsklass Classification<br>Company Restricted |

|-----------|---------------------------------------------|------------------------------------------|---------------------------|--------------------------------------------------------|

| 6.10      | 0.1 General SCTM                            | TC ASIC registers                        |                           | 200                                                    |

| 6.10      |                                             | ce registers                             |                           |                                                        |

| 6.10      |                                             | mand Decoder Module (                    |                           |                                                        |

| 6.10      |                                             | Interface Module (ExtC                   |                           |                                                        |

| 6.10      |                                             | Module (CSEL) register                   |                           |                                                        |

| 6.10      |                                             | Distribution Module (C                   |                           |                                                        |

| 6.10      | 0.7 Packet Telemetr                         | y Encoder Module (TM                     | E) registers              | 235                                                    |

| 6.10      |                                             | ule (SPW) registers                      |                           |                                                        |

| 6.10      | -                                           | e Module (CI) registers.                 |                           |                                                        |

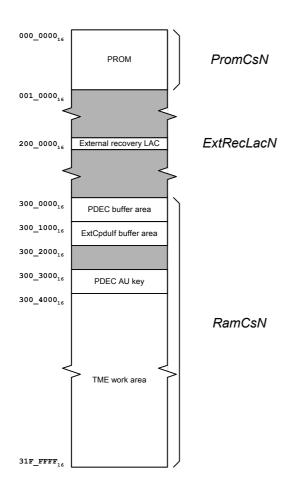

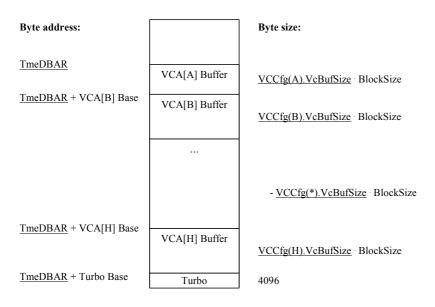

| 6.1       | 1 Memory Usage as                           | nd Mapping                               |                           | 257                                                    |

| 6.1       |                                             | lock memory usage                        |                           |                                                        |

| 6.1       |                                             | mand Decoder Module (                    |                           |                                                        |

| 6.1       |                                             | y Encoder (TME) memo                     |                           |                                                        |

| 7         |                                             | ERFACE                                   |                           |                                                        |

| 7.1       |                                             | C ASIC Functions                         |                           |                                                        |

| 7.1.      | 1 Internal Scan Co                          | ontroller block                          |                           | 273                                                    |

| 7.1.      | 2 Test Access Por                           | t (TAP) block                            |                           | 273                                                    |

| 7.1.      | 3 Clock and Reset                           | (CAR) block                              |                           | 274                                                    |

| 7.1.      | 4 Configuration b                           | lock                                     |                           | 275                                                    |

| 1.1.      | - · · · · · · · · · · · · · · · · · · ·     |                                          |                           |                                                        |

| 7.2       |                                             | <u>,</u>                                 |                           |                                                        |

| 7.2.      |                                             | ription                                  |                           |                                                        |

| 7.2.      | $\mathcal{E}$                               |                                          |                           |                                                        |

| 7.2.      | 1.1                                         | <u> </u>                                 |                           |                                                        |

| 7.3       |                                             | and Decoder Module (P                    | /                         |                                                        |

| 7.3.      |                                             | ription                                  |                           |                                                        |

| 7.3.      | C                                           |                                          |                           |                                                        |

| 7.3.      | 11                                          | e                                        |                           |                                                        |

| 7.3.      |                                             |                                          |                           |                                                        |

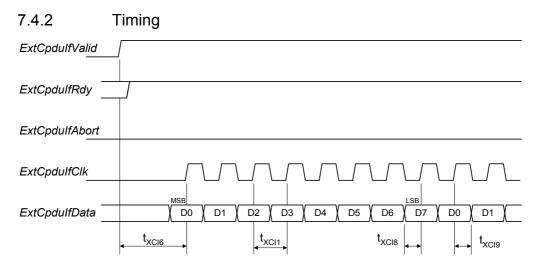

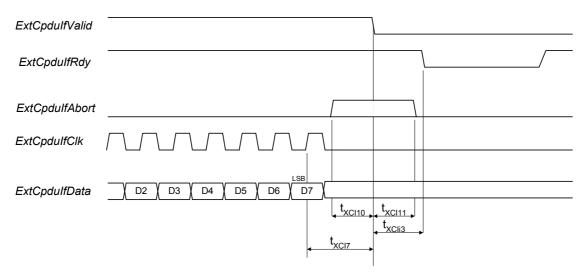

| 7.4       |                                             | nterface Module (ExtCpo                  |                           |                                                        |

| 7.4.      |                                             | ription                                  |                           |                                                        |

| 7.4.      | •                                           |                                          |                           |                                                        |

| 7.4.      |                                             |                                          |                           |                                                        |

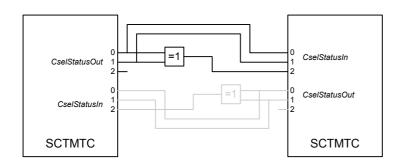

| 7.5       |                                             | Module (CSEL)                            |                           |                                                        |

| 7.5.      |                                             | ription                                  |                           |                                                        |

| 7.5.      | U                                           |                                          |                           |                                                        |

| 7.5.      | 1 1                                         | e                                        |                           |                                                        |

| 7.5.      |                                             |                                          |                           |                                                        |

| 7.6       |                                             | Distribution Module (CP                  |                           |                                                        |

| 7.6.      |                                             | ription                                  |                           |                                                        |

| 7.6.      | C                                           |                                          |                           |                                                        |

| 7.6.      |                                             |                                          |                           |                                                        |

| 7.7       |                                             | Encoder Module (TME)                     |                           |                                                        |

| 7.7.      |                                             |                                          |                           |                                                        |

| 7.7.      | _                                           |                                          |                           |                                                        |

| 7.7.      |                                             |                                          |                           |                                                        |

| 7.8       | SpaceWire Modu                              | le (SPW)                                 |                           | 301                                                    |

Frisläppt datum Date Released

Utgåva Issue

Informationsklass Classification

a) be used for any purpose other than those for which it was supplied;

b) be copied or reproduced in whole or in part without the prior written consent of Saab Ericsson Space AB;

c) be disclosed to any third party without the prior written consent of Saab Ericsson Space AB.

| Dokument ID Document ID P-ASIC-NOT-00122-S | Frisläppt datum Date Released SE 2006-03-22 | Utgåva <i>Issue</i><br>11 | Informationsklass Classification Company Restricted | Sida <i>Page</i><br>7 |

|--------------------------------------------|---------------------------------------------|---------------------------|-----------------------------------------------------|-----------------------|

| 7.8.1                                      | Functional Description                      |                           |                                                     | 301                   |

| 7.8.1  | Functional Description                            | 301 |

|--------|---------------------------------------------------|-----|

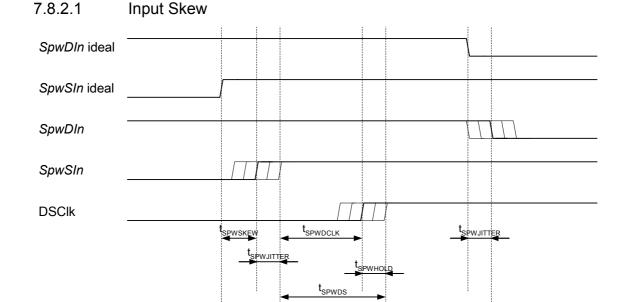

| 7.8.2  | Timing                                            | 301 |

| 7.8.3  | Reset                                             | 303 |

| 7.9    | Control Interface Module (CI)                     | 304 |

| 7.9.1  | Functional Description                            | 304 |

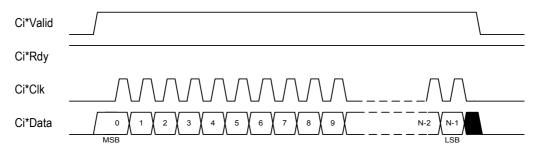

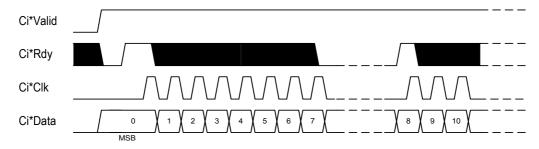

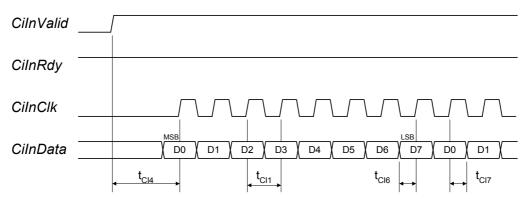

| 7.9.2  | Timing                                            | 305 |

| 7.9.3  | Reset                                             | 307 |

| 7.10   | Signal Definition Summary                         | 308 |

| 7.10.1 | General SCTMTC ASIC signals                       | 308 |

| 7.10.2 | Memory Interface                                  | 309 |

| 7.10.3 | Packet Telecommand Decoder Module (PDEC3) signals | 309 |

| 7.10.4 | External CPDU Interfaces (ExtCpduIf) signals      | 311 |

| 7.10.5 | CPDM Selector Module (CSEL) signals               | 311 |

| 7.10.6 | Command Pulse Distribution Module (CPDM) signals  | 311 |

| 7.10.7 | Packet Telemetry Encoder Module (TME) signals     | 312 |

| 7.10.8 | SpaceWire Module (SPW) signals                    | 313 |

| 7.10.9 | Control Interface Module (CI) signals             | 313 |

| 7.11   | Absolute Maximum Ratings                          | 315 |

| 7.12   | Operating Conditions                              | 315 |

| 7.13   | Static Electrical Characteristics                 | 316 |

| 7.14   | Dynamic Electrical Characteristics                | 317 |

| 7.15   | Packaging                                         | 317 |

| 7.16   | Thermal Characteristics                           | 317 |

| 7.17   | Pinout                                            | 318 |

| 7.18   | JTAG Pin Order                                    | 321 |

a) be used for any purpose other than those for which it was supplied;

b) be copied or reproduced in whole or in part without the prior written consent of Saab Ericsson Space AB;

c) be disclosed to any third party without the prior written consent of Saab Ericsson Space AB.

Informationsklass Classification

8

Dokument ID Document ID P-ASIC-NOT-00122-SE Frisläppt datum Date Released 2006-03-22

Utgåva Issue 11

#### 1 INTRODUCTION

The Single Chip Telemetry and Telecommand (SCTMTC) ASIC is an integrated device providing on-board telemetry and telecommand services via standardised interfaces.

This document will eventually be replaced by the SCTMTC ASIC data sheet produced by Atmel.

#### 2 SCOPE

This User's Manual defines how the SCTMTC ASIC is to be used.

#### 2.1 How to read this manual

The document has been divided in four main chapters, describing the relevant data formats, the functionality, the software aspects and finally the hardware aspects. Each of these chapters has been partitioned into sub-chapters for each major module. Therefore, to fully appreciate the functionality of a module, e.g. the telecommand decoder, the corresponding sub-chapter in all the four main chapters should be read by the user. Note that some sub-chapters have been omitted since not carrying any specific data for the corresponding module.

#### 2.2 Turbo code patent

Implementers should be aware that a wide class of turbo codes is covered by a patent by France Télécom and Télédiffusion de France under US Patent 5,446,747 and its counterparts in other countries. Potential user agencies should direct their requests for licenses to:

Mr. Christian Hamon CCETT GIE/CVP 4 rue du Clos Courtel **BP59** 35512 CESSON SEVIGNE Cedex France

Tel: +33 2 99 12 48 05 Fax: +33 2 99 12 40 98

Dokument ID Document ID Frisläppt datum Date Released Utgåva Issue Informationsklass Classification Sida Page P-ASIC-NOT-00122-SE 2006-03-22 11 Company Restricted 9

#### 3 DOCUMENTS

The latest issue of a document is valid, if not specified.

#### 3.1 Applicable Documents

[TC\_STD] Packet Telecommand Standard

ESA PSS-04-107, issue 2, April 1992 Telecommand Decoder Specification

[TC\_SPEC] Telecommand Decoder Specification ESA PSS-04-151, issue 1, September 1993

[TM\_STD] Packet Telemetry Standard

ESA PSS-04-106, issue 1, January 1988

[TMCOD\_STD] Telemetry Channel Coding Standard

ESA PSS-04-103, issue 1, September 1989

[MOD\_STD] Radio Frequency and Modulation Standard,

ESA PSS-04-106, issue 1, December 1989

#### 3.2 Reference Documents

[JTAG] Standard Test Access Port and Boundary-Scan Architecture and Supplement

IEEE-STD-1149.1 and IEEE-STD-1149.1b

[CCSDS\_TC1] Telecommand – Part 1 – Channel Service

CCSDS 201.0-B-3, June 2000

[CCSDS\_TC2] Telecommand – Part 2 – Data Routing Service

CCSDS 202.0-B-3, June 2001

[CCSDS\_TC2.1] Telecommand – Part 2.1 – Command Operation Procedures CCSDS 202.1-B-2,

June 2001

[CCSDS\_TC3] Telecommand – Part 3 – Data Management Service

CCSDS 203.0-B-2, June 2001

[CCSDS TM] Packet Telemetry

CCSDS 102.0-B-5, November 2000

[CCSDS TMCOD] Telemetry Channel Coding

CCSDS 101.0-B-6, October 2002

[CCSDS\_TMSYNC] TM Synchronization and Channel Coding, CCSDS 131.0-R-1, Red Book, July

2002

[CCSDS\_TMLINK] TM Space Data Link Protocol, CCSDS 132.0-R-1, Red Book, December 2001 Space Packet Protocol, CCSDS 133-0-R-1, Red Book, December 2001 [CCSDS\_TCSYNC] TC Synchronization and Channel Coding, CCSDS 231.0-R-1, Red Book, July

2002

[CCSDS\_TCLINK] TC Space Data Link Protocol, CCSDS 232.0-R-1, Red Book, December 2001 SpaceWire - Links, Nodes, Routers and Networks, ECSS-E-50-12, Draft 4

Sida Page Dokument ID Document ID 10 P-ASIC-NOT-00122-SE

Frisläppt datum Date Released 2006-03-22

Utgåva *Issue* 11 Informationsklass Classification

Company Restricted

#### 4 DEFINITIONS

This section and the following subsections define the typographic and naming conventions used throughout this document.

#### 4.1 Requirement Numbering

Requirement numbering is inapplicable for this document.

#### 4.2 Bit Numbering

The following conventions are used for bit numbering:

- The Most Significant Bit (MSB) of a vector has the leftmost position.

- The Least Significant Bit (LSB) of a vector has the rightmost position.

- Unless otherwise indicated, the MSB of a vector has the highest bit number and the LSB the lowest bit number.

#### 4.3 Names

The following conventions are used for all names (for signals and registers some extra conventions are defined below):

- A name may never start with a digit; e.g. 1553 could instead be M1553.

- A dollar sign (\$) in a name is used as a wildcard representing a number. (If the dollar sign (\$) is used in a context it must then be defined somewhere else in the document)

- An asterisk (\*) in a name is used as a wildcard representing one or more characters.

#### 4.4 Radix

The following conventions is used for writing numbers:

- Binary numbers are indicated by the subscript "2", e.g. 12, 1011\_1010\_1011\_11102, 0100102 etc.

- Decimal numbers are indicated by the subscript "10", e.g. 67,872310, 4786010.

- Hexadecimal numbers are indicated by the subscript "16", e.g. E16, BABE16.

- Unless the Radix is explicitly declared as above the number should be considered to be decimal number.

#### 4.5 Signal Names

The following conventions are used for signal names:

- Signal names are written in Italics, e.g. SignalName.

- Active low signals have a capital N appended to their name, e.g. SignalNameN.

- Bus indices are indicated with brackets, e.g. SignalName[12:3].

- Signals maybe grouped into subsignals, e.g. SignalName.SubSignal.

- Signals with two functions are named with the name and then the first functionality followed by the second function, e.g. *SignalNameFunction1Function2N*. The second function is the valid when the signal is deasserted (thus the suffix *N* in the name).

P-ASIC-NOT-00122-SE

Frisläppt datum Date Released 2006-03-22

Utgåva *Issue* 11 Informationsklass *Classification*Company Restricted

Sida *Page* 11

#### 4.6 Externally Accessible Register Names

The following convention is used for externally accessible registers.

- Register names are underlined, e.g. <u>RegisterName</u>.

- Fields of a register are indicated by the name of the register and the field, separated by a period and underlined, e.g. <u>RegisterName.Field</u>.

#### 4.7 Primitive Polynomials

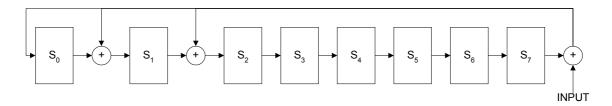

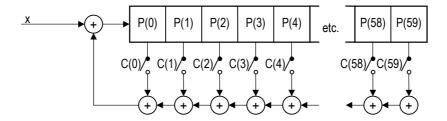

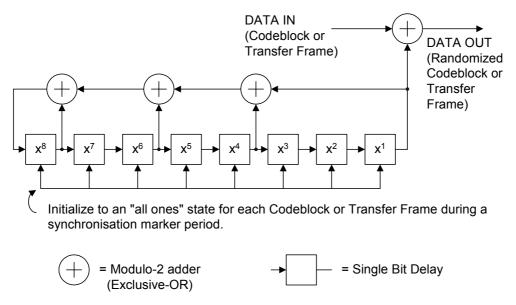

In this document, PN sequence generators are defined by their primitive polynomial on the following format:  $x^{k1} + x^{k2} + ... + x^{kN}$  The terms are integers representing the XOR positions of a generator in which the bit-shift moves in the direction of increasing bit number.

#### Example:

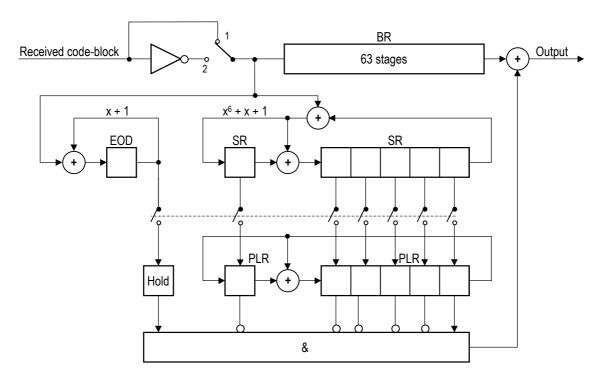

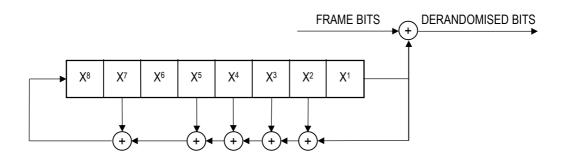

The primitive polynomial  $x^8 + x^2 + x^1 + 1$  defines the PN sequence generator seen in the figure below.

Figure 4-1 PN sequence generator defined by  $x^8 + x^2 + x^1 + 1$

Released

### Saab Ericsson Space AB

Sida Page Dokument ID Document ID Frisläppt datum Date Released Utgåva Issue Informationsklass Classification

12 P-ASIC-NOT-00122-SE 2006-03-22 11 Company Restricted

#### 4.8 Terminology

#### 4.8.1 General SCTMTC ASIC terminology

#### 4.8.1.1 General

ASIC Module An ASIC internal module

Issue an Interrupt The corresponding bit has been set in the pending interrupt register in

the ASIC/FPGA module

Reset Assertion An internal reset activation as seen by ASIC/FPGA modules

#### 4.8.1.2 Basic Data Types

Byte 8 bits of data HalfWord 16 bits of data Word 32 bits of data

#### 4.8.1.3 Registers

Register Read A read access to an externally accessible ASIC register

Register Write A write access to an externally accessible ASIC register

Set Indicates that the bit in the register is 1

Clear Indicates that the field or bit in the register is 0

Reset Indicates that the field or bit in the register is set to its default Value

(indicated in the Register definition chapter)

#### 4.8.1.4 Signals

Assert To put a signal into its active state. A signal is *asserted* when in its

active state

Deassert To put a signal into its inactive state. A signal is *deasserted* when in its

inactive state

#### 4.8.1.5 Direct memory access

DMA Channel A unit for accessing memory

DMA Error Signal to DMA Channel for failing memory access

DMA Read A transfer of data to a DMA channel from a DMA controller, e.g. read

data from memory

DMA Write A transfer of data from a DMA channel to a DMA controller, e.g. write

data to memory.

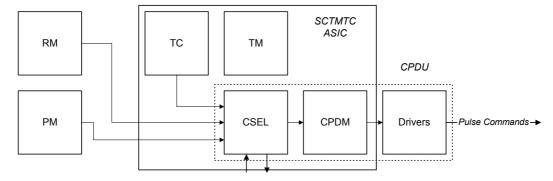

#### 4.8.1.6 CPDM Selector Module (CSEL) specific

Accept A request is accepted if it is allowed to execute in the mode the CSEL is

operating in.

Ground Request The telecommand decoder (TC) tries to send a CPDU Telecommand

Packet to the CPDM.

a) be used for any purpose other than those for which it was supplied;

b) be copied or reproduced in whole or in part without the prior written consent of Saab Ericsson Space AB;

c) be disclosed to any third party without the prior written consent of Saab Ericsson Space AB.

Dokument ID Document ID

| P-ASIC-NOT-00122-SE | 2006-03-22         | 11              | Company Restricted             | 13       |

|---------------------|--------------------|-----------------|--------------------------------|----------|

| Ongoing             | A sequence is ongo | oing when it h  | as been handed over to the CPI | OM and   |

| Sequence            | until the CPDM fro | ees the buffer. |                                |          |

| PM Request          | The Processor Moo  | dule (PM) trie  | s to send a CPDU Telecomman    | d Packet |

|                     | . ~~~              |                 |                                |          |

Utgåva Issue

Informationsklass Classification

Sida Page

to the CPDM.

Remote CPDM The CPDM connected to the remote CSEL.

Frisläppt datum Date Released

Remote CSEL A redundant CPDM Selector in a system, with which the CSEL

communicates.

Remote Status The copy of the status of the remote CSEL, kept by the CSEL.

RM Request The RM tries to send a CPDU Telecommand Packet to the CPDM.

#### 4.8.1.7 Command Pulse Distribution Module (CPDM) specific

Clean A packet is considered clean if it passes the clean check and, if it is of

Lockout type, it does not contain any invalid pulses.

Dirty If a packet is not clean, it is considered dirty.

Duration Unit for pulse output timing defined by [TC SPEC].

Free a buffer Freeing a buffer allows the originator of the CPDU Telecommand Packet

to reuse the memory area.

Free a buffer Freeing a buffer with error informs the originator of the CPDU

with error Telecommand Packet that an error occurred during the clean check, legal

check or packet execution.

Illegal A packet that is clean but not legal is considered illegal.

Legal A packet is considered legal if it passes the legal check.

Lockout type A packet of Lockout type does not have access to all pulses, if the packet

contains any of the inaccessible pulses, it is considered dirty.

Ground type A packet of Ground type has a status register separated from all other

packets.

Ongoing A pulse is considered ongoing as soon as the CPDM has asserted

CpdmArm.

Abort A packet can be aborted before all its pulses has been executed, this leads

to any ongoing pulse being shortened to a predefined value if it's

remaining execution time is longer than this time. All remaining pulses

are discarded.

#### 4.8.1.8 Packet Telemetry Encoder Module (TME) specific

Packet A packet is a data structure as defined by [TM STD] and [CCSDS TM].

Also referred to as Telemetry Packet, Source Packet or similar. Indicated in the Transfer Frame by the Data Field Synchronisation flag equals zero.

Data Block A data block is a general data structure. Indicated in the Transfer Frame

by the Data Field Synchronisation flag equals one.

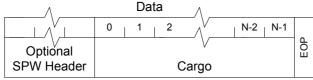

#### 4.8.1.9 SpaceWire Module (SPW) specific

Active Virtual receive or transmit channel, VRC or VTC\$ is currently receiving

VRC/VTC \$ or transmitting data.

Inactive No data is currently being received or transmitted on virtual receive or

VTC/VRC \$ transmit channel, VRC or VTC\$.

a) be used for any purpose other than those for which it was supplied;

b) be copied or reproduced in whole or in part without the prior written consent of Saab Ericsson Space AB;

Sida Page Dokument ID Document ID 14 P-ASIC-NOT-00122-SE

Frisläppt datum Date Released 2006-03-22

Utgåva *Issue* 11 Informationsklass Classification

Company Restricted

#### 4.9 Data structures

#### 4.9.3 Packet Telecommand Decoder (PDEC3) specific

#### 4.9.3.1 Command Link Transmission Unit Structure

The structure of the Command Link Transmission Unit (CLTU) processed by the PDEC3 is shown in Figure 4-2.

|          | Command Link Transmission Unit |        |          |                  |        |          |           |             |        |          |               |

|----------|--------------------------------|--------|----------|------------------|--------|----------|-----------|-------------|--------|----------|---------------|

| Start    |                                |        |          | Telecomm         | and C  | Code B   | lock Fiel | ld          |        |          | Tail Sequence |

| Sequence | TC Cod                         | e Bloc | k 1      | TC Cod           | e Bloo | ck 2     | etc.      | TC Cod      | de Blo | ck N     |               |

|          |                                | Err    | or       |                  | Eı     | ror      |           |             | Е      | rror     |               |

|          | on                             | Con    | itrol    | ou               | Co     | ntrol    |           | on          | Co     | ntrol    |               |

|          | Information                    | bits   | bit      | Information      | bits   | bit      |           | Information | bits   | pit      |               |

|          | ıforr                          |        | Filler   | ıforr            |        | Filler   |           | ıforr       |        | Filler   |               |

|          | <u></u>                        | Parity | <u>—</u> | <u></u>          | Parity | <u>1</u> |           | <u></u>     | Parity | <u>1</u> |               |

|          |                                | 7      |          |                  | 7      |          |           |             | 7      |          |               |

| 2 octets | 7 octets                       | 1 00   | ctet     | 7 octets 1 octet |        |          | 7 octets  | 1 (         | octet  | 8 octets |               |

|          | 8 0                            | ctets  |          | 8 00             | ctets  |          |           | 8 0         | octets |          |               |

Figure 4-2 Command Link Transmission Unit structure

A valid CLTU consists of

- The Start Sequence with the nominal value EB90<sub>16</sub>, and which marks the beginning of the CLTU.

- The Telecommand (TC) Code Block field with 2 to 147 TC Code Blocks, each consisting of seven Information octets and one Error Control octet. In the Error Control octet the Parity bits are a (63,56) modified Bose-Chaudhuri-Hocquenghem (BCH) code generated by the polynomial  $G(x) = x^7 + x^6 + x^2 + x^0$ , and the Filler bit shall nominally be zero.

- The Tail Sequence, which marks the end of the TC Code Block field. It is a TC Code Block with more than one bit-error, and with a Filler bit nominally being one.

#### 4.9.3.2 Telecommand Transfer Frame Structure

The structure of the Telecommand Transfer Frame together with the Fill octets is shown in Figure 4-3. The Information octets (i.e., without the Error Control octets) from all TC Code Blocks in a CLTU are concatenated to form a Telecommand Transfer Frame. Any leftover Information octets after the Frame, as determined by the Frame Length field in the Frame Header, are called Fill octets.

b) be copied or reproduced in whole or in part without the prior written consent of Saab Ericsson Space AB;

Dokument ID Document ID Frisläppt datum Date Released Utgåva Issue Informationsklass Classification Sida Page P-ASIC-NOT-00122-SE 2006-03-22 11 Company Restricted 15

| Concatenated Information octets from the CLTU Code Blocks |                                                                    |             |  |  |  |  |

|-----------------------------------------------------------|--------------------------------------------------------------------|-------------|--|--|--|--|

|                                                           |                                                                    | Fill octets |  |  |  |  |

| Frame Header                                              | Frame Header Frame Data field containing a Telecommand Frame Error |             |  |  |  |  |

|                                                           |                                                                    |             |  |  |  |  |

| 5 octets                                                  | 0 to 6 octets                                                      |             |  |  |  |  |

| N*7 octets ( $2 \le N \le 147$ )                          |                                                                    |             |  |  |  |  |

Figure 4-3 Telecommand Transfer Frame structure, also showing the Fill octets

The Telecommand Transfer Frame consists of:

- The Frame Header, further described in section 4.9.3.2.1.

- The Frame Data field, further described in section 4.9.3.2.2.

- The Frame Error Control field, which is a Cyclic Redundancy Code (CRC) used for detecting any remaining errors which may exist in the Transfer Frame. After initialising the encoder to all ones, it is generated over the entire Transfer Frame (except the Frame Error Control field) using the polynomial  $g(x) = x^{16} + x^{12} + x^5 + 1$ .

#### 4.9.3.2.1 Frame Header Structure

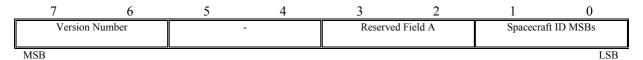

The structure of the Frame Header processed by the PDEC3 is shown in Figure 4-4.

|                   | Frame Header |                         |                     |                |                       |                |                             |

|-------------------|--------------|-------------------------|---------------------|----------------|-----------------------|----------------|-----------------------------|

| Version<br>Number | Bypass flag  | Control<br>Command flag | Reserved field<br>A | Spacecraft Id  | Virtual Channel<br>Id | Frame Length   | Frame<br>Sequence<br>Number |

| 2 bits 01         | 1 bit<br>2   | 1 bit<br>3              | 2 bits<br>45        | 10 bits<br>615 | 6 bits<br>05          | 10 bits<br>615 | 8 bits                      |

|                   | 2 octets     |                         |                     |                |                       | 2 octets       | 1 octet                     |

Figure 4-4 Frame Header structure

a) be used for any purpose other than those for which it was supplied;

b) be copied or reproduced in whole or in part without the prior written consent of Saab Ericsson Space AB;

Sida Page Dokument ID Document ID Frisläppt datum Date Released Utgåva Issue Informationsklass Classification

16 P-ASIC-NOT-00122-SE 2006-03-22 11 Company Restricted

The Frame Header consists of:

- The static fields, being the Version Number field, the Reserved field A, the Spacecraft Identifier field and the Virtual Channel Identifier field, and which are simply compared to static values stored in the external non-volatile memory. The Version Number field and Reserved field A should be set to 00<sub>2</sub> to be compliant with [TC\_STD].

- The Bypass flag and the Control Command flag, which are used to determine the Transfer Frame type. The possible combinations and their interpretation are shown in Table 4-1.

- The Frame Length field specifies the length of the TC Transfer Frame, with its value being (total number of octets in the Transfer Frame 1).

- The Frame Sequence Number field, which is denoted N(S). It is used differently depending on the Transfer Frame type:

- ♦ For AD Frames, this field is used by the FARM-1 for the sequence control.

- ♦ For BC and BD Frames, the 8-bit field shall be zero.

| Bypass flag | <b>Control Command flag</b> | Interpretation                     |

|-------------|-----------------------------|------------------------------------|

| 0           | 0                           | AD Frame: sequence-controlled data |

| 0           | 1                           | Illegal combination                |

| 1           | 0                           | BD Frame: expedited data           |

| 1           | 1                           | BC Frame: FARM-1 Control Command   |

Table 4-1 Interpretation of Bypass and Control Command flags

#### 4.9.3.2.2 Frame Data Field Structures

The Frame Data field of an AD or a BD Frame contains a TC Segment, further described in section 4.9.3.3.

The Frame Data field of a BC Frame contains a Frame Acceptance and Reporting Mechanism (FARM-1) Control Command. Two such commands are supported:

- "Unlock", further described in section 4.9.3.3.1.

- "Set V(R) to V\*(R)", further described in section 4.9.3.3.2.

b) be copied or reproduced in whole or in part without the prior written consent of Saab Ericsson Space AB;

Dokument ID Document ID Frisläppt datum Date Released Utgåva Issue Informationsklass Classification Sida Page P-ASIC-NOT-00122-SE 2006-03-22 11 Company Restricted 17

#### 4.9.3.3 Telecommand Segment Structure

The structure of the Telecommand Segment processed by the PDEC3 is shown in Figure 4-5.

|          | Telecommand Segment |              |                           |         |                        |         |  |  |  |  |  |

|----------|---------------------|--------------|---------------------------|---------|------------------------|---------|--|--|--|--|--|

|          | Segment H           | leader       | Segment Data field        | Authent | Authentication Tail (o |         |  |  |  |  |  |

| Sequence | MAI                 | □ Identifier | containing a CPDU packet, | Log     | Logical                |         |  |  |  |  |  |

| flags    |                     |              | an Authentication Unit    | Authen  | Authentication         |         |  |  |  |  |  |

|          |                     |              | Control Command, or data  | Channe  | Channel (LAC)          |         |  |  |  |  |  |

|          | Control MAP Address |              | to be provided to the     | LAC Id  | LAC                    |         |  |  |  |  |  |

|          | flag                |              | spacecraft users          |         | Count                  |         |  |  |  |  |  |

| 2 bits   | 1 bit               | 5 bits       | 0 to 1016 octets, or      | 2 bits  | 30 bits                | 40 bits |  |  |  |  |  |

| 01       | 2                   | 37           | 0 to 1007 octets          | 01      | 231                    | 3271    |  |  |  |  |  |

|          | 1 octe              | et           |                           |         | 0 or 9 octe            | s       |  |  |  |  |  |

|          | •                   |              | 1 to 1017 octets          | •       |                        |         |  |  |  |  |  |

Figure 4-5 Telecommand Segment structure

The TC Segment consists of:

- The Segment Header, used to route the TC Segment to different users, as determined by the MAP Identifier.

- The Segment Data field, further described in section 4.9.3.3.3.

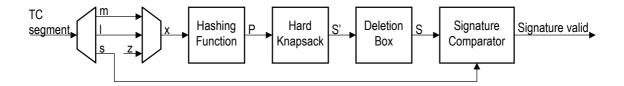

- The Authentication Tail, only included for TC Segments that shall be authenticated. It consists of a Logical Authentication Channel (LAC) with a LAC Identifier and a 30-bit LAC Count value, followed by a 40-bit Signature. The interpretation of the LAC Id field is shown in Table 4-2.

| LAC Id (binary) | Interpretation      |

|-----------------|---------------------|

| 00              | Principal LAC       |

| 01              | Auxiliary LAC       |

| 10              | Recovery LAC        |

| 11              | Illegal combination |

Table 4-2 Interpretation of LAC Id field

a) be used for any purpose other than those for which it was supplied;

b) be copied or reproduced in whole or in part without the prior written consent of Saab Ericsson Space AB;

c) be disclosed to any third party without the prior written consent of Saab Ericsson Space AB.

Sida Page Dokument ID Document ID

18 P-ASIC-NOT-00122-SE

Frisläppt datum Date Released 2006-03-22

Utgåva Issue 11 Informationsklass Classification Company Restricted

#### 4.9.3.3.1 FARM-1 Control Command "Unlock" Structure

The structure of the FARM-1 Control Command "Unlock" executed by the PDEC3 is shown in Figure 4-6. This command is used to reset the sequence-controlled service.

| "Unlock" command               |  |  |  |  |

|--------------------------------|--|--|--|--|

| Command Identifier = 0000_0000 |  |  |  |  |

| 1 octet                        |  |  |  |  |

Figure 4-6 FARM-1 Control Command "Unlock" structure

#### 4.9.3.3.2 FARM-1 Control Command "Set V(R) to V\*(R)" Structure

The structure of the FARM-1 Control Command "Set V(R) to  $V^*(R)$ " executed by the PDEC3 is shown in Figure 4-7. This command is used to preset the expected Frame Sequence Number V(R) to any desired value. The new value for V(R) is contained in the third octet of the command.

| "Set V(R) to V*(R)" command              |                           |  |  |  |  |  |  |

|------------------------------------------|---------------------------|--|--|--|--|--|--|

| Command Identifier = 1000_0010_0000_0000 | V*(R): new value for V(R) |  |  |  |  |  |  |

| 2 octets                                 | 1 octet                   |  |  |  |  |  |  |

Figure 4-7 FARM-1 Control Command "Set V(R) to V\*(R)" structure

#### 4.9.3.3.3 Segment Data Field Structures

The Segment Data Field contains either:

- A packet to be processed by the Command Pulse Distribution Unit (CPDU), further described in section 4.9.4.1.1.

- A Control Command for the Authentication Unit (AU), further described in section 4.9.3.3.4.

- Data to be provided to the spacecraft users (preceded by the Segment Header, but without Authentication Tail, if any).

Dokument ID Document ID Frisläppt datum Date Released Utgåva Issue Informationsklass Classification Sida Page P-ASIC-NOT-00122-SE 2006-03-22 11 Company Restricted 19

#### 4.9.3.3.4 Authentication Unit Control Command Structure

For an AU Control Command the Segment Header shall be 255, i.e. the MAP Identifier shall be 63 and the Sequence flags shall be 11<sub>2</sub> (unsegmented).

There are seven different AU Control Commands, defined in Table 4-3, grouped into three groups, of which the structures are shown in Figure 4-8, Figure 4-9 and Figure 4-10.

| Group   | <b>Command Identifier</b> | Command name                         |

|---------|---------------------------|--------------------------------------|

| Group 1 | 0000_00002                | Dummy segment                        |

|         | 0000_01012                | Select fixed key                     |

|         | 0000_01102                | Select programmable key              |

|         | 0000_01112                | Load fixed key into programmable key |

| Group 2 | 0000_10012                | Set New LAC Count value              |

| Group 3 | 0000_10102                | Change programmable key block A      |

|         | 0000_10112                | Change programmable key block B      |

**Table 4-3 AU Control Commands**

| Authentication Unit group 1 Control Command |  |  |  |  |

|---------------------------------------------|--|--|--|--|

| Command Identifier                          |  |  |  |  |

| 1 octet                                     |  |  |  |  |

Figure 4-8 Authentication Unit group 1 Control Command structure

| Authentication Unit group 2 Control Command |          |         |  |  |  |  |  |  |

|---------------------------------------------|----------|---------|--|--|--|--|--|--|

| Command Identifier LAC value to be set      |          |         |  |  |  |  |  |  |

| LAC Id LAC Count                            |          |         |  |  |  |  |  |  |

| 8 bits                                      | 2 bits   | 30 bits |  |  |  |  |  |  |

| 07                                          | 01 230   |         |  |  |  |  |  |  |

| 1 octet                                     | 4 octets |         |  |  |  |  |  |  |

Figure 4-9 Authentication Unit group 2 Control Command structure

| Authentication Unit group 3 Control Command           |         |          |  |  |  |  |  |

|-------------------------------------------------------|---------|----------|--|--|--|--|--|

| Command Identifier Start Address Key specific pattern |         |          |  |  |  |  |  |

| 1 octet                                               | 1 octet | 7 octets |  |  |  |  |  |

Figure 4-10 Authentication Unit group 3 Control Command structure

a) be used for any purpose other than those for which it was supplied;

b) be copied or reproduced in whole or in part without the prior written consent of Saab Ericsson Space AB;

c) be disclosed to any third party without the prior written consent of Saab Ericsson Space AB.

Sida Page Dokument ID Document ID

20 P-ASIC-NOT-00122-SE

Frisläppt datum Date Released 2006-03-22

Utgåva Issue 11 Informationsklass Classification Company Restricted

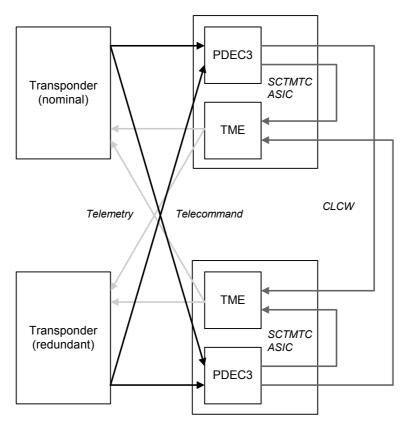

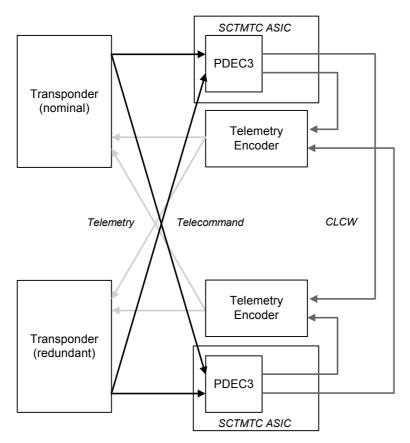

#### 4.9.3.4 Command Link Control Word Structure

The structure of the Command Link Control Word (CLCW) generated by the PDEC3 is shown in Figure 4-11.

|                               | Command Link Control Word |          |              |               |    |                 |        |                |  |        |

|-------------------------------|---------------------------|----------|--------------|---------------|----|-----------------|--------|----------------|--|--------|

| Control CLCW Version          |                           |          | Status Field | COP In Effect |    | Virtual Channel |        | Reserved Field |  |        |

| Word Type                     | Word Type Number          |          |              |               |    | Identifier      |        |                |  |        |

| 1 bit                         | 1 bit 2 bits              |          | 3 bits       | 2 bits        |    | 6 bits          |        | 2 bits         |  |        |

| 0                             | 0 12 35                   |          | 35           | 67            |    | 813             |        | 1415           |  |        |

|                               | 2 octets                  |          |              |               |    |                 |        |                |  |        |

| No RF                         | No Bit                    | Lock Out | Wait         | Retransm      | F/ | ARM B           | Report | Report Value   |  |        |

| Availabl                      | Lock                      |          |              | it            | (  | Count           | Type   |                |  |        |

| е                             |                           |          |              |               |    |                 |        |                |  |        |

| 1 bit 1 bit 1 bit 1 bit 1 bit |                           |          |              |               |    | 2 bits          |        | 2 bits 1 bit   |  | 8 bits |

| 16                            | 16 17 18 19 20            |          | 2            | 122           | 23 | 2431            |        |                |  |        |

|                               | •                         |          |              | 2 octets      | •  |                 | •      |                |  |        |

Figure 4-11 Command Link Control Word structure

The CLCW consists of:

- The Control Word Type flag, which shall be zero to identify the word as containing CLCW.

- The CLCW Version Number field, which identifies the CLCW structure. This field shall be set to 00<sub>2</sub>.

- The Status Field, reserved for future applications, which shall be set to 000<sub>2</sub>.

- The COP In Effect field, which shall be set to  $01_2$  to indicate that COP-1 is in use.

- The Virtual Channel Identifier, which identifies the TC channel of the PDEC3.

- The Reserved field, which shall be set to  $00_2$ .

- The No RF Available flag, which shall be one if none of the connected RF subsystems have detected a valid RF signal, and otherwise shall be zero.

- The No Bit Lock flag, which shall be one if none of the connected demodulation subsystems have achieved bit lock, and otherwise it shall be zero.

- Frame Acceptance and Reporting Mechanism (FARM-1) variables, being the Lockout flag, the Wait flag, the Retransmit flag, the FARM-B Count and the Report value.

- The Report Type bit, which shall be zero.

b) be copied or reproduced in whole or in part without the prior written consent of Saab Ericsson Space AB;

#### 4.9.4 Command Pulse Distribution Module (CPDM) specific

#### 4.9.4.1.1 Command Pulse Distribution Unit Packet Structure

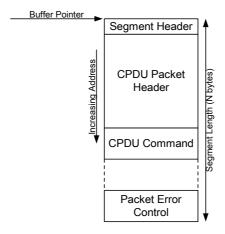

The structure of the CPDU packets is shown in Figure 4-12. CPDU packets are not processed by PDEC3 but transferred to the Command Pulse Distribution Module.

|         | CPDU Telecommand Packet           |        |         |          |          |        |            |                            |        |        |  |                       |         |

|---------|-----------------------------------|--------|---------|----------|----------|--------|------------|----------------------------|--------|--------|--|-----------------------|---------|

|         | Packet Header                     |        |         |          |          |        |            | Packet Data Field          |        |        |  |                       |         |

| Pa      | Packet Identification Packet Seq- |        |         |          |          | Packet | N (        | N Command Instructions (s) |        |        |  | ns (s)                | Packet  |

|         |                                   |        |         | uence    | Control  | Length |            |                            |        |        |  |                       | Error   |

| Version | Type                              | Data   | Appli-  |          |          |        | Com        | mand                       | Instru | iction |  | 7                     | Control |

| Number  |                                   | Field  | cation  |          | <b>-</b> |        |            | •                          | 1      |        |  | _<br>L                |         |

|         |                                   | Header | Process | flags    | Count    |        |            |                            |        |        |  | ij                    |         |

|         |                                   | flag   | ld      | e fi     |          |        | SB         | MSB                        |        | Ę.     |  | stru                  |         |

|         |                                   |        |         | enc      | nce      |        | ).<br>L    | ≥ :                        | >-     | Length |  | <u>=</u>              |         |

|         |                                   |        |         | Sequence | Sequence |        | Output No. | Output No.                 | Parity | ) e    |  | Command Instruction N |         |

|         |                                   |        |         | Se       | Se       |        | tþn        | tbul                       |        | Pulse  |  | ШL                    |         |

|         |                                   |        |         |          |          |        | 0          | Õ                          |        | ட      |  | Ŝ                     |         |

|         |                                   |        |         |          |          |        |            |                            |        |        |  |                       | 10.11   |

| 3 bits  | 1                                 | 1 bit  | 11 bits | 2 bits   | 14       | 16     | 8          | 4                          | 1      | 3      |  | 16                    | 16 bits |

| 02      | bit                               | 4      | 515     | 01       | bits     | bits   | bit        | bit                        | bit    | bit    |  | bits                  | 015     |

|         | 3                                 |        |         |          | 215      | 015    | S          | S                          |        | S      |  |                       |         |

|         | 2 octets                          |        |         | 2 octets |          | 2      | 2*N octets |                            |        |        |  | 2 octets              |         |

|         |                                   |        |         |          |          | octets |            |                            |        |        |  |                       |         |

|         |                                   |        |         |          |          |        |            |                            |        |        |  |                       |         |

Figure 4-12 Command Pulse Distribution Unit packet structure

a) be used for any purpose other than those for which it was supplied;

b) be copied or reproduced in whole or in part without the prior written consent of Saab Ericsson Space AB;

Sida *Page* 22 Dokument ID Document ID P-ASIC-NOT-00122-SE

Frisläppt datum Date Released 2006-03-22

Utgåva *Issue* 11 Informationsklass *Classification*Company Restricted

#### The CPDU packet consists of:

- The Packet Identification field, being the Version Number field, the Type field, the Data Field Header flag, and the Application Process Identifier field, which are simply compared to static values stored in the external non-volatile memory.

- The Sequence flags, which for a CPDU packet shall be 11<sub>2</sub> (standalone packet).

- The Sequence Count, which identifies the CPDU packet in a sequence of CPDU packets.

- The Packet Length field specifies the length of the CPDU packet, with its value being (total number of octets in the CPDU packet − 7).

- Between 1 and 504 CPDU command instruction when the TC Segment for the CPDU is not authenticated, and between 1 and 499 commands when it is authenticated. Each CPDU command instruction consists of:

- ♦ Output Number (12 bits), specifying one of 4096 possible CPDU outputs.

- ◆ Pulse Length (3 bits), which determines the length of the CPDU pulse. The pulse length is defined as D·2<sup>L</sup>, where D is the CPDM duration and L is the 3-bit pulse length.

- ♦ One optional parity bit. If command instruction parity is enabled in the CPDM, the total number of ones in the command instruction shall equal an odd number (odd parity).

The Packet Error Control field, which is a CRC used for detecting any remaining errors which may exist in the CPDU packet. After initialising the encoder to all ones, it is generated over the entire CPDU Packet (except the Packet Error Control field) using the polynomial  $g(x) = x^{16} + x^{12} + x^5 + 1$

4.9.7

#### Packet Telemetry Encoder (TME) specific

#### 4.9.7.1 **Telemetry Transfer Frame**

The Transfer Frame generated by the Telemetry Encoder is shown in Figure 4-13. It consists of the Primary header, the data field and the optional Secondary header and Transfer Frame trailer.

|                                          | Telemetry Transfer Frame     |                             |                        |  |  |  |  |  |  |

|------------------------------------------|------------------------------|-----------------------------|------------------------|--|--|--|--|--|--|

| Transfer F                               | rame Header                  | Transfer Frame Data Field   | Transfer Frame Trailer |  |  |  |  |  |  |

| Primary                                  | Secondary                    | ket   Packet   Packet   Pac |                        |  |  |  |  |  |  |

| Header                                   | Header                       |                             |                        |  |  |  |  |  |  |

| 6 octets                                 | 6 octets 0/4 octets variable |                             |                        |  |  |  |  |  |  |

| 223/446/892/1115/239/478/956/1195 octets |                              |                             |                        |  |  |  |  |  |  |

Figure 4-13 Channel Access Data Unit structure

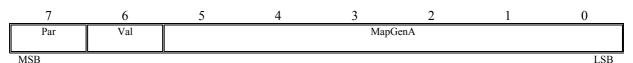

#### 4.9.7.1.1 Telemetry Primary Header Structure

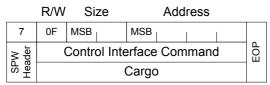

The structure of the primary header generated by the Telemetry Encoder is shown in Figure 4-14.