SpaceWire Remote Terminal Controller AT7913E User's Manual

## **Features**

- SPARC V8 integer unit with 7-stage pipeline,

4 kbyte instruction and 4 kbyte data cache

- Double precision IEEE-754 floating point unit

- EDAC protected interface to multiple 8/32bits PROM/SRAM memory banks and I/O

- Advanced on-chip debug support unit

- UARTs, Timers, Watchdog, GPIO, Digital ADC/DAC interfaces, Interrupt controller

- Two SpaceWire links with RMAP

- Redundant CAN 2.0 interface with DMA

- FIFO interface with DMA

- Up to 50 MHz system frequency

- Up to 200 Mbit/s SpaceWire data rate

- 349-pin MCGA with 50 mil pin spacing

# Description

The SpaceWire Remote Terminal Controller (RTC) is a bridge between the SpaceWire network and the CAN bus, providing a fully integrated system. Additional features are provided to carter for autonomy of remote terminals and to relieve the central processing chain of repetitive standard acquisitions and management duties.

## Aeroflex Gaisler AB

Kungsgatan 12 tel +46 31 7758650 411 19 Göteborg fax +46 31 421407 Sweden www.Aeroflex.com/Gaisler

Company confidential material and document. This document may not be distributed under any circumstances. All information is provided as is. There is no warranty that it is correct or suitable for any purpose, neither implicit nor explicit.

# **Table of contents**

| 1 | INT]                | RODUCTION                                       | 4  |  |  |  |  |  |

|---|---------------------|-------------------------------------------------|----|--|--|--|--|--|

|   | 1.1                 | Scope                                           | 4  |  |  |  |  |  |

|   | 1.2                 | Licensing                                       | 4  |  |  |  |  |  |

|   | 1.3                 | Reference documents                             | 4  |  |  |  |  |  |

|   | 1.4                 | Source reference                                | 4  |  |  |  |  |  |

|   | 1.5                 | System overview                                 | 4  |  |  |  |  |  |

|   | 1.6                 | Block diagram                                   | 5  |  |  |  |  |  |

|   | 1.7                 | Description of typical systems using the device | 6  |  |  |  |  |  |

| 2 | FUNCTIONAL OVERVIEW |                                                 |    |  |  |  |  |  |

|   | 2.1                 | General functionality                           | 7  |  |  |  |  |  |

|   | 2.2                 | General interfaces                              | 8  |  |  |  |  |  |

| 3 | PRO                 | CESSOR AND PERIPHERALS                          | 9  |  |  |  |  |  |

|   | 3.1                 | LEON integer unit                               | 9  |  |  |  |  |  |

|   | 3.2                 | Cache sub-system                                | 13 |  |  |  |  |  |

|   | 3.3                 | On-chip peripherals                             | 17 |  |  |  |  |  |

|   | 3.4                 | External memory access                          | 33 |  |  |  |  |  |

|   | 3.5                 | Hardware debug support                          | 40 |  |  |  |  |  |

|   | 3.6                 | Vendor and device id                            | 48 |  |  |  |  |  |

| 4 | ON-                 | CHIP MEMORY                                     | 49 |  |  |  |  |  |

|   | 4.1                 | Overview                                        | 49 |  |  |  |  |  |

|   | 4.2                 | Operation                                       | 49 |  |  |  |  |  |

|   | 4.3                 | Vendor and device id                            | 50 |  |  |  |  |  |

|   | 4.4                 | Registers                                       | 50 |  |  |  |  |  |

| 5 | FIFO                | O INTERFACE                                     | 52 |  |  |  |  |  |

|   | 5.1                 | Overview                                        | 52 |  |  |  |  |  |

|   | 5.2                 | Interface                                       | 54 |  |  |  |  |  |

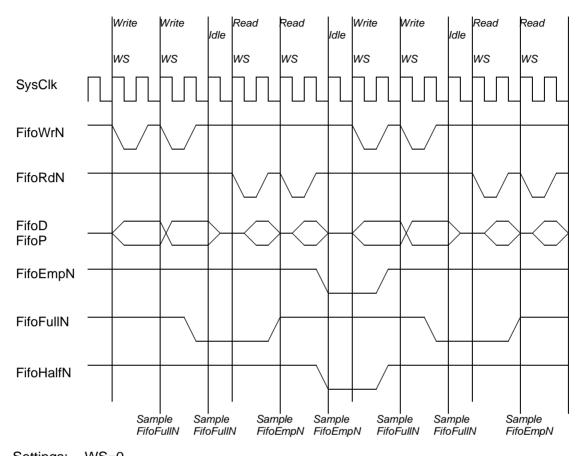

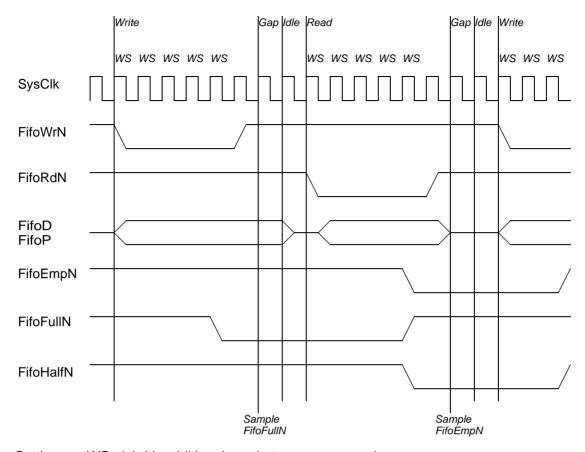

|   | 5.3                 | Waveforms                                       | 55 |  |  |  |  |  |

|   | 5.4                 | Transmission                                    | 57 |  |  |  |  |  |

|   | 5.5                 | Reception                                       | 59 |  |  |  |  |  |

|   | 5.6                 | Operation                                       | 61 |  |  |  |  |  |

|   | 5.7                 | Registers                                       | 62 |  |  |  |  |  |

| 6 | ADO                 | C / DAC INTERFACE                               | 70 |  |  |  |  |  |

|   | 6.1                 | Overview                                        | 70 |  |  |  |  |  |

|   | 6.2                 | Operation                                       | 71 |  |  |  |  |  |

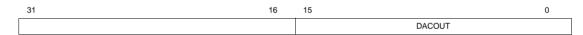

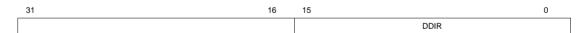

|   | 6.3                 | Registers                                       | 74 |  |  |  |  |  |

| 7 | 32-E                | BIT TIMERS                                      | 80 |  |  |  |  |  |

|   | 7.1                 | Overview                                        | 80 |  |  |  |  |  |

|   | 7.2                 | Operation                                       | 80 |  |  |  |  |  |

|   | 7.3                 | Vendor and device id                            | 80 |  |  |  |  |  |

|   | 7.4                 | Registers                                       | 81 |  |  |  |  |  |

| 8 | 24-E                | BIT GENERAL PURPOSE INPUT OUTPUT                | 84 |  |  |  |  |  |

|   | 8.1                 | Overview                                        | 84 |  |  |  |  |  |

|   | 8.2                 | Registers                                       |    |  |  |  |  |  |

|   |                     | <del>-</del>                                    |    |  |  |  |  |  |

Aerospace Defence Technology

| CAN INTERFACE               | 88 |

|-----------------------------|----|

| 9.1 Overview                | 88 |

| 9.2 Interface               | 89 |

| 9.3 Protocol                | 89 |

| 9.4 Status and monitoring   | 90 |

| 9.5 Transmission            | 90 |

| 9.6 Reception               | 93 |

| 9.7 Global reset and enable | 95 |

|    | 9.3  | Protocol                                    | 89  |

|----|------|---------------------------------------------|-----|

|    | 9.4  | Status and monitoring                       | 90  |

|    | 9.5  | Transmission                                | 90  |

|    | 9.6  | Reception                                   | 93  |

|    | 9.7  | Global reset and enable                     | 95  |

|    | 9.8  | Interrupt                                   | 95  |

|    | 9.9  | Vendor and device id                        | 95  |

|    | 9.10 | Registers                                   | 96  |

|    | 9.11 | Memory mapping                              | 107 |

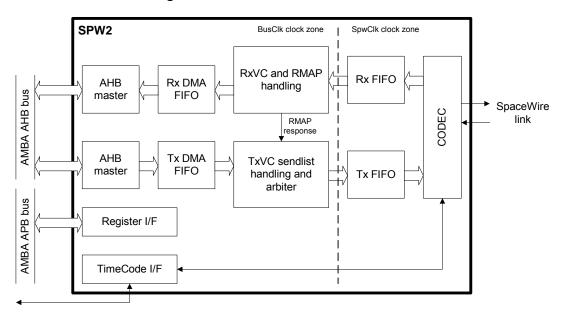

| 10 | SPAC | CEWIRE LINK INTERFACE                       | 108 |

|    | 10.1 | System overview                             | 108 |

|    | 10.2 | Functions                                   | 108 |

|    | 10.3 | Interfaces                                  | 108 |

|    | 10.4 | Module overview                             | 109 |

|    | 10.5 | Definitions                                 | 113 |

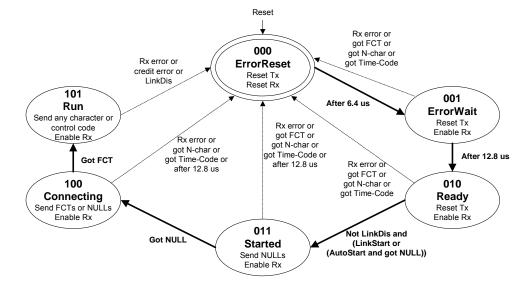

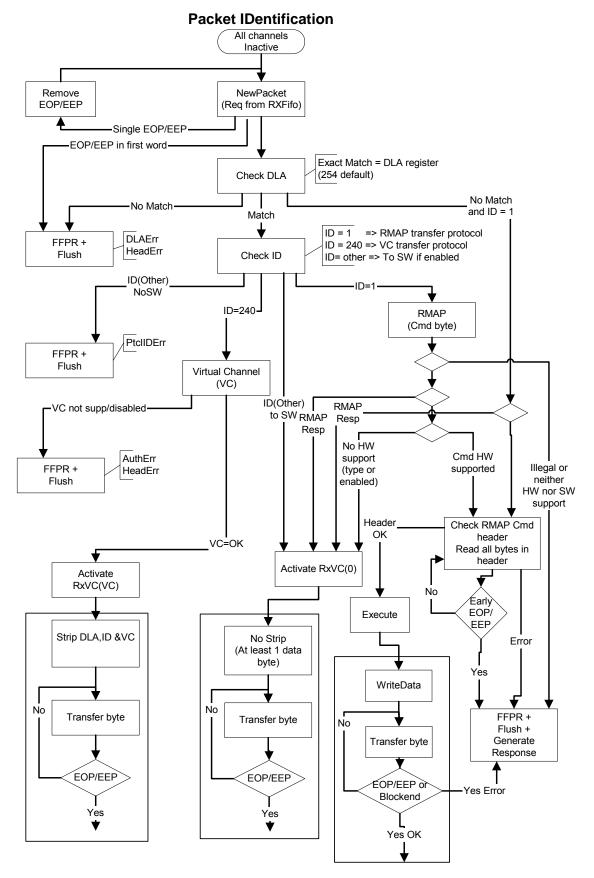

|    | 10.6 | Functional behaviour                        | 126 |

|    | 10.7 | Register definition summary                 | 161 |

|    | 10.8 | Vendor and device id                        | 181 |

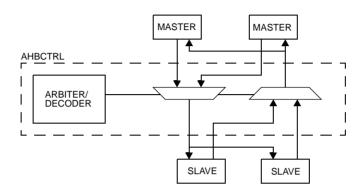

| 11 | AMB  | A AHB CONTROLLER                            | 182 |

|    | 11.1 | Overview                                    | 182 |

|    | 11.2 | Operation                                   | 182 |

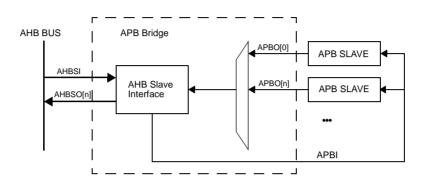

| 12 | AMB  | A AHB/APB BRIDGE                            | 184 |

|    | 12.1 | Overview                                    | 184 |

|    | 12.2 | Operation                                   | 184 |

|    | 12.3 | Vendor and device id                        | 184 |

| 13 | MEM  | IORY AND REGISTER MAP, INTERRUPT ASSIGNMENT | 185 |

|    | 13.1 | Addressing information                      | 185 |

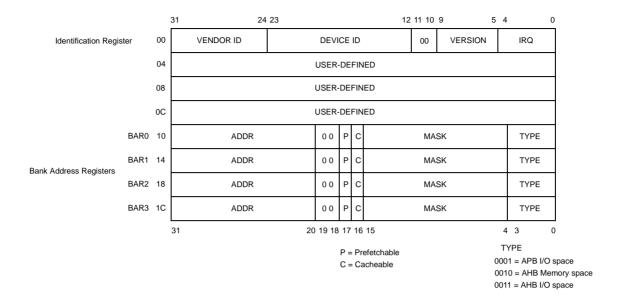

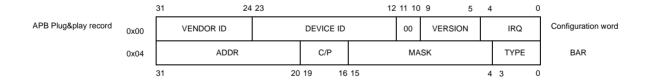

|    | 13.2 | Plug & Play information                     | 186 |

|    | 13.3 | Registers                                   | 187 |

|    | 13.4 | Interrupts                                  | 193 |

| 14 | INTE | RFACES AND SIGNALS                          | 195 |

| 15 | REV  | ISION CONTROL                               | 198 |

## 1 INTRODUCTION

## 1.1 Scope

This document establishes the User's Manual for the SpaceWire Remote Terminal Controller (RTC) device developed in the scope of the "TopNet SpaceWire Controller / Remote User Interface" activity initiated by the European Space Agency.

## 1.2 Licensing

Note that the CAN protocol is developed by Robert Bosch GmbH and protected by patents. For licensing issues please contact:

Dr. Gerhard Holfelder Corporate Licensing Department Robert Bosch GmbH - AE/EIS Tübinger Str. 123 72762 Reutlingen Germany

Phone+49-711-811-33150, Fax+49-711-811-33182, EmailGerhard.Holfelder@de.bosch.com

## 1.3 Reference documents

| [AMBA]      | AMBA <sup>TM</sup> Specification, Rev 2.0, ARM IHI 0011A, 13 May 1999, Issue A, first release, ARM Limited                                                                               |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [GRLIB]     | GRLIB IP Library User's Manual, Version 1.0.7, Gaisler Research                                                                                                                          |

| [SPARC]     | The SPARC Architecture Manual, Version 8, Revision SAV080SI9308, SPARC International Inc.                                                                                                |

| [SPWSTD]    | SpaceWire - Links, Nodes Routers and Networks, ECSS-E-ST-50-12C                                                                                                                          |

| [CANSTD]    | CAN Specification Version 2.0 Part B, BOSCH                                                                                                                                              |

| [ISO11898]  | ISO 11898:1993 and Amendment 1 (ISO 11898:1995) Road Vehicles - Interchange of Digital Information - Controller Area Network (CAN) for high-speed communication, First Edition 1993, ISO |

| [ISO11898E] | ISO 11898:1993(E) and Amendment 1, 1995, ISO                                                                                                                                             |

### 1.4 Source reference

The Space Wire Remote Terminal Controller (RTC) design is based on the following sources:

[LEON2FT-SRC] LEON-2 FT VHDL model, version 1.0.9.16.1-r85, 2007 [GRLIB-SRC] GRLIB VHDL source code, version 1.0.7, 2006

[CANESA-SRC] HURRICANE source code, version 5.1.6, dated 21 Nov 2006

[DUNDEE-SRC] SPWB source code, version 2.0

## 1.5 System overview

The SpaceWire Remote Terminal Controller (RTC) device is a bridge between the SpaceWire network (backbone) and the CAN bus, providing a fully integrated system. Additional features are provided to carter for autonomy of remote terminals and to relieve the central processing chain of repetitive standard acquisitions and management duties. The SpaceWire-RTC device can be used both in non-intelligent nodes and in nodes with local intelligence.

The SpaceWire-RTC device includes an embedded microprocessor, a CAN bus controller, ADC/DAC interfaces for analogue acquisition/conversion, standard interfaces and resources (UARTs, timers, general purpose input output).

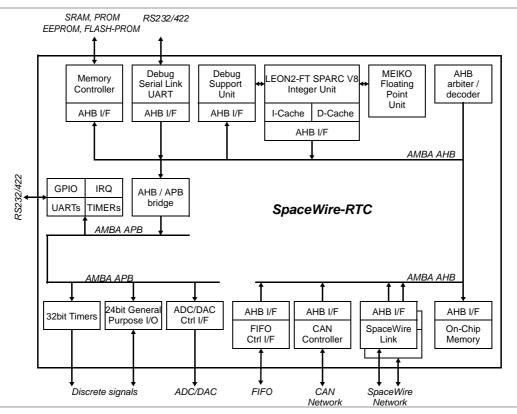

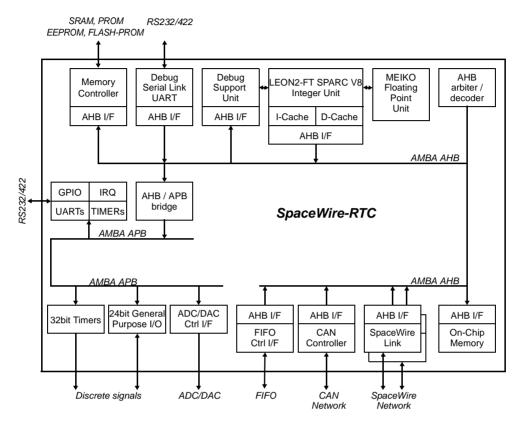

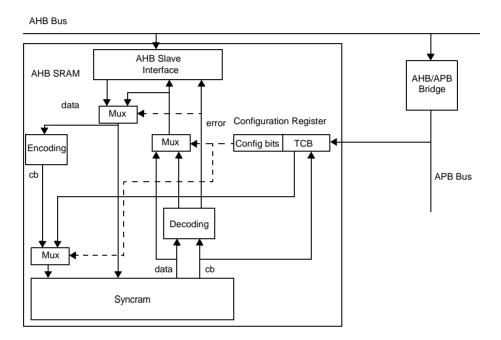

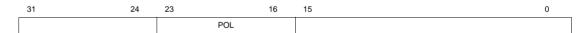

## 1.6 Block diagram

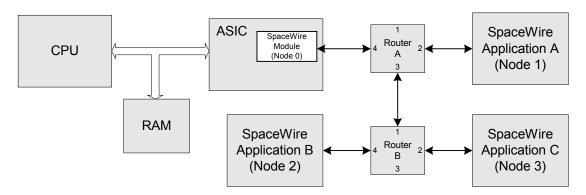

SpaceWire Remote Terminal Controller (RTC) block diagram is shown hereafter.

Figure 1. SpaceWire Remote Terminal Controller (RTC) block diagram

The block diagram shows the functional modules that constitute the SpaceWire-RTC. The SpaceWire-RTC is based on the following on-chip buses:

- AMBA AHB bus

- · AMBA APB bus

The on-chip bus selection is based on the ESA baseline/directive for using the open standard AMBA Specification (Rev 2.0) as a standard bus. See [AMBA] for details.

Although not directly shown in the block diagram, several of the modules on the AMBA AHB bus also have secondary AMBA APB interfaces for configuration and control purposes. These AMBA APB interfaces are logically connected to the AMBA APB bus shown in the block diagram. For the modules that are shown in the block diagram as only connected to the AMBA APB bus, there are no other hidden connections to the AMBA AHB bus.

The AMBA AHB bus is controlled by an AHB controller with plug&play support. The controller implements the AMBA AHB bus with the following sideband information:

- · cacheability information

- interrupt bus

- · configuration information

- · diagnostic information

The AMBA APB bus is controlled by an AHB/APB bridge with plug&play support. The bridge implements the AMBA APB bus with the following sideband information:

- interrupt bus

- · configuration information

- · diagnostic information

## 1.7 Description of typical systems using the device

The SpaceWire Remote Terminal Controller (RTC) device can be integrated in the instrument controller Unit (ICU) that acts as the payload data processor and mainly receives payload data from instruments and produces processed data to be down linked. The main data communication is performed via the SpaceWire network. The ICU is however controlled and monitored via the CAN network from the On-Board Computer (OBC). The CAN controller in the SpaceWire-RTC device acts as a remote terminal that is being managed by the OBC.

Alternatively, the SpaceWire-RTC device can be integrated in the On-Board Computer (OBC). Since the OBC acts as the network manager on the CAN network, the CAN controller carters capability such as node management and time distribution. The OBC also communicates or manages the SpaceWire network via SpaceWire links.

As can be seen from the above application scenarios, the capabilities of the SpaceWire-RTC device are not limited only to support the CAN bus in the ICU, but also allows it to be used in an OBC. This reduces future development costs since the same device is used in both payload and avionics. This also promotes the usage of hybrid SpaceWire and CAN networks and the TopNet concept.

To bring the concept a step further, one could envisage applications in which the SpaceWire-RTC device actually replaces the processor in an ICU. The integer processing capacity of the LEON2 processor in the SpaceWire-RTC device is in par with what can be expected from current monolithic processor devices. This provides for savings in terms of power and board area, since a single device with external memory is sufficient to form the core of an ICU.

The main application of the SpaceWire-RTC device is however in instruments or individual experiments of the payload. It provides an abundance of interfaces, each with a high degree of programmability and configurability. It is able to acquire analogue and digital data, generated by connected peripherals and to generate discrete commands towards the same peripherals.

The SpaceWire-RTC device can be operated stand-alone or with a number of external devices such as SRAM, PROM and FIFO memories, ADC and DAC converters. The device can be managed locally by the on-chip processor, or remotely via its SpaceWire link interfaces.

SpaceWire-RTC device can operate as a single-chip system, with software being uploaded to its onchip memory via the SpaceWire link interface, forming a compact solution for remotely controlled applications. Or it can operate in a full-size system, with software being decompressed from local PROM and executed from multiple fast and wide SRAM memory banks.

## 2 FUNCTIONAL OVERVIEW

## 2.1 General functionality

The SpaceWire-RTC ASIC implements the following functions:

- Processor

- The SpaceWire-RTC ASIC includes the LEON2-FT SPARC V8 Integer Unit, featuring an instruction cache of 4 kbytes, and a data cache of 4 kbytes, and a Meiko Floating Point Unit.

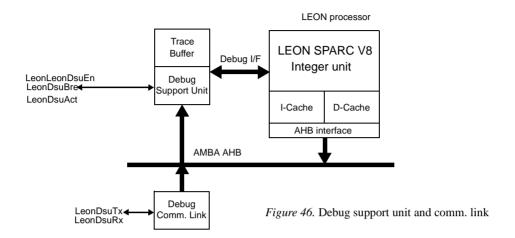

- Debug Support Unit

- The SpaceWire-RTC ASIC includes the LEON2-FT Debug Support Unit (DSU) with a Trace Buffer of 512 lines of 16 bytes.

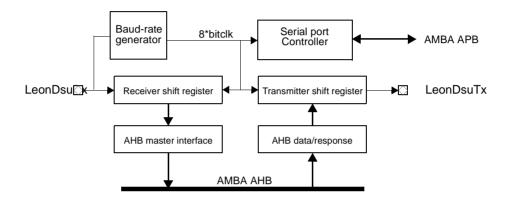

- Debug Serial Link UART

- The SpaceWire-RTC ASIC includes the LEON2-FT serial debug interface for AMBA AHB.

- The SpaceWire-RTC ASIC includes the LEON2-FT peripherals:

- Interrupt Controller and Secondary Interrupt Controller

- 32-bit Timers (three)

- UART Serial Links (two)

- 16-bit General Purpose Input Output

- Memory Interface

- The SpaceWire-RTC ASIC includes the LEON2-FT Memory Controller, including EDAC protection and support for SRAM, PROM, EEPROM, and a memory mapped I/O area.

- On-Chip Memory

- The SpaceWire-RTC ASIC includes 64 kbytes EDAC protected on-chip memory.

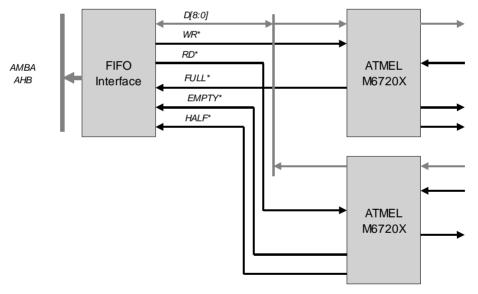

- FIFO Interface

- The SpaceWire-RTC ASIC can simultaneously interface two FIFO devices, one for input and one for output. The interface features one DMA channel in either direction.

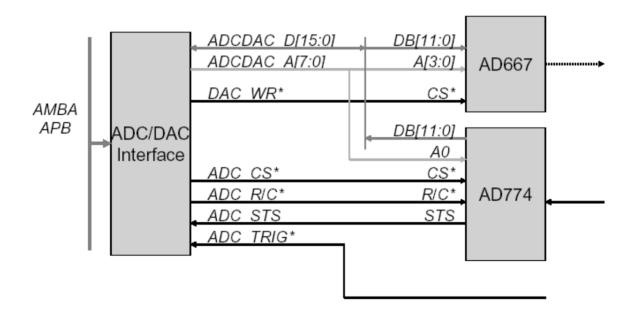

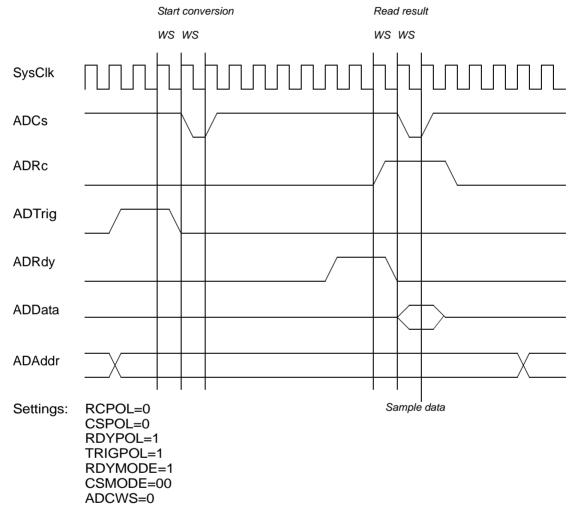

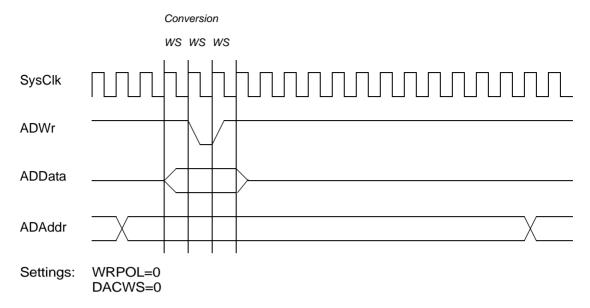

- ADC/DAC Interface

- The SpaceWire-RTC ASIC can simultaneously interface ADC and DAC devices.

- 32-bit Timers

- The SpaceWire-RTC ASIC includes two additional 32-bit timers, being cascadable and with optional external clock input.

- 24-bit General Purpose Input Output

- The SpaceWire-RTC ASIC includes 24 additional general-purpose input output channels, supporting input, output and pulse generation.

- CAN Interface

- The SpaceWire-RTC ASIC includes the ESA HurriCANe CAN controller. The interface features one DMA channel in either direction and is compatible with the CANopen application layer protocol.

- SpaceWire Link Interface

- The SpaceWire-RTC ASIC includes two University of Dundee SpaceWire links. The interface implements DMA channels and Remote Memory Access Protocol (RMAP).

- JTAG Interface

- The SpaceWire-RTC ASIC includes a JTAG interface with TAP controller for boundary scan testing.

#### 2.2 General interfaces

The SpaceWire-RTC ASIC provides the following external and internal interfaces:

- Debug Serial Link UART

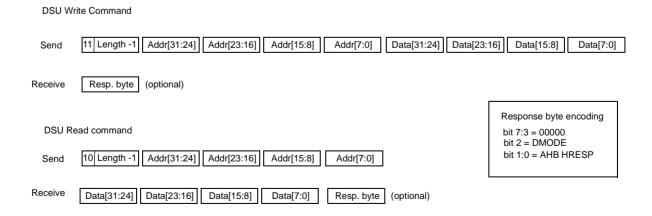

- A simple communication protocol is provided to transmit access parameters and data on the internal AMBA bus. A command comprises a control byte, followed by and a 32-bit address, followed by optional write data.

- Interrupt Controller

- External interrupts can be selected from the 16-bit General Purpose Input Output or the data bus of the Memory Interface.

- 32-bit Timers

- Watchdog with external trigger signal.

- UART Serial Links

- Two Universal Asynchronous Receiver and Transmitters (UART), supporting optional parity, internal or external clock source, hardware handshake and programmable baud rate.

- 16-bit General Purpose Input Output

- Programmable input output channels, shared with the interrupt controller inputs and the UART serial links.

- · Memory Interface

- Supports two PROM banks, four SRAM banks and one memory mapped I/O. Features 23 byte-address bits, 32 data bits and 8 check bits. Unused data bits can be used as general purpose input output.

- · FIFO Interface

- Supports one input and one output external FIFO device, with 8- or 16-bit wide data. Unused data bits can be used as general purpose input output.

- ADC/DAC Interface

- Supports one ADC and one DAC device, with 8- or 16-bit wide data, and 8-bit address. Unused address and data bits can be used as general purpose input output.

- 32-bit Timers

- Supports external clock source and external triggers.

- 24-bit General Purpose Input Output

- Dedicated programmable input output channels, with input interrupts.

- · CAN Interface

- Supports nominal and redundant transmit and receive pair, with non-simultaneously operation.

- SpaceWire Link Interface

- Supports nominal and redundant SpaceWire links, with simultaneously operation.

- JTAG Interface

- Supports standard TAP signal interface.

## 3 PROCESSOR AND PERIPHERALS

## 3.1 LEON integer unit

The LEON integer unit (IU) implements SPARC integer instructions as defined in SPARC Architecture Manual version 8. It is a new implementation, not based on any previous designs. The implementation is focused on portability and low complexity.

## 3.1.1 Overview

The LEON integer unit has the following features:

- 5-stage instruction pipeline

- Separate instruction and data cache interface

- Support for 8 register windows

- Multiplier 16x16

- Radix-2 divider (non-restoring)

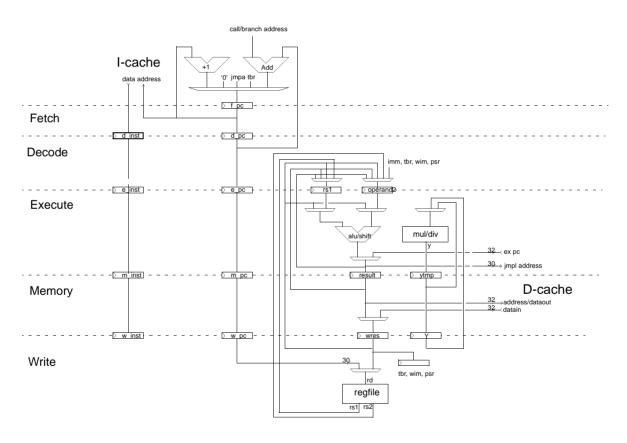

Figure 2 shows a block diagram of the integer unit.

Figure 2. LEON integer unit block diagram

## 3.1.2 Instruction pipeline

The LEON integer unit uses a single instruction issue pipeline with 5 stages:

1. FE (Instruction Fetch): If the instruction cache is enabled, the instruction is fetched from the instruction cache. Otherwise, the fetch is forwarded to the memory controller. The instruction is valid at the end of this stage and is latched inside the IU.

- 2. DE (Decode): The instruction is decoded and the operands are read. Operands may come from the register file or from internal data bypasses. CALL and Branch target addresses are generated in this stage.

- 3. EX (Execute): ALU, logical, and shift operations are performed. For memory operations (e.g., LD) and for JMPL/RETT, the address is generated.

- 4. ME (Memory): Data cache is accessed. For cache reads, the data will be valid by the end of this stage, at which point it is aligned as appropriate. Store data read out in the execution stage is written to the data cache at this time.

- 5. WR (Write): The result of any ALU, logical, shift, or cache read operations are written back to the register file.

Table 1 lists the cycles per instruction (assuming cache hit and no load interlock):

TABLE 1. Instruction timing

| Instruction            | Cycles |

|------------------------|--------|

| JMPL                   | 2      |

| Double load            | 2      |

| Single store           | 2      |

| Double store           | 3      |

| SMUL/UMUL              | 5      |

| SDIV/UDIV              | 35     |

| Taken Trap             | 4      |

| Atomic load/store      | 3      |

| All other instructions | 1      |

#### 3.1.3 Multiply instructions

The LEON processor supports the SPARC integer multiply instructions UMUL, SMUL UMULCC and SMULCC. These instructions perform a 32x32-bit integer multiply, producing a 64-bit result. SMUL and SMULCC performs signed multiply while UMUL and UMULCC performs unsigned multiply. UMULCC and SMULCC also set the condition codes to reflect the result.

### 3.1.4 Divide instructions

Full support for SPARC V8 divide instructions is provided (SDIV/UDIV/SDIVCC/UDIVCC). The divide instructions perform a 64-by-32 bit divide and produce a 32-bit result. Rounding and overflow detection is performed as defined in the SPARC V8 standard.

## 3.1.5 Register file SEU protection

To prevent erroneous operations from SEU errors in the main register file, each word is protected using a 7-bit EDAC checksum. Checking of the EDAC bits is done every time a fetched register value is used in an instruction. If a correctable error is detected, the erroneous data is corrected before being used. At the same time, the corrected register value is also written back to the register file. A correction operation incurs a delay 4 clock cycles, but has no other software visible impact. If an un-correctable error is detected, a register error trap (tt=0x20) is generated.

The implemented protection scheme has an impact on double-store instructions: the write-buffer will delay the request of the memory bus one clock cycle in order to not start any memory store cycle before the second store data word has been checked and (potentially) corrected.

The register file protection operation is controlled using application-specific register 16 (%asr16). The register is accessed using the RDASR/WRASR instructions.

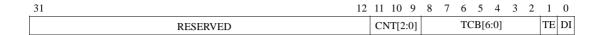

Figure 1: Register file protection control register (%asr16)

[0]: DI - disable checking. If set, will disable the register-file checking function.

[1]: TE - Test enable.

[8:2] TCB[6:0] - Test checkbits.

[11:9] CNT[2:0] - Error counter. This field will be incremented for each corrected error.

The protection can be disabled by clearing the DI bit (this bit is set to '1' after reset). By setting the TE bit, errors can be inserted in the register file to test the protection function. Since a 7-bit EDAC is used, when the test mode is enabled the register checksum is XORed with the TCB field before written to the register file. The CNT field is incremented each time a register correction is performed, but saturates at "111".

## 3.1.6 Processor reset operation

The processor is reset by asserting the RESET input for at least one clock cycle. The following table indicates the reset values of the registers which are affected by the reset. All other registers maintain their value (or are undefined).

TABLE 2. Processor reset values

| Register                        | Reset value |

|---------------------------------|-------------|

| PC (program counter)            | 0x0         |

| nPC (next program counter)      | 0x4         |

| PSR (processor status register) | ET=0, S=1   |

| CCR (cache control register)    | 0x0         |

Execution will start from address 0.

## 3.1.7 Exceptions

LEON adheres to the general SPARC trap model. The table below shows the implemented traps and their individual priority. When PSR (processor status register) bit ET=0, an exception trap causes the processor to halt execution and enter error mode, and the external error signal will then be asserted.

TABLE 3. Trap allocation and priority

| Trap                     | TT   | Pri | Description                                      |

|--------------------------|------|-----|--------------------------------------------------|

| reset                    | 0x00 | 1   | Power-on reset                                   |

| write error              | 0x2b | 2   | write buffer error                               |

| instruction_access_error | 0x01 | 3   | Error during instruction fetch                   |

| illegal_instruction      | 0x02 | 5   | UNIMP or other un-implemented instruction        |

| privileged_instruction   | 0x03 | 4   | Execution of privileged instruction in user mode |

| fp_disabled              | 0x04 | 6   | FP instruction while FPU disabled                |

| cp_disabled              | 0x24 | 6   | CP instruction while Co-processor disabled       |

TABLE 3. Trap allocation and priority

| Trap                    | TT          | Pri | Description                                   |

|-------------------------|-------------|-----|-----------------------------------------------|

| watchpoint_detected     | 0x0B        | 7   | Hardware breakpoint match                     |

| window_overflow         | 0x05        | 8   | SAVE into invalid window                      |

| window_underflow        | 0x06        | 8   | RESTORE into invalid window                   |

| register_hadrware_error | 0x20        | 9   | register file EDAC error (LEON-FT only)       |

| mem_address_not_aligne  | 0x07        | 10  | Memory access to un-aligned address           |

| fp_exception            | 0x08        | 11  | FPU exception                                 |

| cp_exception            | 0x28        | 11  | Co-processor exception                        |

| data_access_exception   | 0x09        | 13  | Access error during load or store instruction |

| tag_overflow            | 0x0A        | 14  | Tagged arithmetic overflow                    |

| divide_exception        | 0x2A        | 15  | Divide by zero                                |

| interrupt_level_1       | 0x11        | 31  | Asynchronous interrupt 1                      |

| interrupt_level_2       | 0x12        | 30  | Asynchronous interrupt 2                      |

| interrupt_level_3       | 0x13        | 29  | Asynchronous interrupt 3                      |

| interrupt_level_4       | 0x14        | 28  | Asynchronous interrupt 4                      |

| interrupt_level_5       | 0x15        | 27  | Asynchronous interrupt 5                      |

| interrupt_level_6       | 0x16        | 26  | Asynchronous interrupt 6                      |

| interrupt_level_7       | 0x17        | 25  | Asynchronous interrupt 7                      |

| interrupt_level_8       | 0x18        | 24  | Asynchronous interrupt 8                      |

| interrupt_level_9       | 0x19        | 23  | Asynchronous interrupt 9                      |

| interrupt_level_10      | 0x1A        | 22  | Asynchronous interrupt 10                     |

| interrupt_level_11      | 0x1B        | 21  | Asynchronous interrupt 11                     |

| interrupt_level_12      | 0x1C        | 20  | Asynchronous interrupt 12                     |

| interrupt_level_13      | 0x1D        | 19  | Asynchronous interrupt 13                     |

| interrupt_level_14      | 0x1E        | 18  | Asynchronous interrupt 14                     |

| interrupt_level_15      | 0x1F        | 17  | Asynchronous interrupt 15                     |

| trap_instruction        | 0x80 - 0xFF | 16  | Software trap instruction (TA)                |

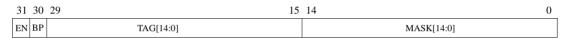

# 3.1.8 Hardware breakpoints

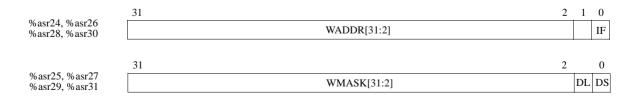

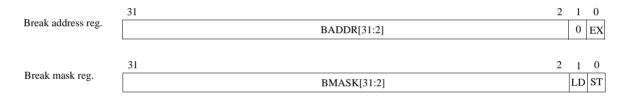

The integer unit can be configured to include up to four hardware breakpoints. Each breakpoint consists of a pair of application-specific registers (%asr24/25, %asr26/27, %asr28/30 and %asr30/31) registers; one with the break address and one with a mask:

Figure 3. Watch-point registers

Any binary aligned address range can be watched - the range is defined by the WADDR field, masked by the WMASK field (WMASK[x] = 1 enables comparison). On a breakpoint hit, trap

0x0B is generated. By setting the IF, DL and DS bits, a hit can be generated on instruction fetch, data load or data store. Clearing these three bits will effectively disable the breakpoint function.

## 3.1.9 Floating-point unit

The Meiko FPU is attached using an integrated interface inside the IU pipeline. The integrated FPU interface does not implement a floating-point queue, and the processor is stopped during the execution of floating-point instructions. This means that QNE bit in the %fsr register always is zero, and any attempts of executing the STDFQ instruction will generate a FPU exception trap.

## 3.2 Cache sub-system

#### 3.2.1 Overview

The LEON processor implements a Harvard architecture with separate instruction and data buses, connected to two independent cache controllers. In addition to the address, a SPARC processor also generates an 8-bit address space identifier (ASI), providing up to 256 separate, 32-bit address spaces. During normal operation, the LEON processor accesses instructions and data using ASI 0x8 - 0xB as defined in the SPARC standard. Using the LDA/STA instructions, alternative address spaces can be accessed. The table shows the ASI usage for LEON. Only ASI[3:0] are used for the mapping, ASI[7:4] have no influence on operation.

TABLE 4. ASI usage

| ASI                | Usage                                       |

|--------------------|---------------------------------------------|

| 0x0, 0x1, 0x2, 0x3 | Forced cache miss (replace if cacheable)    |

| 0x4, 0x7           | Forced cache miss (update on hit)           |

| 0x5                | Flush instruction cache                     |

| 0x6                | Flush data cache                            |

| 0x8, 0x9, 0xA, 0xB | Normal cached access (replace if cacheable) |

| 0xC                | Instruction cache tags                      |

| 0xD                | Instruction cache data                      |

| 0xE                | Data cache tags                             |

| 0xF                | Data cache data                             |

Access to ASI 4 and 7 will force a cache miss, and update the cache if the data was previously cached. Access with ASI 0 - 3 will force a cache miss, update the cache if the data was previously cached, or allocated a new line if the data was not in the cache and the address refers to a cacheable location.

TABLE 5. Default cache table

| Address range          | Area           | Cached        |

|------------------------|----------------|---------------|

| 0x00000000 - 0x1FFFFFF | PROM           | Cacheable     |

| 0x20000000 - 0x3FFFFFF | I/O            | Non-cacheable |

| 0x40000000 -0x7FFFFFF  | RAM            | Cacheable     |

| 0x80000000 -0x9FFFFFF  | Internal (AHB) | Non-cacheable |

| 0xA0000000 -Ax7FFFFFF  | On-Chip RAM    | Cacheable     |

| 0xB0000000 -0xFFFFFFF  | Internal (AHB) | Non-cacheable |

#### 3.2.2 Instruction cache

## 3.2.2.1 Operation

The instruction cache is configured as a direct-mapped cache. The set size is 4 kbyte and divided into cache lines of 32 bytes. Each line has a cache tag associated with it consisting of a tag field, valid field with one valid bit for each 4-byte sub-block. On an instruction cache miss to a cachable location, the instruction is fetched and the corresponding tag and data line updated.

If instruction burst fetch is enabled in the cache control register (CCR) the cache line is filled from main memory starting at the missed address and until the end of the line. At the same time, the instructions are forwarded to the IU (streaming). If the IU cannot accept the streamed instructions due to internal dependencies or multi-cycle instruction, the IU is halted until the line fill is completed. If the IU executes a control transfer instruction (branch/CALL/JMPL/RETT/TRAP) during the line fill, the line fill will be terminated on the next fetch. If instruction burst fetch is enabled, instruction streaming is enabled even when the cache is disabled. In this case, the fetched instructions are only forwarded to the IU and the cache is not updated.

If a memory access error occurs during a line fill with the IU halted, the corresponding valid bit in the cache tag will not be set. If the IU later fetches an instruction from the failed address, a cache miss will occur, triggering a new access to the failed address. If the error remains, an instruction access error trap (tt=0x1) will be generated.

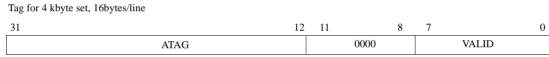

### 3.2.2.2 Instruction cache tag

A instruction cache tag entry consists of several fields as shown in figure 4:

Figure 4. Instruction cache tag layout

#### Field Definitions:

[31:12]: Address Tag (ATAG) - Contains the tag address of the cache line.

[11:8]: Unused. No affect when written to. Undefined when read.

[7:0]: Valid (V) - When set, the corresponding sub-block of the cache line contains valid data. These bits are set when a sub-block is filled due to a successful cache miss; a cache fill which results in a memory error will leave the valid bit unset. A FLUSH instruction will clear all valid bits. V[0] corresponds to address 0 in the cache line, V[1] to address 1, V[2] to address 2 and so on.

## 3.2.3 Data cache

### **3.2.3.1 Operation**

The data cache is configured as a direct-mapped cache. The set size is 4 kbyte and divided into cache lines of 16 bytes. Each line has a cache tag associated with it consisting of a tag field, valid field with one valid bit for each 4-byte sub-block. On a data cache read-miss to a cachable location 4 bytes of data are loaded into the cache from main memory. The write policy for stores is write-through with no-allocate on write-miss. In a multi-set configuration a line to be replaced on read-miss is chosen according to the replacement policy. If a memory access error occurs during a data load, the corresponding valid bit in the cache tag will not be set. and a data access error trap (tt=0x9) will be generated.

### 3.2.3.2 Write buffer

The write buffer (WRB) consists of three 32-bit registers used to temporarily hold store data until it is sent to the destination device. For half-word or byte stores, the stored data replicated into proper byte alignment for writing to a word-addressed device, before being loaded into one of the WRB registers. The WRB is emptied prior to a load-miss cache-fill sequence to avoid any stale data from being read in to the data cache.

Since the processor executes in parallel with the write buffer, a write error will not cause an exception to the store instruction. Depending on memory and cache activity, the write cycle may not occur until several clock cycles after the store instructions has completed. If a write error occurs, the currently executing instruction will take trap 0x2b.

Note: the 0x2b trap handler should flush the data cache, since a write hit would update the cache while the memory would keep the old value due the write error.

## 3.2.3.3 Data cache snooping

The data cache can optionally perform snooping on the AHB bus. When snooping is enabled, the data cache controller will monitor write accesses to the AHB bus performed by other AHB masters (DMA). When a write access is performed to a cacheable memory location, the corresponding cacheline will be invalidated in the data cache if present. Cache snooping has no overhead and does not affect performance. It can be dynamically enabled/disabled through bit 23 in the cache control register. Cache snooping requires the target technology to implement dual-port memories, which will be used to implement the cache tag RAM.

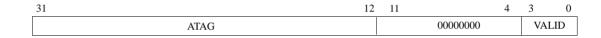

## 3.2.3.4 Data cache tag

A data cache tag entry consists of several fields as shown in figure 5:

Figure 5. Data cache tag layout

### Field Definitions:

[31:12]: Address Tag (ATAG) - Contains the address of the data held in the cache line.

[11:4]: Unused. No affect when written to. Undefined when read.

[3:0]: Valid (V) - When set, the corresponding sub-block of the cache line contains valid data. These bits is set when a sub-block is filled due to a successful cache miss; a cache fill which results in a memory error will leave the valid bit unset. V[0] corresponds to address 0 in the cache line, V[1] to address 1, V[2] to address 2 and V[3] to address 3.

## 3.2.4 Cache flushing

The instruction and data cache is flushed by executing the FLUSH instruction, setting the FI bit in the cache control register, or by writing to any location with ASI=0x5. The flushing will take one cycle per cache line and set during which the IU will not be halted, but during which the instruction cache will be disabled. When the flush operation is completed, the cache will resume the state (disabled, enabled or frozen) indicated in the cache control register.

## 3.2.5 Diagnostic cache access

Tags and data in the instruction and data cache can be accessed through ASI address space 0xC, 0xD, 0xE and 0xF by executing LDA and STA instructions. Address bits making up the cache offset will be used to index the tag to be accessed while the least significant bits of the bits making up the address tag will be used to index the cache set.

Diagnostic read of tags is possible by executing an LDA instruction with ASI=0xC for instruction cache tags and ASI=0xE for data cache tags. A cache line and set are indexed by the address bits making up the cache offset and the least significant bits of the address bits making up the address tag. Similarly, the data sub-blocks may be read by executing an LDA instruction with ASI=0xD for instruction cache data and ASI=0xF for data cache data. The sub-block to be read in the indexed cache line and set is selected by A[4:2].

The tags can be directly written by executing a STA instruction with ASI=0xC for the instruction cache tags and ASI=0xE for the data cache tags. The cache line and set are indexed

by the address bits making up the cache offset and the least significant bits of the address bits making up the address tag. D[31:10] is written into the ATAG field (see above) and the valid bits are written with the D[7:0] of the write data. Bit D[9] is written into the LRR bit (if enabled) and D[8] is written into the lock bit (if enabled). The data sub-blocks can be directly written by executing a STA instruction with ASI=0xD for the instruction cache data and ASI=0xF for the data cache data. The sub-block to be read in the indexed cache line and set is selected by A[4:2].

Note that diagnostic access to the cache is not possible during a FLUSH operation and will cause a data exception (trap=0x09) if attempted.

## 3.2.6 Cache parity protection

The caches are provided with two parity bits per tag and per 4-byte data sub-block. The tag parity is generated from the tag value and the valid bits. Similarly, the data sub-block parity is derived from the sub-block data. The parity bits are written simultaneously with the associated tag or sub-block and checked on each access. Two parity bits are configured, with the bits corresponding to the parity of odd and even data (tag) bits.

If a tag parity error is detected during a cache access, a cache miss will be generated and the tag (and data) will be automatically updated. All valid bits except the one corresponding to the newly loaded data will be cleared. If a data sub-block parity error occurs, a miss will also be generated but only the failed sub-block will be updated with data from main memory.

## 3.2.7 Cache Control Register

The operation of the instruction and data caches is controlled through a common Cache Control Register (CCR) (figure 5). Each cache can be in one of three modes: disabled, enabled and frozen. If disabled, no cache operation is performed and load and store requests are passed directly to the memory controller. If enabled, the cache operates as described above. In the frozen state, the cache is accessed and kept in sync with the main memory as if it was enabled, but no new lines are allocated on read misses.

| 31 30 29  | 28 27 26 | 25 24 23 | 22 21 | 20 19 | 18 17 1 | 6 15 | 14 13 12 | 11 10 | 9 8 | 7 6 | 5 4   | 3 2 | 1 0 |

|-----------|----------|----------|-------|-------|---------|------|----------|-------|-----|-----|-------|-----|-----|

| DREPL IRE | PL ISETS | DSETS DS | FD FI | CPC   | CPTE I  | B IP | DP ITE   | IDE   | DTE | DDE | DF IF | DCS | ICS |

Figure 6. Cache control register

- [31:30]: Data cache replacement policy (DREPL) 00 no replacement policy (direct-mapped cache), 01 random, 10 least-recently replaced (LRR), 11 least-recently used (LRU)

- [29:28]: Instruction cache replacement policy (IREPL) 00 no replacement policy (direct-mapped cache), 01 random, 10 least-recently replaced (LRR), 11 least-recently used (LRU)

- [27:26]: Instruction cache associativity (ISETS) Number of sets in the instruction cache 1:00 direct mapped, 01 2-way associative, 10 3-way associative, 11 4-way associative

- [25:24]: Data cache associativity (DSETS) Number of sets in the data cache 1: 00 direct mapped, 01 2-way associative, 10 3-way associative, 11 4-way associative

- [23]: Data cache snoop enable [DS] if set, will enable data cache snooping.

- [22]: Flush data cache (FD). If set, will flush the data cache. Always reads as zero.

- [21]: Flush Instruction cache (FI). If set, will flush the instruction cache. Always reads as zero.

- [20:19]: Cache parity bits (CPC) Indicates how many parity bits are used to protect the caches (00=none, 01=1, 10=2)

- [18:17]: Cache parity test bits. (CPTE). These bits are XOR'ed to the data and tag parity bits during diagnostic writes.

- [16]: Instruction burst fetch (IB). This bit enables burst fill during instruction fetch.

- [15]: Instruction cache flush pending (IP). This bit is set when an instruction cache flush operation is in progress.

- [14]: Data cache flush pending (DP). This bit is set when a data cache flush operation is in progress.

- [13:12]: Instruction cache tag error counter (ITE) This field is incremented every time an instruction cache tag parity error is detected.

- [11:10]: Instruction cache data error counter (IDE) This field is incremented each time an instruction cache data sub-block parity error is detected.

- [9:8]: Data cache tag error counter (DTE) This field is incremented every time a data cache tag parity error is detected.

- [7:6]: Data cache data error counter (DDE) This field is incremented each time an instruction cache data sub-block parity error is detected.

- [5]: Data Cache Freeze on Interrupt (DF) If set, the data cache will automatically be frozen when an asynchronous interrupt is taken.

- [4]: Instruction Cache Freeze on Interrupt (IF) If set, the instruction cache will automatically be frozen when an asynchronous interrupt is taken.

- [3:2]: Data Cache state (DCS) Defines the current data cache state according to the following: X0= disabled, 01 = frozen, 11 = enabled. Set to '00' at reset.

- [1:0]: Instruction Cache state (ICS) Defines the current data cache state according to the following: X0= disabled, 01 = frozen, 11 = enabled. Set to '00' at reset.

If the DF or IF bit is set, the corresponding cache will be frozen when an asynchronous interrupt is taken. This can be beneficial in real-time system to allow a more accurate calculation of worst-case execution time for a code segment. The execution of the interrupt handler will not evict any cache lines and when control is returned to the interrupted task, the cache state is identical to what it was before the interrupt.

If a cache has been frozen by an interrupt, it can only be enabled again by enabling it in the CCR. This is typically done at the end of the interrupt handler before control is returned to the interrupted task.

# 3.3 On-chip peripherals

#### 3.3.1 On-chip registers

A number of system support functions are provided directly on-chip. The functions are controlled through registers mapped APB bus according to the following table:

TABLE 6. On-chip registers

| Address    | Register                                   | Address    |                                      |

|------------|--------------------------------------------|------------|--------------------------------------|

| 0x80000000 | Memory configuration register 1            | 0x800000B0 | Secondary interrupt mask register    |

| 0x80000004 | Memory configuration register 2 0x800000B4 |            | Secondary interrupt pending register |

| 0x80000008 | Memory configuration register 3            | 0x800000B8 | Secondary interrupt status register  |

| 0x800000C  | AHB Failing address register               | 0x800000B8 | Secondary interrupt clear register   |

| 0x80000010 | AHB status register                        |            |                                      |

| 0x80000014 | Cache control register                     | 0x800000C4 | DSU UART status register             |

| 0x80000018 | Power-down register                        | 0x800000C8 | DSU UART control register            |

| 0x8000001C | Write protection register 1                | 0x800000CC | DSU UART scaler register             |

| 0x80000020 | Write protection register 2                |            |                                      |

| 0x80000024 | LEON configuration register                | 0x800000D0 | Write protect start address 1        |

| 0x80000040 | Timer 1 counter register                   | 0x800000D4 | Write protect end address 1          |

TABLE 6. On-chip registers

| Address    | Register                              | Address    |                               |

|------------|---------------------------------------|------------|-------------------------------|

| 0x80000044 | Timer 1 reload register               | 0x800000D8 | Write protect start address 2 |

| 0x80000048 | Timer 1 control register              | 0x800000DC | Write protect end address 2   |

| 0x8000004C | Watchdog register                     |            |                               |

| 0x80000050 | Timer 2 counter register              |            |                               |

| 0x80000054 | Timer 2 reload register               |            |                               |

| 0x80000058 | Timer 2 control register              |            |                               |

| 0x80000060 | Prescaler counter register            |            |                               |

| 0x80000064 | Prescaler reload register             |            |                               |

| 0x80000070 | UART 1 data register                  |            |                               |

| 0x80000074 | UART 1 status register                |            |                               |

| 0x80000078 | UART 1 control register               |            |                               |

| 0x8000007C | UART 1 scaler register                |            |                               |

| 0x80000080 | UART 2 data register                  |            |                               |

| 0x80000084 | UART 2 status register                |            |                               |

| 0x80000088 | UART 2 control register               |            |                               |

| 0x8000008C | UART 2 scaler register                |            |                               |

| 0x80000090 | Interrupt mask and priority register  |            |                               |

| 0x80000094 | Interrupt pending register            |            |                               |

| 0x80000098 | Interrupt force register              |            |                               |

| 0x8000009C | Interrupt clear register              |            |                               |

| 0x800000A0 | I/O port input/output register        |            |                               |

| 0x800000A4 | I/O port direction register           |            |                               |

| 0x800000A8 | I/O port interrupt config. register 1 |            |                               |

| 0x800000AC | I/O port interrupt config. register 2 |            |                               |

# 3.3.2 Interrupt controller

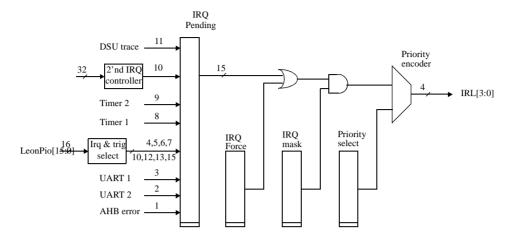

The LEON interrupt controller is used to prioritize and propagate interrupt requests from internal or external devices to the integer unit. In total 15 interrupts are handled, divided on two priority levels. Figure 7 shows a block diagram of the interrupt controller.

Figure 7. Interrupt controller block diagram

## 3.3.2.1 Operation

When an interrupt is generated, the corresponding bit is set in the interrupt pending register. The pending bits are ANDed with the interrupt mask register and then forwarded to the priority selector. Each interrupt can be assigned to one of two levels as programmed in the interrupt level register. Level 1 has higher priority than level 0. The interrupts are prioritised within each level, with interrupt 15 having the highest priority and interrupt 1 the lowest. The highest interrupt from level 1 will be forwarded to the IU - if no unmasked pending interrupt exists on level 1, then the highest unmasked interrupt from level 0 will be forwarded. When the IU acknowledges the interrupt, the corresponding pending bit will automatically be cleared.

Interrupt can also be forced by setting a bit in the interrupt force register. In this case, the IU acknowledgement will clear the force bit rather than the pending bit.

After reset, the interrupt mask register is set to all zeros while the remaining control registers are undefined.

Note that interrupt 15 cannot be maskable by the integer unit and should be used with care most operating system do safely handle this interrupt.

## 3.3.2.2 Interrupt assignment

Table 7 shows the assignment of interrupts.

TABLE 7. Interrupt assignments

| Interrupt | Source                      |  |

|-----------|-----------------------------|--|

| 15        | Parallel I/O [7]            |  |

| 14        | SpaceWire 1                 |  |

| 13        | SpaceWire 0                 |  |

|           | Parallel I/O [6]            |  |

| 12        | CAN interface               |  |

|           | Parallel I/O [5]            |  |

| 11        | DSU trace buffer            |  |

| 10        | Second interrupt controller |  |

|           | Parallel I/O [4]            |  |

| 9         | Timer 2                     |  |

TABLE 7. Interrupt assignments

| Interrupt | Source          |

|-----------|-----------------|

| 8         | Timer 1         |

| 7         | Parallel I/O[3] |

| 6         | Parallel I/O[2] |

| 5         | Parallel I/O[1] |

| 4         | Parallel I/O[0] |

| 3         | UART 1          |

| 2         | UART 2          |

| 1         | AHB error       |

## 3.3.2.3 Control registers

The operation of the interrupt controller is programmed through the following registers:

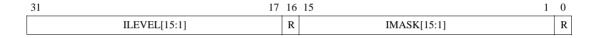

Figure 8. Interrupt mask and priority register

## Field Definitions:

[31:17]: Interrupt level (ILEVEL[15:1]) - indicates whether an interrupt belongs to priority level 1 (ILEVEL[n]=1) or level 0 (ILEVEL[n]=0).

[15:1]: Interrupt mask (IMASK[15:1]) - indicates whether an interrupt is masked (IMASK[n]=0) or enabled (IMASK[n]=1).

[16], [0]: Reserved. No effect when written to. Undefined when read.

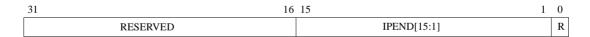

Figure 9. Interrupt pending register

## Field Definitions:

[15:1]: Interrupt pending (IPEND[15:1]) - indicates whether an interrupt is pending (IPEND[n]=1). [31:16], [0]: Reserved. No effect when written to. Undefined when read.

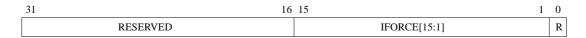

Figure 10. Interrupt force register

## Field Definitions:

[15:1]: Interrupt force (IFORCE[15:1]) - indicates whether an interrupt is being forced (IFORCE[n]=1). [31:16], [0]: Reserved. No effect when written to. Undefined when read.

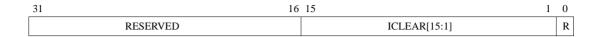

Figure 11. Interrupt clear register

#### Field Definitions:

[15:1]: Interrupt clear (ICLEAR[15:1]) - if written with a '1', will clear the corresponding bit(s) in the interrupt pending register. A read returns zero.

[31:16], [0]: Reserved. No effect when written to. Undefined when read.

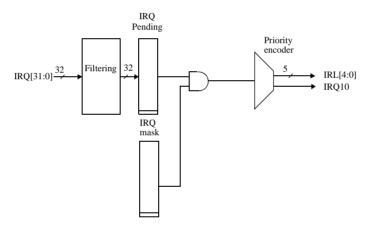

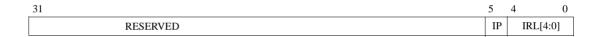

### 3.3.3 Secondary interrupt controller

The secondary interrupt controller is used add up to 32 additional interrupts, to be used by onchip units in system-on-chip designs. Figure 7 shows a block diagram of the interrupt controller.

Figure 12. Secondary interrupt controller block diagram

## 3.3.3.1 Operation

The incoming interrupt signals are filtered. The filtering condition is positive edge-triggered. When the condition is fulfilled, the corresponding bit is set in the interrupt pending register. The pending bits are ANDed with the interrupt mask register and then forwarded to the priority selector. If at least one unmasked pending interrupt exists, the interrupt output will be driven, generating interrupt 10 (by default). The highest unmasked pending interrupt can be read from the interrupt status register (see below).

Interrupts are not cleared automatically upon a taken interrupt - the interrupt handler must reset the pending bit by writing a '1' to the corresponding bit in the interrupt clear register. It must then also clear interrupt 10 in the primary interrupt controller. Testing of interrupts can be done by writing directly to the interrupt pending registers. Bits written with '1' will be set while bits written with '0' will keep their previous value.

After reset, the interrupt mask register is set to all zeros while the remaining control registers are undefined.

## 3.3.3.2 Control registers

The operation of the secondary interrupt controller is programmed through the following registers:

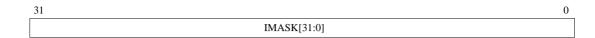

Figure 13. Secondary interrupt mask register

[31:0]: Interrupt mask - indicates whether an interrupt is masked (IMASK[n]=0) or enabled (IMASK[n]=1).

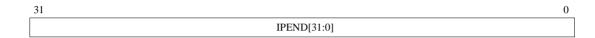

Figure 14. Secondary interrupt pending register

[31:0]: Interrupt pending - indicates whether an interrupt is pending (IPEND[n]=1).

Figure 15. Secondary interrupt status register

[4:0]: Interrupt request level - indicates the highest unmasked pending interrupt.

[5]: Interrupt pending - if set, then IRL is valid. If cleared, no unmasked interrupt is pending.

Figure 16. Secondary interrupt clear register

[31:0]: Interrupt clear - if written with a '1', will clear the corresponding bit(s) in the interrupt pending register.

# 3.3.3.3 Interrupt assignment

Table 8 shows the assignment of interrupts for the secondary interrupt controller.

TABLE 8. Secondary interrupt controller assignments

| Interrupt | Source          |                             |

|-----------|-----------------|-----------------------------|

| 31        | GPIO / Gpio[23] | 24-bit GPIO input interrupt |

| 30        | GPIO / Gpio[22] | 24-bit GPIO input interrupt |

| 29        | GPIO / Gpio[21] | 24-bit GPIO input interrupt |

| 28        | GPIO / Gpio[20] | 24-bit GPIO input interrupt |

TABLE 8. Secondary interrupt controller assignments

| Interrupt | Source                  |                                       |

|-----------|-------------------------|---------------------------------------|

| 27        | GPIO / Gpio[19]         | 24-bit GPIO input interrupt           |

| 26        | GPIO / Gpio[18]         | 24-bit GPIO input interrupt           |

| 25        | GPIO / Gpio[17]         | 24-bit GPIO input interrupt           |

| 24        | GPIO / Gpio[16]         | 24-bit GPIO input interrupt           |

| 23-20     | -                       | Unused                                |

| 19        | CAN/RxSync              | Synchronization message received      |

| 18        | CAN/TxSync              | Synchronization message transmitted   |

| 17        | CAN/IRQ                 | Common output from interrupt handler  |

| 16        | SpaceWire 1/ Tick       | Synchronization received              |

| 15        | SpaceWire 1 / Interrupt | Common output from interrupt handler  |

| 14        | SpaceWire 0 / Tick      | Synchronization received              |

| 13        | SpaceWire 0 / Interrupt | Common output from interrupt handler  |

| 12        | FIFO/RxParity           | Parity error during reception         |

| 11        | FIFO/RxError            | AHB access error during reception     |

| 10        | FIFO/RxFull             | Circular reception buffer full        |

| 9         | FIFO/RxIrq              | Successful reception of data block    |

| 8         | FIFO/TxError            | AHB access error during transmission  |

| 7         | FIFO/TxEmpty            | Circular transmission buffer empty    |

| 6         | FIFO/TxIrq              | Successful transmission of data block |

| 5         | ADC/DAC                 | DAC conversion ready                  |

| 4         | ADC/DAC                 | ADC conversion ready                  |

| 3         | 32-Bit Timer/Timer 2    | Timer expired                         |

| 2         | 32-Bit Timer/Timer 1    | Timer expired                         |

| 1         | GPIO/PULSE              | Pulse command completed               |

| 0         | -                       | Unused                                |

Note: Interrupt 17, 15 and 13 are available in primary interrupt controller and should therefore be used restrictively in the secondary interrupt controller. The secondary interrupt controller uses edge detection, whereas the aforementioned interrupt sources use level. The interrupt handling software must thus ensure that the sources for the aforementioned interrupts do not have an additional pending interrupt when clearing the corresponding bit in the pending interrupt register in the secondary interrupt controller. This limitation does not exist for the primary interrupt controller.

Note: Interrupts 31 down to 24 are connected to the inputs of the 24-bit General Purpose Input Output interface. The secondary interrupt controller uses edge detection. The 24-bit General Purpose Input Output interface must therefore only be programmed for edge detection, not for level, to ensure that multiple interrupts can be detected.

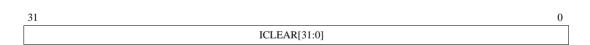

#### 3.3.4 Timer unit

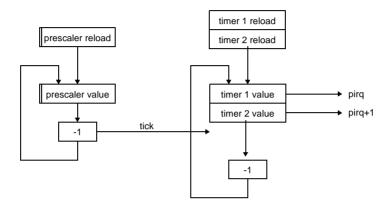

The timer unit implements two 32-bit timers, one 32-bit watchdog and one 10-bit shared prescaler (figure 17).

Figure 17. Timer unit block diagram

## 3.3.4.1 Operation

The prescaler is clocked by the system clock and decremented on each clock cycle. When the prescaler underflows, it is reloaded from the prescaler reload register and a timer tick is generated for the two timers and watchdog. The effective division rate is therefore equal to prescaler reload register value + 1.

The operation of the timers is controlled through the timer control register. A timer is enabled by setting the enable bit in the control register. The timer value is then decremented each time the prescaler generates a timer tick. When a timer underflows, it will automatically be reloaded with the value of the timer reload register if the reload bit is set, otherwise it will stop (at 0xffffffff) and reset the enable bit. An interrupt will be generated after each underflow.

The timer can be reloaded with the value in the reload register at any time by writing a 'one' to the load bit in the control register.

The watchdog operates similar to the timers, with the difference that it is always enabled and upon underflow asserts the external signal WDOG. This signal can be used to generate a system reset

To minimise complexity, the two timers and watchdog share the same decrementer. This means that the minimum allowed prescaler division factor is 4 (reload register = 3).

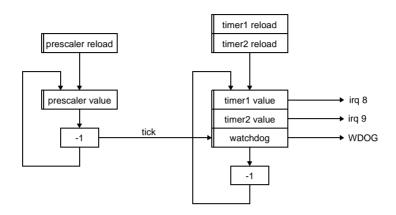

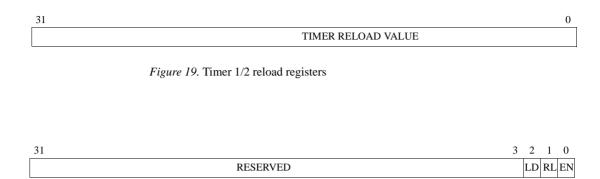

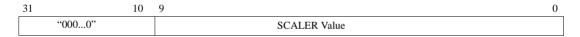

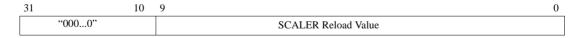

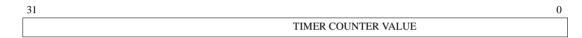

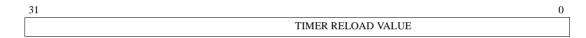

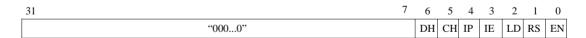

## 3.3.4.2 Registers

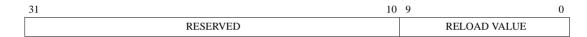

Figures 18 to 22 shows the layout of the timer unit registers.

Figure 18. Timer 1/2 and Watchdog counter registers

Figure 20. Timer 1/2 control registers

- [2]: Load counter (LD) when written with 'one', will load the timer reload register into the timer counter register. Always reads as a 'zero'.

- [1]: Reload counter (RL) if RL is set, then the counter will automatically be reloaded with the reload value after each underflow.

- [0]: Enable (EN) enables the timer when set.

- [31:3]: Reserved. No effect when written to. Undefined when read.

Figure 21. Prescaler reload register

[31:10]: Reserved. No effect when written to. Undefined when read.

Figure 22. Prescaler counter register

[31:10]: Reserved. No effect when written to. Undefined when read.

#### **3.3.5 UARTs**

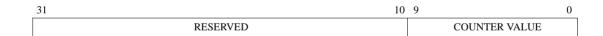

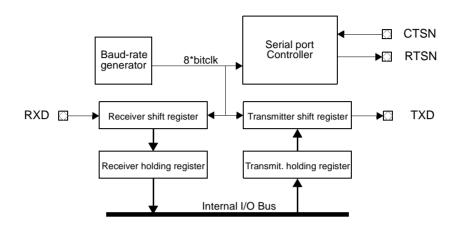

Two identical UARTs are provided for serial communications. The UARTs support data frames with 8 data bits, one optional parity bit and one stop bit. To generate the bit-rate, each UART has a programmable 12-bits clock divider. Hardware flow-control is supported through the RTSN/CTSN hand-shake signals. Figure 23 shows a block diagram of a UART.

Figure 23. UART block diagram

## 3.3.5.1 Transmitter operation

The transmitter is enabled through the TE bit in the UART control register. When ready to transmit, data is transferred from the transmitter holding register to the transmitter shift register and converted to a serial stream on the transmitter serial output pin (TXD). It automatically sends a start bit followed by eight data bits, an optional parity bit, and one stop bits (figure 24). The least significant bit of the data is sent first

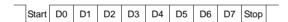

Figure 24. UART data frames

Following the transmission of the stop bit, if a new character is not available in the transmitter holding register, the transmitter serial data output remains high and the transmitter shift register empty bit (TSRE) will be set in the UART control register. Transmission resumes and the TSRE is cleared when a new character is loaded in the transmitter holding register. If the transmitter is disabled, it will continue operating until the character currently being transmitted is completely sent out. The transmitter holding register cannot be loaded when the transmitter is disabled.

If flow control is enabled, the CTSN input must be low in order for the character to be transmitted. If it is deasserted in the middle of a transmission, the character in the shift register is transmitted and the transmitter serial output then remains inactive until CTSN is asserted again. If the CTSN is connected to a receivers RTSN, overrun can effectively be prevented.

#### 3.3.5.2 Receiver operation

The receiver is enabled for data reception through the receiver enable (RE) bit in the UART control register. The receiver looks for a high to low transition of a start bit on the receiver serial data input pin. If a transition is detected, the state of the serial input is sampled a half bit clocks later. If the serial input is sampled high the start bit is invalid and the search for a valid start bit continues. If the serial input is still low, a valid start bit is assumed and the receiver continues to sample the serial input at one bit time intervals (at the theoretical centre of the bit) until the proper number of data bits and the parity bit have been assembled and one stop bit has been detected. The serial input is shifted through an 8-bit shift register where all bits have to have the same value before the new value is taken into account, effectively forming a low-pass filter with a cut-off frequency of 1/8 system clock.

During reception, the least significant bit is received first into the receiver shift register (RSR). The data is then transferred to the receiver holding register (RHR) and the data ready (DR) bit is set in the UART status register. If RHR was not empty when a character was received, the transfer from RSR, and setting of DR, will not occur until RHR has been emptied by a read access to the UART data register. The parity, framing, break and overrun error bits are set at the received character boundary, at the same time as the data ready (DR) bit would have been set, but no new character is transferred to RHR.

The parity error (PE) bit is set or cleared for each received character. The parity error (PE) bit is also cleared when a '0' is written to it via the UART status register.

The break (BR) bit is set when all-zero bits have been received and the stop bit is zero. The break (BR) bit is not cleared when a new character has been received, it is cleared when a '0' is written to it via the UART status register.

The framing error (FE) bit is set when any non-zero bits have been received and the stop bit is zero. The framing error (FE) bit is not cleared when a new character has been received, it is cleared when a '0' is written to it via the UART status register.

If both receiver holding (RHR) and shift (RSR) registers contain an un-read character when a new start bit is detected, then the character held in the receiver shift register (RSR) will be lost and the overrun (OV) bit will be set in the UART status register. The overflow bit (OV) is not cleared when a new character has been received, it is cleared when a '0' is written to it via the UART status register.

If flow control is enabled, then the RTSN will be negated (high) when a valid start bit is detected and the receiver holding register contains an un-read character. When the holding register is read, the RTSN will automatically be reasserted again.

### 3.3.5.3 Baud-rate generation

Each UART contains a 12-bit down-counting scaler to generate the desired baud-rate. The scaler is clocked by the system clock and generates a UART tick each time it underflows. The scaler is reloaded with the value of the UART scaler reload register after each underflow. The resulting UART tick frequency should be 8 times the desired baud-rate. If the EC bit is set, the scaler will be clocked by the LeonPio[3] input rather than the system clock. In this case, the frequency of LeonPio[3] must be less than half the frequency of the system clock.

## 3.3.5.4 Loop back mode

If the LB bit in the UART control register is set, the UART will be in loop back mode. In this mode, the transmitter output is internally connected to the receiver input and the RTSN is connected to the CTSN. It is then possible to perform loop back tests to verify operation of receiver, transmitter and associated software routines. In this mode, the outputs remain in the inactive state, in order to avoid sending out data.

### 3.3.5.5 Interrupt generation

The UART will generate an interrupt under the following conditions: when the transmitter is enabled, the transmitter interrupt is enabled and the transmitter holding register moves from full to empty; when the receiver is enabled, the receiver interrupt is enabled and the receiver holding register moves from empty to full; when the receiver is enabled, the receiver interrupt is enabled and a character with either parity, framing, break or overrun error is received.

## 3.3.5.6 UART registers

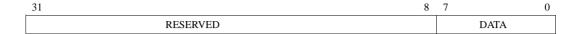

Figure 25. UART data register

[7:0]: Receiver holding register (read access)

[7:0]: Transmitter holding register (write access)

[31:8]: Reserved. No effect when written to. Undefined when read.

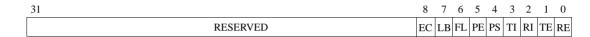

Figure 26. UART control register

- 0: Receiver enable (RE) if set, enables the receiver.

- 1: Transmitter enable (TE) if set, enables the transmitter.

- 2: Receiver interrupt enable (RI) if set, enables generation of receiver interrupt.

- 3: Transmitter interrupt enable (TI) if set, enables generation of transmitter interrupt.

- 4: Parity select (PS) selects parity polarity (0 = even parity, 1 = odd parity)

- 5: Parity enable (PE) if set, enables parity generation and checking.

- 6: Flow control (FL) if set, enables flow control using CTS/RTS.

- 7: Loop back (LB) if set, loop back mode will be enabled.

- 8: External Clock (EC) if set, the UART scaler will be clocked by LeonPio[3]

- [31:9]: Reserved. No effect when written to. Undefined when read.

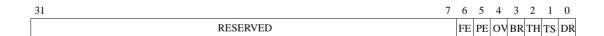

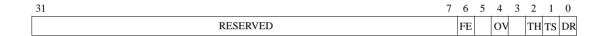

Figure 27. UART status register

- 0: Data ready (DR) indicates that new data is available in the receiver holding register.

- 1: Transmitter shift register empty (TS) indicates that the transmitter shift register is empty.

- 2: Transmitter hold register empty (TH) indicates that the transmitter hold register is empty.

- 3: Break received (BR) indicates that a BREAK has been received.

- 4: Overrun (OV) indicates that one or more character have been lost due to overrun.

- 5: Parity error (PE) indicates that a parity error was detected.

- 6: Framing error (FE) indicates that a framing error was detected.

- [31:7]: Reserved. No effect when written to. Undefined when read.

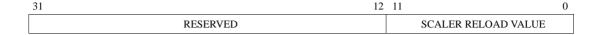

Figure 28. UART scaler reload register

[31:12]: Reserved. No effect when written to. Undefined when read.

## 3.3.6 Parallel I/O port

A partially bit-wise programmable 32-bit I/O port is provided on-chip. The port is split in two parts - the lower 16-bits are accessible via the LeonPio[15:0] signal while the upper 16-bits uses D[15:0] and can only be used when all areas (rom, ram and I/O) of the memory bus are in 8-bit mode (See "8-bit PROM and SRAM access" on page 35.).

The lower 16 bits of the I/O port can be individually programmed as output or input, while the high 16 bits of the I/O port only be configures as outputs or inputs on byte basis. Two registers are associated with the operation of the I/O port; the combined I/O input/output register, and I/O direction register. When read, the input/output register will return the current value of the I/O port; when written, the value will be driven on the port signals (if enabled as output). The direction register defines the direction for each individual port bit (0=input, 1=output).

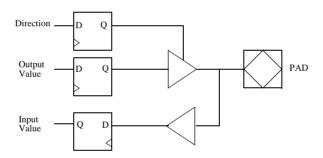

Figure 29. I/O port block diagram

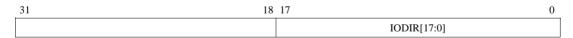

Figure 30. I/O port direction register

IODIR*n* - I/O port direction. The value of IODIR[15:0] defines the direction of I/O ports 15 - 0. If bit *n* is set the corresponding I/O port becomes an output, otherwise it is an input. IODIR[16] controls D[15:8] while IODIR[17] controls D[7:0]

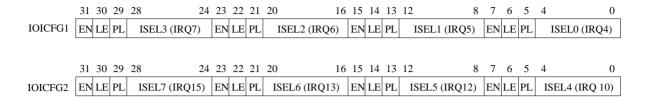

The I/O ports can also be used as interrupt inputs from external devices. A total of eight interrupts can be generated, corresponding to interrupt levels 4, 5, 6, 7, 10, 12, 13, and 15. The I/O port interrupt configuration register 1 and 2 define which port should generate each interrupt and how it should be filtered.

[31:18]: Reserved. No effect when written to. Undefined when read.

Figure 31. I/O port interrupt configuration register 1 & 2

- ISEL*n* I/O port select. The value of this field defines which I/O port (0 31) should generate parallel I/O port interrupt *n*.

- PL Polarity. If set, the corresponding interrupt will be active high (or edge-triggered on positive edge). Otherwise, it will be active low (or edge-triggered on negative edge).

- LE Level/edge triggered. If set, the interrupt will be edge-triggered, otherwise level sensitive.

- EN Enable. If set, the corresponding interrupt will be enabled, otherwise it will be masked.

To save pins, I/O pins are shared with other functions according to the table below:

TABLE 9. UART/IO port usage

| I/O port     | Function   | Туре   | Description                     | Enabling condition         |

|--------------|------------|--------|---------------------------------|----------------------------|

| LeonPio[15]  | TXD1       | Output | UART1 transmitter data          | UART1 transmitter enabled  |

| LeonPio[14]  | RXD1       | Input  | UART1 receiver data             | -                          |

| LeonPio[13]  | RTS1       | Output | UART1 request-to-send           | UART1 flow-control enabled |

| LeonPio[12]  | CTS1       | Input  | UART1 clear-to-send             | -                          |

| LeonPio[11]  | TXD2       | Output | UART2 transmitter data          | UART2 transmitter enabled  |

| LeonPio[10]  | RXD2       | Input  | UART2 receiver data             | -                          |

| LeonPio[9]   | RTS2       | Output | UART2 request-to-send           | UART2 flow-control enabled |

| LeonPio[8]   | CTS2       | Input  | UART2 clear-to-send             | -                          |

| LeonPio[3]   | UART clock | Input  | Use as alternative UART clock   | -                          |

| LeonPio[2]   | Prom EDAC  | Input  | Defines prom edac at boot time  | -                          |

| LeonPio[1:0] | Prom width | Input  | Defines prom width at boot time | -                          |

#### 3.3.7 LEON configuration register

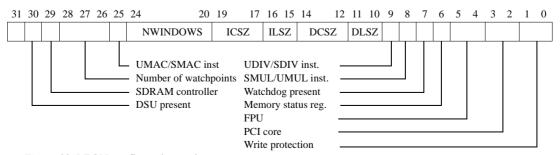

Since LEON is extensively configurable, the LEON configuration register (read-only) is used to indicate which options were enabled in the design. For each option present, the corresponding register bit is hardwired to '1'. Figure 32 shows the layout of the register.

Figure 32. LEON configuration register

[31]: Reserved. No effect when written to. Undefined when read.

- [30]: Debug support unit (0=disabled, 1=present)

- [29]: SDRAM controller present (0=disabled, 1=present)

- [28:26]: Number of implemented watchpoints (0 4)

- [25]: UMAC/SMAC instruction implemented

- [24:20]: Number of register windows. The implemented number of SPARC register windows -1.

- [19:17]: Instruction cache size. The size (in kbytes) of the instruction cache. Cache size =  $2^{ICSZ}$ .

- [16:15]: Instruction cache line size. The line size (in 32-bit words) of each line. Line size  $= 2^{ILSZ}$ .

- [14:12]: Data cache size. The size (in kbytes) of the data cache. Cache size =  $2^{DCSZ}$ .

- [11:10]: Data cache line size. The line size (in 32-bit words) of each line. Line size =  $2^{DLSZ}$ .

- [9]: UDIV/SDIV instruction implemented

- [8]: UMUL/SMUL instruction implemented

- [7]: Watchdog implemented

- [6]: Memory status and failing address register present

- [5:4]: FPU type (00 = none, 01=Meiko)

- [3:2]: PCI core type (00=none, 01=InSilicon, 10=ESA, 11=other)

- [1:0]: Write protection type (00=none, 01=standard)

#### 3.3.8 Power-down

The processor can be powered-down by writing (an arbitrary) value to the power-down register. Power-down mode will be entered on the next load or store instruction. To enter power-down mode immediately, a store to the power-down register should be performed followed by a 'dummy' load. During power-down mode, the integer unit will effectively be halted. The power-down mode will be terminated (and the integer unit re-enabled) when an unmasked interrupt with higher level than the current processor interrupt level (PIL) becomes pending. All other functions and peripherals operate as nominal during the power-down mode. A suitable power-down routine could be:

```

struct pwd_reg_type { volatile int pwd; };

power_down()

{

struct pwd_reg_type *lreg = (struct pwd_reg_type *) 0x80000018;

while (1) lreg->pwd = lreg->pwd;

}

In assembly, a suitable sequence could be:

power_down:

set    0x80000000, %13

st    %g0, [%13 + 0x18]

ba    power_down

ld    [%13 + 0x18], %g0

```

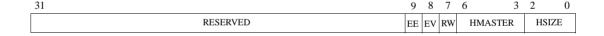

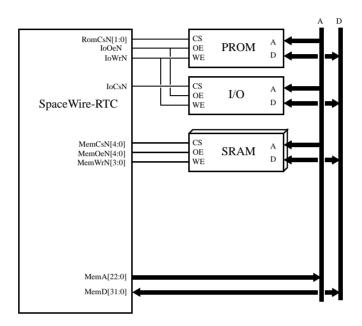

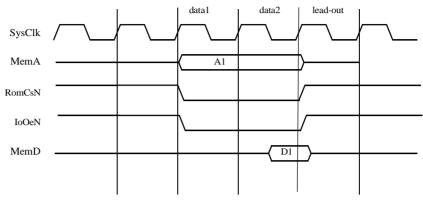

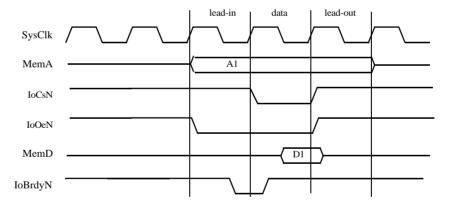

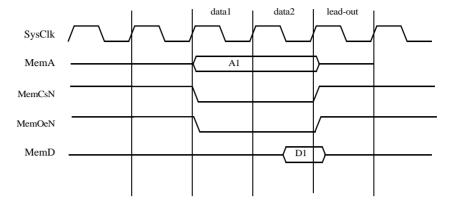

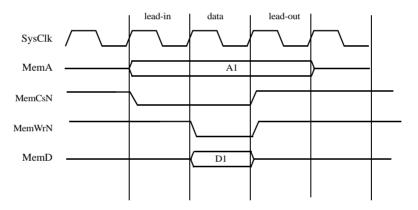

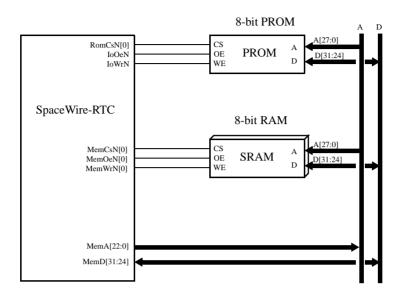

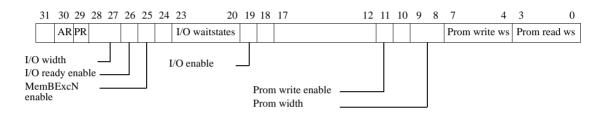

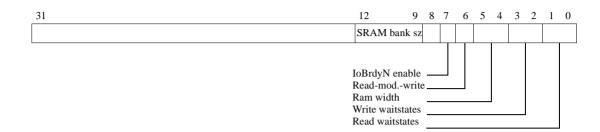

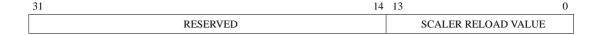

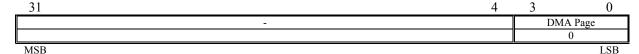

## 3.3.9 AHB status register